一种模拟电路参数型故障诊断新方法

周启忠,谢永乐,毕东杰,李西峰

一种模拟电路参数型故障诊断新方法

周启忠1,2,谢永乐1,毕东杰1,李西峰1

(1. 电子科技大学自动化工程学院 成都 611731; 2. 宜宾学院物理与电子工程学院 四川宜宾 644000)

模拟电路参数型故障诊断一直是电路与系统无法回避的难题。该文基于被测电路主输出电压信号的时间序列值,建立了一种基于本征值和相位差的模拟电路参数型故障诊断模型。该模型利用故障电路的电压输出时间序列值获取电路的故障相位偏移信息,同时,该模型把电压时间序列变换成一个方阵,并求取该方阵的最大本征值。将故障相位偏移信息和故障最大本征值与通过前期仿真获得的每种器件相对应的无故障最大相位偏移和无故障最大本征值的变化趋势进行比较,实现故障定位和参数辨识。实测实验结果表明:该方法具有定位准确、计算效率高,所需测试点少、参数辨识精度高,易于工程实施等优点。

模拟电路; 故障诊断; 参数辨识; 参数故障

近年来,模拟电路故障诊断的重要性和紧迫性日益突出。由于模拟电路具有测试节点有限、系统状态不稳定、故障模型缺乏、容差影响大等固有难点,使得模拟电路故障诊断技术明显落后于数字电路,亟待提出新的、高效的技术手段和方法。

随着工程技术领域对系统可靠性要求的提高,电路系统不仅要求故障诊断方法能够进行故障检测和定位,而且对故障参数辨识提出了进一步要求。如在电路系统剩余寿命估计、电路故障辨识、元件失效机理分析等环节,需要对故障元件进行参数辨识以提供更多更具体的故障信息。相比于故障检测与定位,故障参数的辨识要困难许多。

目前,成熟的故障参数辨识方法鲜有报道,但在故障检测与定位上有许多典型的方法[2-14]。如子带滤波方法可以检测模拟电路参数故障,但是该方法难于进行故障定位[2];基于灵敏度计算的模糊分析方法可实现线性模拟电路的参数型故障诊断,但该方法对处理故障诊断中容差特性效果欠佳[3];神经网络法自适应能力和容错能力强的优点[4],但对故障特征的提取要求高,很容易收敛于局部极小点。小波变换具有良好的时频局部化和多分辨分析的性质[5],但其计算比较复杂。其他改进方法能检测和定位故障[6-14],但不能辨识故障参数。综上分析,有必要寻求新技术途径来实现对模拟电路的故障定位和故障参数辨识。本文针对现有技术的不足,提出一种基于相位偏移和响应矩阵最大本征值的模拟电路故障诊断和故障参数辨识方法。因为电路诊断中的故障主要为单故障,所以本文主要考虑单故障情况。

1 理论原理

周期函数可以表示为三角函数的叠加,为了便于理解,本文以输入激励和输出响应都为正弦信号的线性模拟电路为例,介绍所提出的方法。

在模拟电路的同一测试点上,可诊断故障集的不同故障对应着不同的输出电压幅度和相位,因此从相位和幅度两方面综合考虑进行故障诊断和参数辨识,在理论上是可行的。相比只用幅度信号进行观测,结合相位信息和幅度信息的观测更全面,故障覆盖率和参数辨识精度更高。采用正弦激励信号的上升沿触发采样,以同步采样起始时间,这样,采样序列既体现输出信号幅度的变化,又包含输出响应的相位信息。利用Matlab对故障采样序列和无故障采样序列分别进行曲线拟合,可以获得故障相移信息和无故障相移信息,二者相减可得相位偏移。该相位偏移可作为故障特征量。从线性代数的角度分析表明使用被测电路响应矩阵的最大本征值表征响应幅度的变化也是正确可靠的。

(2)

矩阵理论中的Rouché’s理论和Ostrowski定理[16]表明,矩阵的本征值是矩阵元素的连续函数,盖尔圆盘定理给出了矩阵本征值扰动的上界。即对,和盖尔尔圆半径,,有:

(4)

模拟电路的器件参数有无穷多个状态,不同器件的参数大小和单位也不同,因此很难建立器件参数辨识模型。本文提出的方法首先将要诊断的器件参数进行归一化处理,使得每个器件的标称值都是1。这样就能把归一化器件参数、响应相位偏移和最大本征值统一到一个坐标下建立诊断和辨识模型。

由于模拟电路的器件参数是连续变化的,在理论上有无穷多个响应状态,而且每个响应状态对应一组最大本征值和相位。如果直接用最大本征值和相位来进行故障定位和参数辨识,就需要进行大量的计算和比较才能保证诊断精度,这将增加诊断的时间开销和测试成本。为了降低计算的复杂性,本文利用盖尔圆盘定理以保证每个器件参数变化时对应的最大本征值在一定界限内跟着变化的特点,只对每个可能的故障器件的几个故障参数状态和一个无故障状态进行测前仿真,对仿真结果进行计算获得每个可能故障的器件的参数、响应矩阵最大本征值和相位偏移之间的关系曲线函数,建立参数辨识和故障定位模型。这种方法不仅理论严密,而且在工程实施上具有可行性。

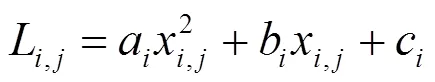

对第个器件的第个故障状态对应的输出序列进行正弦拟合得到相对相位,无故障状态对应的相对相位用表示,则相位偏移为:

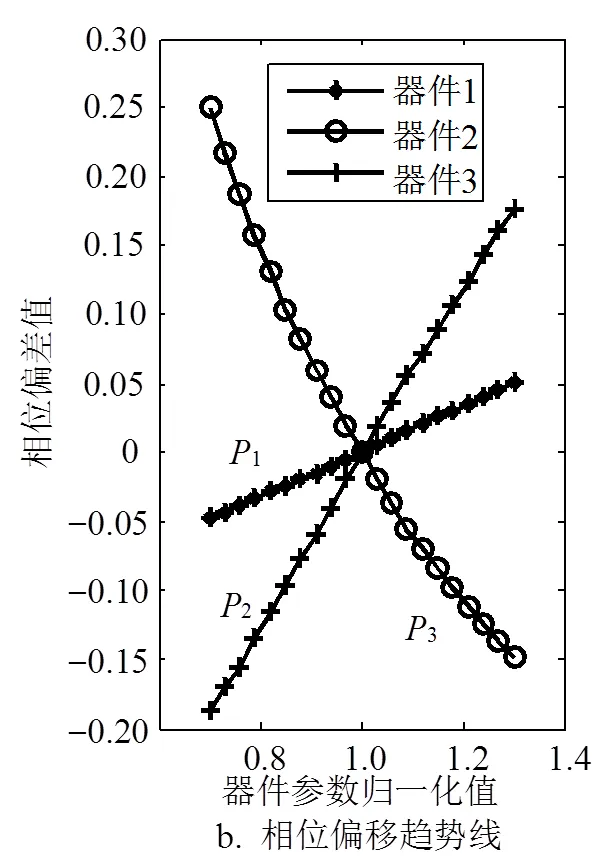

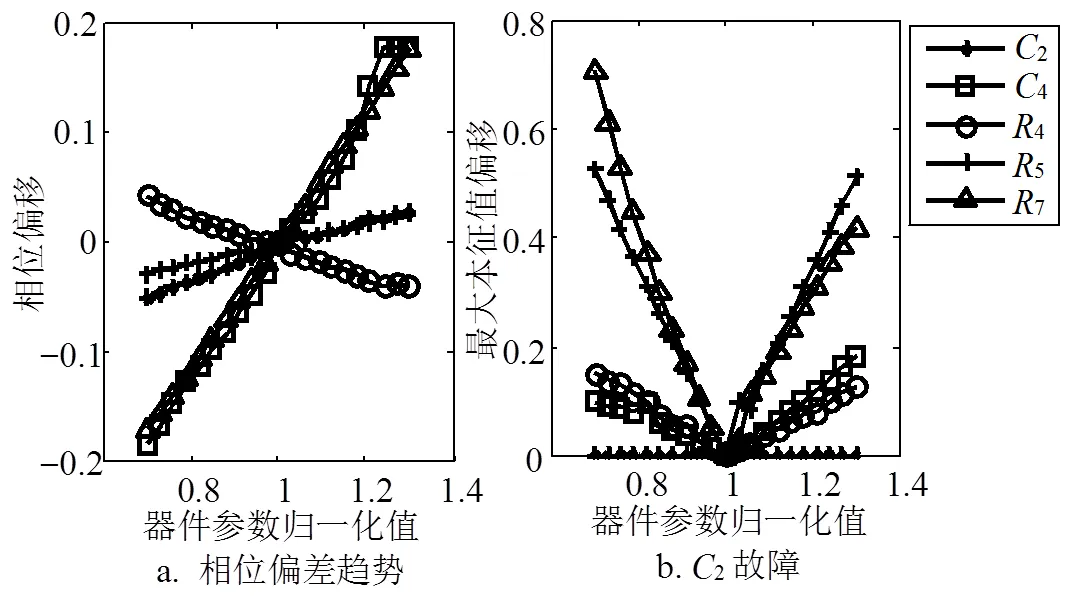

图1 最大本征值和相位差变化趋势曲线

图1显示了一个电路3个器件参数变化时的最大本征值趋势线和相位偏移趋势线。最大本征值趋势线和相位偏移变化线、和、和分别对应器件1、2和3。横坐标是器件归一化值,纵坐标分别表示最大本征值和相对相位差的大小。从图1可以看出,第个器件的最大本征值和相位偏移随器件参数变化而变化的趋势曲线可以用式(6)和式(7)分别表示为:

(7)

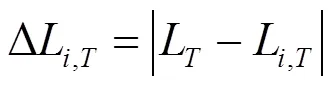

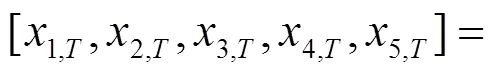

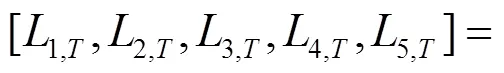

诊断故障时,首先用和仿真相同的激励信号测试故障响应,正弦拟合第次故障测试序列得到相位,与仿真的无故障状态相位相减得到相对相差。把第次故障测试序列的前25个元素组成一个5阶方阵,计算得到最大本征值。然后依次假设每个要诊断的器件分别发生故障,求出器件参数值。因和只对应电路的一个参数状态,所以可以按的顺序,将代替式(7)中的,根据、和求得每一个器件故障时中的一个器件参数,将作为代入式(6),得到中与对应的,计算出和的绝对误差为:

2 诊断过程

本文方法的诊断流程如图2所示,分7个步骤。

图2 诊断流程图

1) 把需诊断的个器件从1~编号,进行测前仿真,计算式(6)和式(7)的系数、、、、和及标称值状态的相位。2) 测试电路,对第次测试结果序列正弦拟合得相对相位,由算出相位偏移。把测试序列的前25个值组成5阶方阵,计算出最大本征值。3)代替代入式(7),算出用表示。4)代替代入式(6),算出,用表示。5) 把和代入式(8),算出。6) 冒泡法以为变量找出中的最小元素。7) 判断步骤4)获得的中的元素是否超出第个器件的容差范围,如果超出,则编号为的器件有故障,故障参数为。否则,电路无故障。

3 实验结果

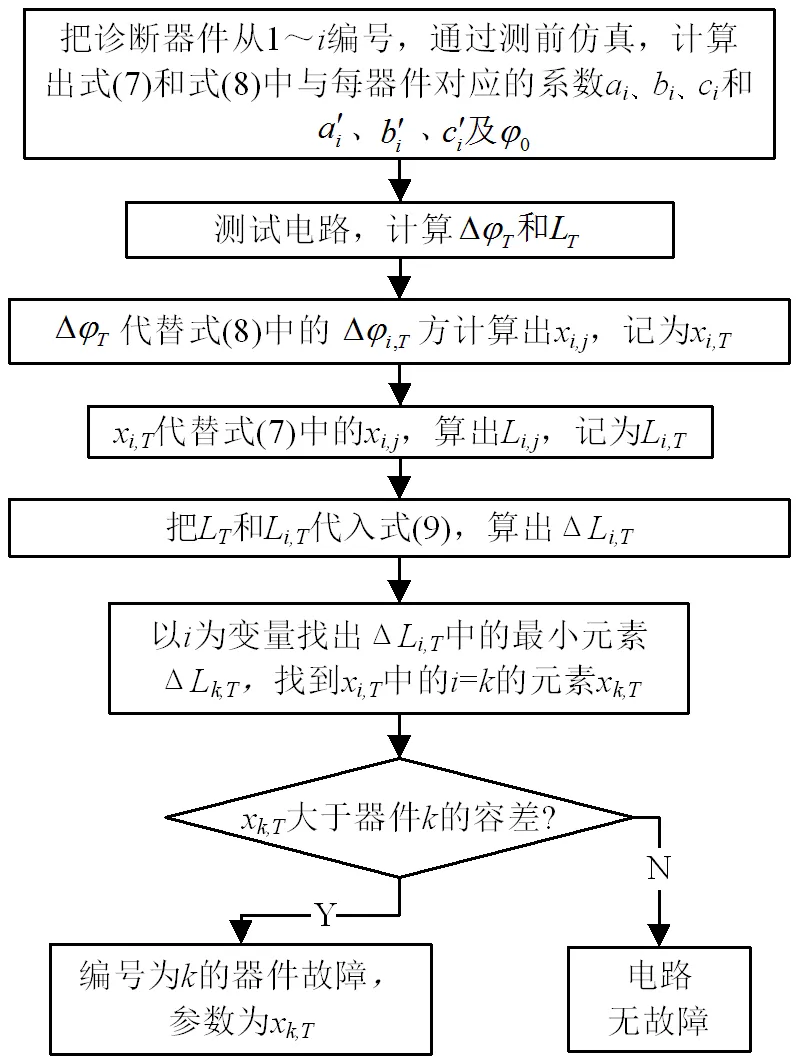

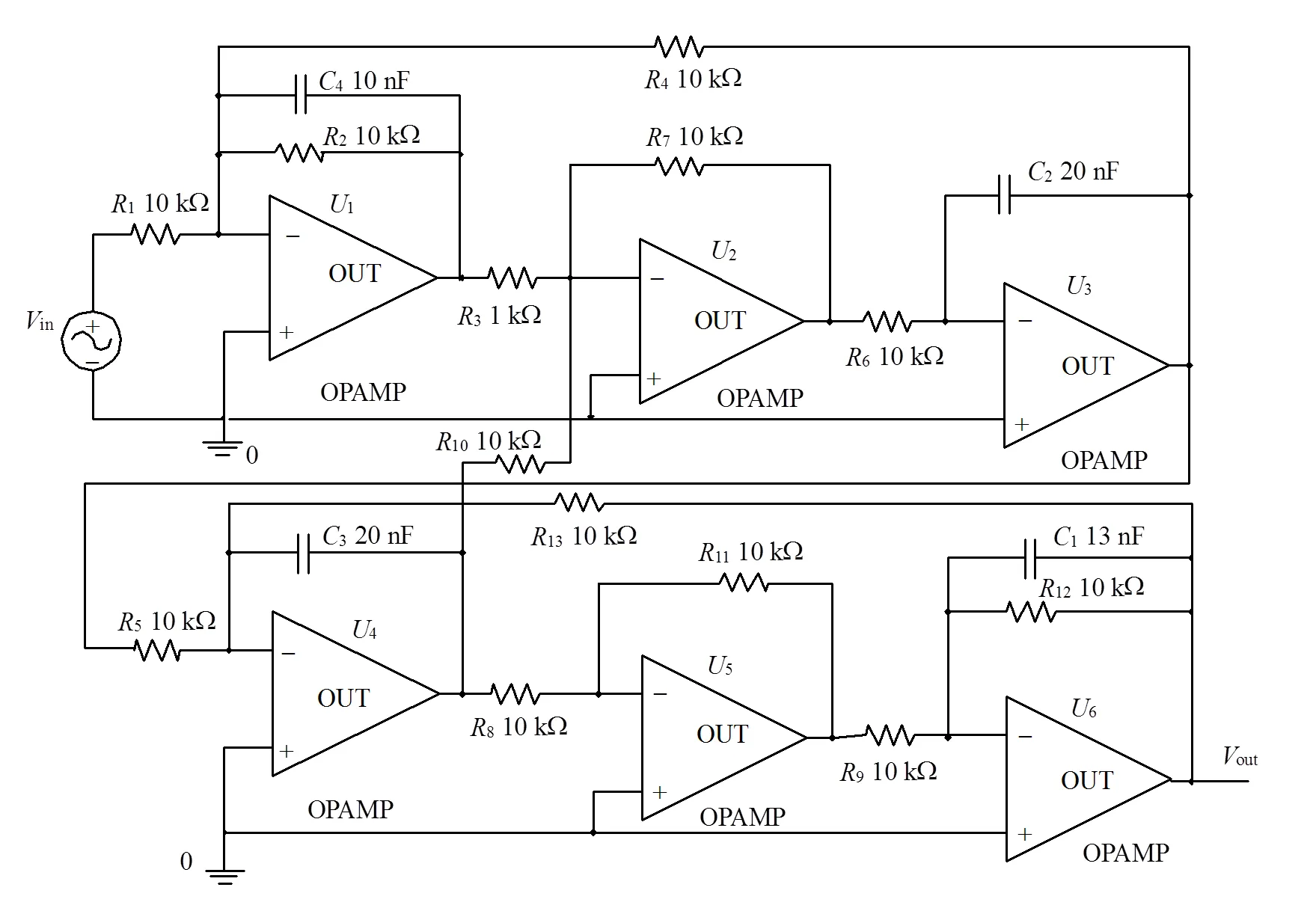

选取国际标准电路中的跳蛙低通滤波器电路作为实验电路以验证本文方法的有效性。测试激励根据被测电路特性来选取,这里采用信号源YB1603加入1 kHz,幅度为1 V的正弦激励信号。用NI公司USB-9201数据采集器(8通道;单通道最高采样率为800 kS/s;ADC分辨率为12 bits)对被测电路采样获得响应输出信号。数据处理部分采用CPU3.6 GHz和8 GB内存的PC机进行。由激励信号通过比较器获得的方波信号的上升沿触发采样模块。测试实际测试系统和实际电路如图3所示,所有器件的标称值和电路结构如图4所示。滤波器的截止频率是1.4 kHz。激励输入是一个频率为1 kHz幅度为6 V的正弦信号,选择被测电路电压输出端为测试输出端。设定无源器件的容差限是标称参数的±5%,2、4、4、5和7组成待诊断的故障集。

图3 实际测试系统和测试电路

图4 被测电路原理图

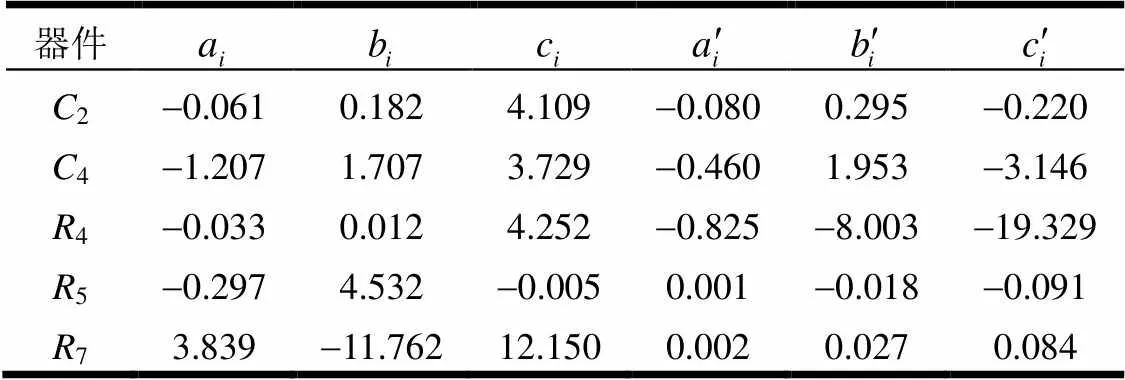

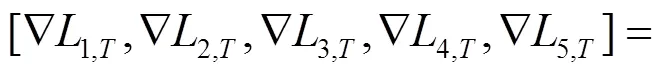

2、4、4、5和75个器件依次编号为1~5,首先对5个器件分别从它们标称值的70%到130%以10%的步进变化进行仿真,即每个器件仿真1个无故障状态和6个故障状态。根据仿真结果计算出每个器件的6个故障状态的响应矩阵最大本征值和对其无故障状态的6个相位偏移值后,分别对这6个值进行最小二乘拟合得到式(6)和式(7)描述的每个器件的相位偏移和最大本征值趋势曲线系数、、、、和如表1所示。

每个器件的容差限是5%,下面以器件2参数为标称值的109%为例,说明诊断过程。2参数为标称值的109%时,用图2所示的测试系统得到out端输出电压的25个采样值。用MATLAB工具计算出相位偏移值为=0.008 8,最大本征值=4.238 3。

表1 基相位偏移和最大本征值趋势曲线系数

(9)

(10)

(11)

不等式(12)表明辨识结果超过容差范围5%,所以得出:编号为1的器件2发生故障,其故障参数的归一化值为1.090 2,辨识误差为0.02%。

为了全面评估本文方法的效果,让5个器件分别从它们标称值的70%到130%以3%的步进变化,共105种参数状态。图5给出了仿真获得的相应偏移趋势曲线和5个器件105中故障参数的最大本征值偏差、、、、的大小情况。图5表明,编号为的器件发生故障时,对应的最小,这说明了本方法用最大本征值的偏移量作为故障定位判据,能得到正确的故障定位结果。

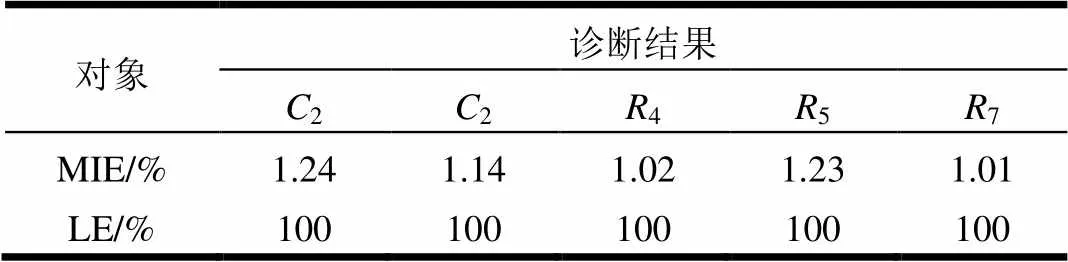

表2给出了105个参数状态的故障定位和故障参数辨识结果的总体情况。表中MIE表示每个器件对应的21个参数状态的参数辨识最大误差,LE表示故障定位准确率。实验结果证明,用相位和最大本征值进行模拟电路的故障定位和故障参数辨识,结果准确可靠,参数辨识精度高。

表2 故障定位准确率和参数辨识精度

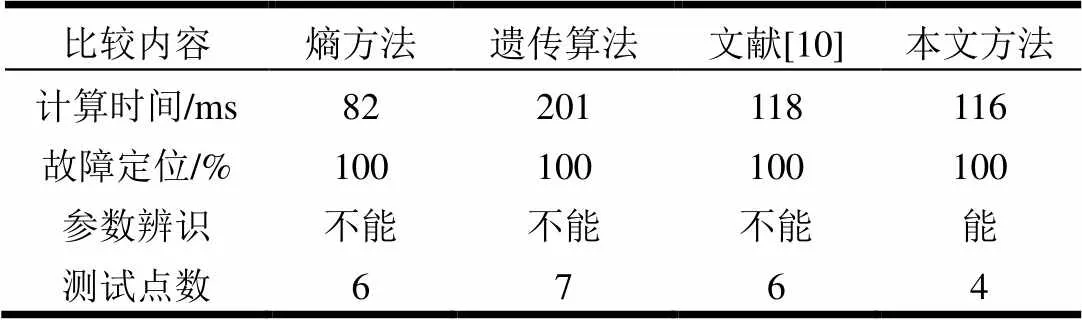

将本方法与3种模拟电路故障诊断方法对相同的电路进行故障诊断,得到如表3所示的结果。比较结果表明,本文提出的方法除了具有故障定位准确、计算效率高、所需测试点少的优势外,还具有将故障诊断与高精度的故障参数辨识一体化处理、易于工程实施的优点。

表3 故障定位准确率和参数辨识精度

4 结束语

本文提出了一种基于输出响应的相位变化和响应矩阵的最大本征值的模拟电路故障诊断和故障参数辨识法。实验结果表明该方法故障诊断的准确度和参数辨识的精度高。通过和其他方法比较,证明本文方法除了具有故障定位准确、计算效率高、所需测试点少的优势外,还具有将故障诊断与高精度的故障参数辨识一体化处理、易于工程实施的优点,满足大规模集成模拟电路测试的需求。

[1] LI F, WOO P Y. Fault detection for linear analog IC – the method of short-circuits admittance parameters[J]. IEEE Trans Circuits Syst I, Fundam Theory Appl, 2002, 49(1): 105-108.

[2] ROH J, ABRAHAM J A. Subband filtering for time and frequency analysis of mixed-signal circuit testing[J]. IEEE Trans Instrum Meas, 2004, 53(2): 602-611.

[3] TADEUSIEWICZ M, HALGAS S, KORZYBSKI M. An algorithm for soft fault diagnosis of linear and nonlinear circuits[J]. IEEE Trans Circuits Syst, 2002, 49(11): 1648-1653.

[4] AMINIAN F, AMINIAN M, COLLINS H W. Analog fault diagnosis of actual circuits using neural networks[J]. IEEE Transactions on Instrumentation and Measurement, 2002, 51(3): 544-550.

[5] AMINIAN M, AMINIAN F. Neural-network based analog-circuit fault diagnosis using wavelet transform as preprocessor[J]. IEEE Trans Circuits Syst, 2000, 47(2): 151-155.

[6] YANG Chen-lin, TIAN Shu-lin, LONG Bing, et al. Methods of handling the tolerance and test-point selection problem for analog-circuit fault diagnosis[J]. IEEE Trans Instrum Meas, 2011, 60(1): 176-185.

[7] ZHOU Long-fu, SHI Yi-bing. A novel method of single fault diagnosis in linear resistive circuit based on slope[C]// Proceeding of International Conference on Communications, Circuits and Systems. [S.l.]: IEEE, 2008: 1350-1353.

[8] LANG Rong-ling, XU Zhe-ping, GAO Fei. Data-driven fault diagnosis method for analog circuitsbased on robust competitive agglomeration[J]. Journal of Systems Engineering and Electronics, 2013, 24(4): 706-712.

[9] YANG Chen-lin, YANG Jing, LIU Zhen. Complex field fault modeling based optimal frequency selection in linear analog circuit fault diagnosis[J]. Transactions on Instrumentation and Measurement IEEE, 2014, 63(4): 813-825.

[10] TADEUSIEWICZ M, HALGAS S. A new approach to multiple soft fault diagnosis of analog BJT and CMOS circuits[J]. IEEE Transactions on Instrumentation and Measurement, 2015, 64(10): 2688-2695.

[11] YANG Chen-lin, TIAN Shu-lin, LIU Zhen. Fault modeling on complex plane and tolerance handling methods for analog circuits[J]. IEEE Transactions on Instrumentation and Measurement, 2013, 62(10): 2730-2738.

[12] VASAN S, SAI A, LONG Bing, et al. Diagnostics and prognostics method for analog electronic circuits[J]. IEEE Transactions on Industrial Electronics, 2013, 60(11): 5277-5291.

[13] LI Zhi-hua. A novel fault diagnostic method based on node-voltage vector ambiguity sets[J]. IEEE Transactions on Instrumentation and Measurement, 2014, 63(8): 1957-1965.

[14] WEI Li-xiang, LIU Zhi-jun, KERKMAN R J, et al. Identifying ground-fault locations: Using adjustable speed drives in high-resistance grounded systems[J]. Industry Applications Magazine, 2013, 19(2): 47-55.

[15] GRIFFITHS D J. Introduction to quantum mechanics[M]. [S.l.]: Addison Wesley, 2004: 96-98.

[16] WILKINSON J H. The algebraic eigenvalue problem[M]. Oxford: Clarendon, 1988: 62-64.

编 辑 漆 蓉

A Novel Method for Parametric Fault Diagnosis of Analog Circuits

ZHOU Qi-zhong1,2, XIE Yong-le1, BI Dong-jie1, and LI Xi-feng1

(1. School of Automation Engineering, University of Electronic Science and Technology of China Chengdu 611731; 2.School of Physics and Electronic Engineering, Yibin University Yibin Sichuan 644000)

This paper proposes a new model for parametric fault diagnosis in analog circuits, which is one of the most challenging problems in circuits and systems. This new model is based on the eigenvalue and phase difference from the time series of the output voltage of the circuit under test (CUT). The phase deviation information of the circuit is obtained via the sampling voltage time series. The sampling voltage time series is reorganized to be a matrix, and dominant eigenvalue of this matrix is obtained accordingly. Finally, by comparing the phase deviation and the dominant eigenvalue of the CUT with those of the fault free circuit in absolute relative error criteria, fault location and parameter identification can be accomplished. Experimental results show that the proposed method performs well in both fault location and parameter identification with very few access points and relatively low computation cost, moreover, fault location and parameter identification can be realized simultaneously, which makes it an effective and efficient method for fault diagnosis of analog circuits.

analog circuits; fault diagnosis; parameter identification; parametric faults

TN911.3

A

10.3969/j.issn.1001-0548.2017.02.012

2015-11-16;

2016-01-15

国家重点基础研究发展计划(2014CB744206);国家自然科学基金(61371049);四川省教育厅项目(09ZC081)

周启忠(1976-),男,博士生,主要从事模拟电路故障诊断方面的研究.