一种可实现STDP机制的CMOS突触和神经元电路设计

孙宏伟,陈 松,林福江

(中国科学技术大学 信息科学技术学院,安徽 合肥 230026)

一种可实现STDP机制的CMOS突触和神经元电路设计

孙宏伟,陈 松,林福江

(中国科学技术大学 信息科学技术学院,安徽 合肥 230026)

设计了一个高度集成的、高能效的CMOS突触和神经元电路。该突触电路可以实现基于脉冲时间依赖可塑性(Spike Timing Dependent Plasticity,STDP)的学习机制。通过这种机制可以模拟动作脉冲在真实突触中的传导特性并大规模集成为神经形态芯片。该电路采用低功耗的设计方法,晶体管偏置在亚阈值区,由低压电源(0.6 V)供电,采用0.18 μm 标准CMOS工艺实现。仿真结果表明,突触权值的变化为0.17 V~0.43 V;神经元电路可以真实模拟出神经元放电的多种模式,如RS(Regular Spike)模式、LTS(Low-Threshold Spike)模式、CH(Chattering)模式和IB(Intrinsic Bursting)模式等,电路在产生动作电位时每个脉冲平均仅消耗约0.6 pJ的能量。

神经元;突触;神经形态;高效

Abstract: An area-efficient and energy-efficient biophysical neuron and synapse CMOS circuit is presented. The proposed biologically inspired synapse circuit can perform the Spike Timing Dependent Plasticity (STDP) learning mechanism to imitate the generation and transmission properties of the realistic synapse and can be integrated in neuromorphic chips. The proposed circuit was biased in sub-threshold region and powered by a low voltage (0.6 V) supply, which is in line with the low power design principle. The circuit was implemented in 0.18 μm standard CMOS process. From the simulation results, the weight of the synapse varies from 0.17 V to 0.43 V. Besides, the bio-mimic neuron circuit can generate the burst behaviors of different patterns such as Regular Spikes (RS), Low-Threshold Spikes (LTS), Chattering (CH), and Intrinsic Bursting (IB). The action potential produced by the employed silicon neuron is energy-efficient and the average energy consumption is about 0.6 pJ per spike.

Key words:silicon neuron; synapse; neuromorphic; energy-efficient

0 引言

相比传统冯诺依曼架构的计算机,人类大脑具有更强的联想记忆和形象思维能力,在解决函数逼近、复杂分类和聚类等复杂问题上比现有计算机具有更大的潜力。而且相比计算机,大脑体积更小,功耗更低。因此,通过人工智能网络实现模拟人脑智能是最近一段时间来的热点[1]。神经网络由大量神经元组成,虽然单个神经元结构和行为简单,但通过一定的学习规则却能呈现出丰富的网络处理功能。因此可集成度对于神经形态模拟电路来说是关键指标,神经电路单元的面积越小、功耗越低,意味着芯片上就可以集成越多的模拟神经元和突触。因此设计面积小、功耗低的模拟神经单元电路是构建模拟神经形态VLSI的重要前提,也是一个挑战。

1 神经形态电路基本原理

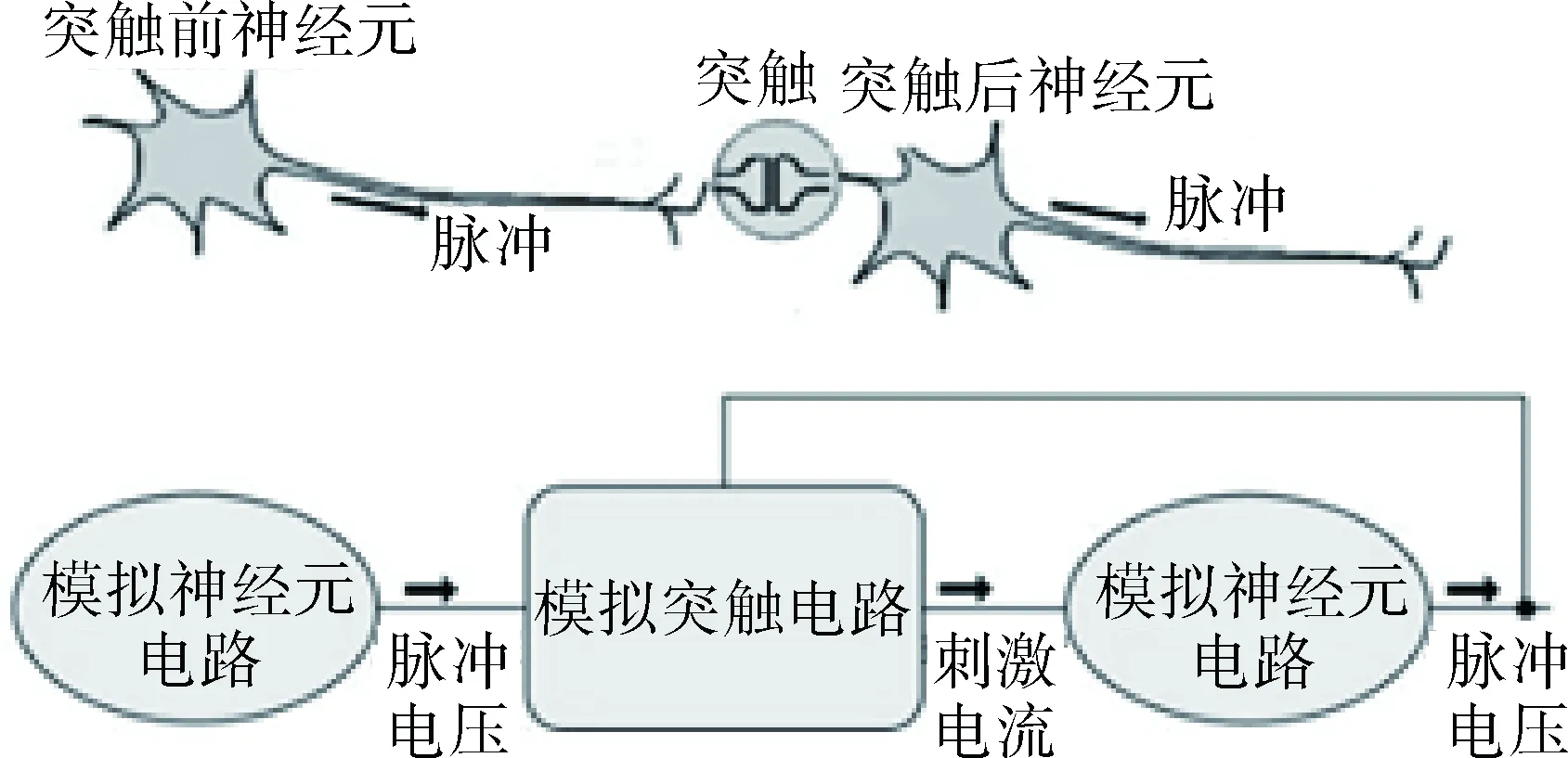

在现实的生物神经系统中,神经元之间各种相互作用是通过突触来实现的。图1是神经元和突触的生物模型以及简化后的电路模型。在电路设计中也采用类似的结构,包括模拟突触电路和模拟神经元电路,如图1所示,脉冲电压代表突触前神经元和突触后神经元的膜电位,两个膜电位同时流入到模拟突触中,经过突触电路处理后,输出的电流可以反映两个神经元之间的关系,该电流重新刺激突触后神经元影响突触后神经元的放电特性。

该突触电路可以实现STDP学习机制。在STDP机制中,突触权值是反映突触的传递效能的物理量,突触的传递效能由突触前和突触后神经元的动作脉冲发放的相对时刻来决定。如果突触前神经元的脉冲电位先于突触后神经元产生,则说明突触后神经元的脉冲发放受到了突触前神经元的影响,即突触的效能增强,权值增大;反之则说明突触后神经元的行为与突触前神经元无关,两者之间的突触权值应减小[2]。

图1 电路原理框图

2 电路结构

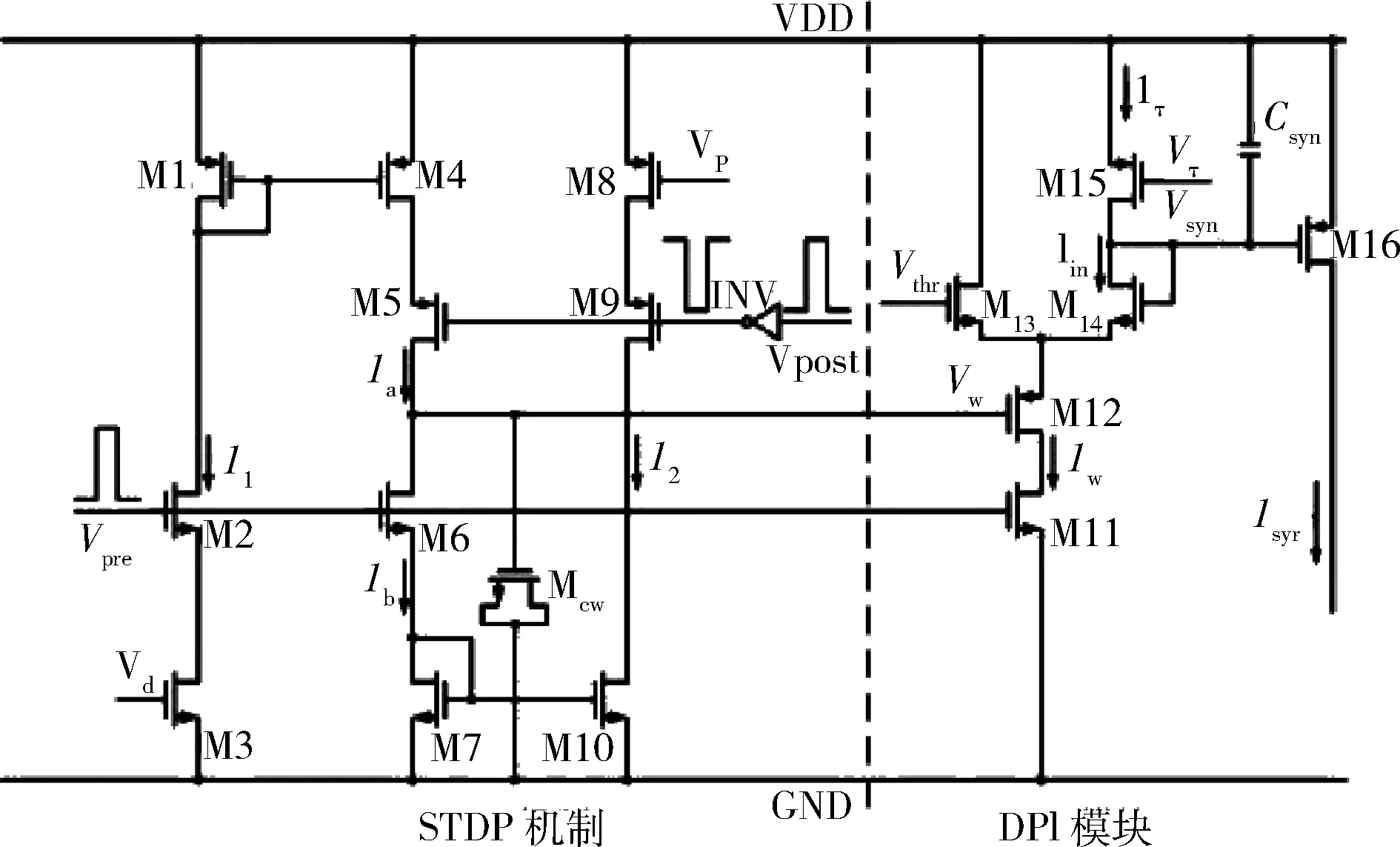

基于以上原则,本文设计的突触电路如图2所示,包括STDP功能模块和差分积分电路(Diff-Pair Integrator, DPI)。DPI电路最早由BARTOLOZZI C等人提出[3]。本设计在此基础上增加了STDP功能模块,使得该电路可以模拟突触特性。

图2 突触电路

图2中,虚线左边部分可以实现STDP功能,VW表示突触权值,存储在MOS电容Mcw上,Vd和Vp是决定电路偏置电流的可调参数,Vpre和Vpost分别代表突触前神经元和突触后神经元发放的动作脉冲,动作脉冲由晶体管M2和M9检测。当一个脉冲到达M2时,M2导通,产生的电流I1通过M1和M4组成的电流镜产生电流Ia给Mcw充电,使突触权值升高。当M9检测到突触后神经元产生的动作电位后也类似,M7和M10镜像产生的电流Ib提供Mcw的放电通路,使突触权值降低。如果突触后神经元的脉冲比突触前神经元脉冲先到达突触,则说明突触前神经元并没有影响到突触后神经元,这时突触权值会降低;反之则会升高。

突触电路的右侧就是DPI电路模块,当突触前膜的脉冲电位到来时,DPI的输入电流Iin可以表示为:

(1)

其中UT表示热电压,系数κ是MOS管的亚阈值斜坡因子。因此输出到下一级神经元的刺激电流可以表示为:

Isyn=I0exp[κ(Vdd-Vsyn)/UT]

(2)

由式(1)、(2)可以得到:

Iin=Iw/(1+Isyn/Igain)

(3)

其中,

Igain=I0exp[κ(Vdd-Vthr)/UT]

(4)

等价于一个虚拟的工作在亚阈值区的PMOS晶体管。由以上式子可以得到微分方程:

τdIsyn(t)/dt+Isyn(t)=Igain·Iw/Iτ

(5)

Isyn(t)=

(6)

为了能够更加真实地模拟出生物神经元动作脉冲的发放类型,神经元的设计采用了Izhikevich模型,这种模型结合了H-H模型和I&F模型的特点,既可以模拟多种脉冲类型,其电路实现又比较高效、简单[4]。 Izhikevich模型可以用如下公式描述:

(7)

当v≥30 mV时,则有

(8)

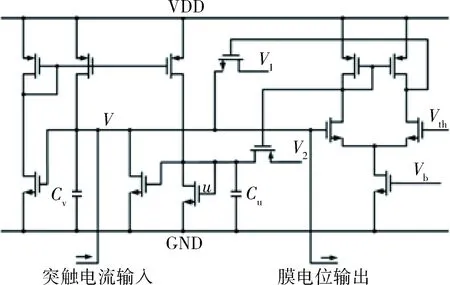

其中v表示神经元发放脉冲的电位,u是动作电位的恢复变量,对v起负反馈作用。当脉冲电位到达峰值(该模型为30 mV)时,v和u分别被重置为v1和v2。参数I表示从突触电路的得到的刺激电流。具体的电路如图3所示,该结构通过一个比较器实现了重赋值功能。

图3 神经元电路

电压Vb控制着比较器的静态电流,使比较器有合适的比较速度,Vth是比较器的阈值电压。当突触的刺激电流输入后,加上M1-M3的正反馈机制,电容Cv上的电压迅速升高,当电压超过Vth后,比较器输出电压VX增大,开关SW1导通,电容Cv较小,迅速放电使得输出膜电位迅速超极化,超极化后的膜电位由V1决定;另一方面,比较器的另一个输出VY控制着开关SW2的导通,由于Cu的值比Cv要大,无法被迅速充电到V2,因此每个膜电位的脉冲都会使Cu上的电压上升,上升到一定电压后,M4和M6导通,电流增大,进而影响膜电位的去极化。通过Cu的调节作用,产生的膜电位脉冲可以表现出自适应特性,改变V1和V2的值,可以模拟不同的脉冲模式。

3 电路仿真结果

基于 0.18 μm 标准CMOS工艺,电路的主要模块的芯片面积为0.018 9 mm2(180 μm×105 μm)。电路工作在0.6 V电源电压下,在Cadence环境下对突触电路和神经元电路的特性进行了仿真。仿真结果表明突触电路可以实现STDP传输机制,神经元电路可以高效模拟神经元多种类型的脉冲发放。

3.1 STDP传输机制仿真结果

图4反映突触权值的变化。当Tpre

图4 STDP机制仿真结果图

3.2神经元脉冲发放仿真结果

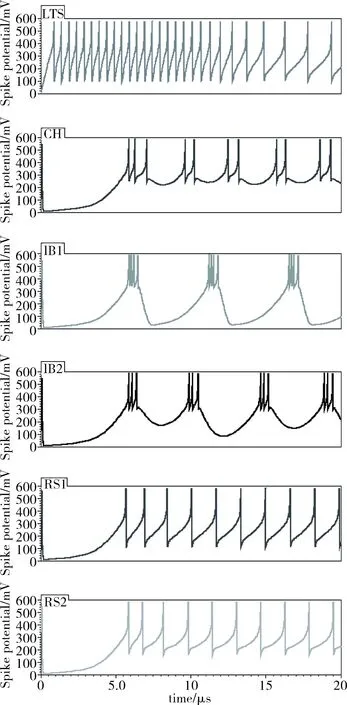

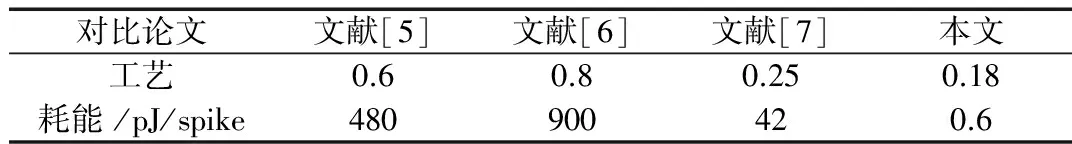

在本文所提到的神经元电路中,通过调节V1和V2,可以得到不同的脉冲发放模式。图5是对于相同的刺激信号,即100 nA的阶跃电流刺激,神经元电路所得到的不同的脉冲发放类型,表1显示了每种类型的脉冲所对应的调节电压及其所消耗的能量。 当V1为0.3 V,调节V2时可以得到LTS、CH和IB1这三种类型的脉冲;设置V1为零,改变V2的值可以得到RS1、RS2和IB2类型的脉冲。表2是与其他相关论文比较的结果,比较结果显示,本文中的突触和神经元的效率更高,有利于大规模集成。

图5 神经元电路的多种脉冲发放模式

动作电位模式LTSCHIB1RS1RS2IB2参数V1/mV075100255090参数V2/mV300300300000能量消耗/pJ/spike0.450.750.560.650.70.64

表2 能耗的比较

4 结论

本文所设计的突触电路和神经元电路结构简单,能够模拟生物神经元的多种脉冲发放模式,实现神经元信号传递的STDP学习机制。电路整体工作在亚阈值区,功耗小,效率高。其工作电压为0.6 V,每个脉冲产生的平均耗能仅为0.6 pJ,可以集成为超大规模神经网络。

[1] 陶建华, 陈云霁. 类脑计算芯片与类脑智能机器人发展现状与思考[J]. 中国科学院院刊, 2016,31(7):803-811.

[2] 陈云芝,徐桂芝,周茜,等.基于STDP可塑性自适应神经网络的构建及仿真研究[J].中国医学物理学杂志,2014,31(2):4820-4832.

[3] BARTOLOZZI C, MITRA S, INDIVERI G. An ultra low power current-mode filter for neuromorphic systems and biomedical signal processing[C]. IEEE Conference on Biomedical Circuits and Systems,2006:130-133.

[4] IZHIKEVICH E M. Simple model of spiking neurons[J]. IEEE Trans on Neural Networks,2003,14(6):1569-1572.

[5] Zhang Lei, Lai Qianxi, Chen Yong. Configurable neural phase shifter with spike-timing-dependent plasticity[J]. IEEE Electron Device Letter, 2010,31(7):716-718.

[6] INDIVERI G, CHICCA E, DOUGLAS R. A VLSI array of low-power spiking neurons and bistable synapses with spike-timing dependent plasticity[J]. IEEE Transactions on Neural Networks,2006,17(1):211-221.

[7] TANAKA H,MORIE T,AIHARA K. A CMOS spiking neural network circuit with symmetric/asymmetric STDP function[J]. IEICE Transactions on Fundamentals of Electronics Communications and Computer Sciences,2009,E92A(7):1690-1698.

Design of synapse and silicon neuron CMOS circuit for STDP

Sun Hongwei, Chen Song, Lin Fujiang

(School of Information Science and Technology, University of Science and Technology of China, Hefei 230026, China)

TN402

A

10.19358/j.issn.1674- 7720.2017.18.013

孙宏伟,陈松,林福江.一种可实现STDP机制的CMOS突触和神经元电路设计[J].微型机与应用,2017,36(18):43-45,48.

2017-03-21)

孙宏伟(1993-),通信作者,男,硕士,主要研究方向:模拟集成电路、神经形态芯片。E-mail:shongwei@mail.ustc.edu.cn。

陈松(1979-),男,博士,副教授,主要研究方向:VLSI及FPGA应用。

林福江(1958-),男, 博士,教授,主要研究方向:半导体器件、器件建模表征、射频集成电路。