JESD204B高速串行接口的FPGA实现

四川九洲电器集团有限责任公司 詹介秋

JESD204B高速串行接口的FPGA实现

四川九洲电器集团有限责任公司 詹介秋

本文针对软件无线电的发展趋势,介绍了目前高速AD所采用的JESD204B高速串行接口,阐明了其相对于传统LVDS、CMOS接口的优势。以TI公司ADS54J60芯片为例,较为详细的介绍了基于XILINX FPGA的JESD204B IP core的实现流程和方法,并对AD测试结果进行了简要的分析。结果表明:该测试流程及方法稳定可靠,AD性能良好,可为XILINX FPGA实现JESD204B接口提供较好的参考。

软件无线电;高速AD;JESD204B;ADS54J60

0 引言

伴随着软件无线电技术的不断发展,高速AD的应用范围越来越广泛,随之而来的是数字端的数据接口速度将变得越来越快。传统的AD与FPGA之间的数据接口通常采用LVDS、CMOS等并行方式,其在数据接口速率、布板面积、时序处理等方面均存在一定的不足。随着AD采样速率的进一步提高,一种新的高速串行数据总线接口即JESD204B接口应运而生。相对于传统的并行数据总线,JESD204B高速串行接口具有以下一些优势[1]:

(1)极大的提高了数据传输带宽,为射频直接采集技术的数字端提供了保障。

(2)简化了系统的PCB设计,避免了LVDS、CMOS等并行数据线在PCB上的长度匹配,节约了布线成本。

(3)减少了管脚数目,使得AD器件的封装大大减小,节约了布板面积。

目前,以ADI、TI等为代表的众多厂家已生产了多款具有JESD204B接口的高速AD,并且高速AD数字端均已开始向JESD204B接口发展。同等采样率下,相对于传统接口的AD,具备JESD204B接口的AD无论在数据位宽,AD性能等方面均有较大的提高。同时,FPGA巨头XILINX公司已就JESD204B接口提供了专门的IP core供用户使用。

基于上述情况,笔者以TI的ADS54J60芯片为例,该芯片为一款双通道1G/16bits AD,详细描述了XILINX公司FPGA的JESD204B接口的逻辑实现,并就该芯片给出了实际的性能测试结果。

1 JESD204B IP core简介

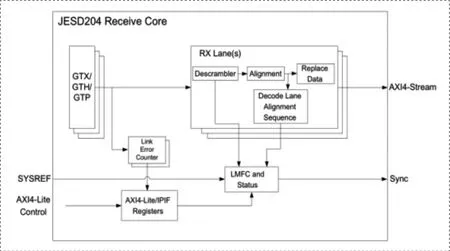

JESD204B是一种连接AD/DA与逻辑器件的高速串行接口,该接口能支持高达12.5Gbps的串行数据速率,并可以确保数据链路具有可重复的确定性延迟[2]。在XILINX公司FPGA设计中,一个实现JESD204B链路层的IP core和实现物理层的可配置SERDES便实现了JESD204B的接口设计。图1为XILINX公司FPGA JESD204B IP core接收AD数据的接口逻辑框图[3]。

图1 JESD204B IP core接收接口逻辑框图

用户在FPGA内部通过IP core提供的AXI4-Lite Control接口实现对JESD204B接口的控制与配置,通过AXI4-Stream接口实现数据的接收,AD数字接口直接连接到GTX/GTH收发器。外部硬件连接示意图如图2所示[3]。

图2 AD与FPGA连接示意图

下面以XILINX公司FPGA开发工具Vivado 2016.4为例,详细介绍了在该开发平台下利用IP core实现对TI ADS54J60芯片JESD204B接口的数据接收,并给出AD的性能测试数据。

2 JESD204B接口的FPGA实现

在Vivado 2016.4下打开JESD204B的IP core定制界面,图形界面下完成FPGA JESD204B接口的配置,实现与所连AD接口的匹配。配置界面如图3、4、5、6所示:

图3 JESD204B IP core配置界面1

图4 JESD204B IP core配置界面2

图5 JESD204B IP core配置界面3

图6 JESD204B IP core配置界面4

根据ADS54J60的芯片手册,完成对应FPGA端IP core的配置。在图3中,将FPGA GTX接收通道数设置为8 lanes,即该双通道AD的单路数据通过4 lanes与FPGA GTX接口进行数据交互。在本次测试中,AD输入的采样时钟设置为983.04MHz,因此,根据计算,该16bits AD单通道采样信号的数据量为:983.04*16*1.25=19.6608Gbps,单根lane的线速率为19.6608/4=4.9152Gbps,根据计算值完成图6中lane rate的配置,并将reference clock设置为lane rate的1/40,则JESD204B core clock可共用此时钟。同时根据AD的数据帧格式及通道配置完成相应IP core中图5参数的配置,该参数可以在生成IP core之后通过AXI4-LITE Control接口进行重配,在本设计中,由于AD的数据格式已经确定,故程序中不再需要对AXI4-LITE Control接口进行操作。

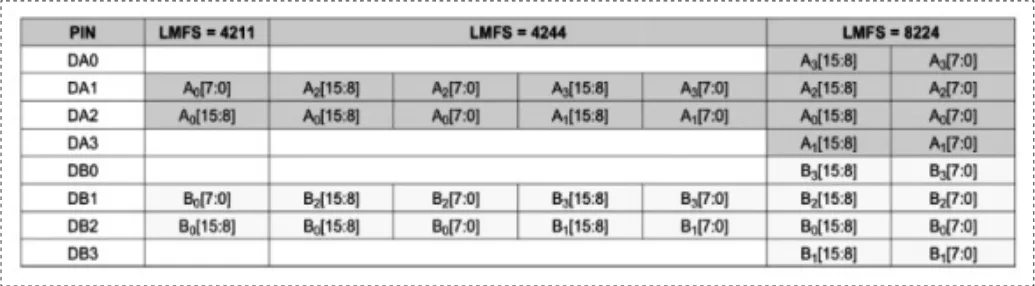

ADS54J60的数据帧格式的配置选择如图7所示[4]。

图7 ADS54J60 JESD204B接口数据帧格式

本次设计中AD输出通道配置采用LMFS=8224的模式,则在IP core内部,将每个通道的AD串行输出数据转换成了128bits的并行数据并通过用户接口逻辑送给设计者,则设计者需要根据该输出数据格式重新对IP core输出的AXI4-Stream 128bits AD并行数据进行排序,如图8所示。

图8 ADS54J60输出数据

signalA_sampl0_reg至signalA_sampl7_reg代表了AD采样的连续8个16bits采样数据,将总共16K采样数据存入FPGA FIFO并上传到上位机,通过Visual Analog软件对AD进行性能分析。

3 数据测试结果

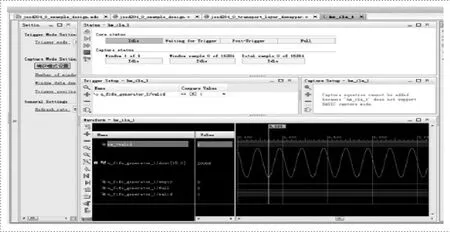

通过配置时钟芯片参数,给ADS54J60提供983.04MHz的采样时钟频率,并给FPGA的GTX接口提供122.88MHz的参考时钟频率。通过外接模拟信号源输入0dBm的单音信号,并根据不同的单音信号频率加上相应的带通滤波器,对16K采样点进行FFT,并对FFT结果进行分析,完成对AD的性能测试。图9为该单音信号数字化后在Vivado下导出的时域上的波形示意图,图10、11、12分别为983.04MHz采样时钟下采出的540MHz、690MHz、840MHz模拟信号做FFT后频谱在第一奈奎斯特区间上的显示。

图9 模拟信号在时域上的图形

图10 540MHz模拟信号在频域上的图形

图11 690MHz模拟信号在频域上的图形

图12 840MHz模拟信号在频域上的图形

从图中可以看出,信号无杂散动态范围SFDR均大于80dBc,通过计算,得出信噪比SNR均大于65dBFs,AD性能良好,采样接口设计稳定可靠。

4 结束语

笔者针对目前AD芯片发展趋势,比较了JESD204B接口相对于传统并行数据接口的优势,详细介绍了基于XILINX公司FPGA IP core的设计流程,实现了对TI ADS54J60芯片JESD204B接口的数据读取操作,并通过对采样数据进行FFT变换,对信号进行了无杂散动态范围和信噪比的分析。整个流程对设计具有JESD204B接口的AD提供了较好的帮助。

[1]Ian Beavers,Jeff Ugalde.选择合适的转换器:JESD204B与LVDS对比.ADI,2014.

[2]Jonathan Harris,Ian Beavers.为什么不需要惧怕JESD204B.ADI,2014.11.

[3]XILINX.JESD204 v6.1 LogiCORE IP Product Guide.PG066 April 1,2015.

[4]TEXAS INSTRUMENTS.ADS54J60 DATASHEET.SBAS706CAPRIL 2015-REVISED JANUARY 2017.