基于FPGA的模型计算机设计与实现

杨锐++翟社平++焦继业

摘 要:结合计算机系统能力培养目标,以设计一个基于FPGA的模型计算机作为计算机组成原理课程设计样例,说明模型机的组织结构,给出指令系统和构成部件的设计与实现,展示功能仿真测试。

关键词:模型机;计算机组成原理;FPGA

0 引 言

计算机组成原理课程是计算机专业的一门重要专业基础课,在培养学生计算机系统能力的过程中起着承上启下的重要作用[1]。通过课程理论学习,学生理解计算机内部各功能部件的组成、设计方法及逻辑实现,建立计算机系统层次结构的概念。课程实验使学生进一步掌握计算机硬件系统分析设计方法,有助于学生深入理解课程的内容,对于培养学生的系统设计能力、工程应用能力和创新能力具有重要的意义。

传统的基于专用实验箱的实践教学模式无法满足系统能力的培养要求[2-3]。在计算机组成原理实践教学中,可以采用基于FPGA的EDA方式进行模型计算机的设计与实践,有效解决传统实践模式中实验效率低、实验内容验证多设计少、不利于学生构建整机概念等问题,培养学生分析设计能力,满足系统能力培养要求。笔者结合计算机组成原理基本理论,采用VerilogHDL完成一个功能较完整的片上模型计算机系统设计实例,包括ALU、微程序控制器、时序产生电路、存储器、指令系统等的设计。功能仿真正确,并在Vavido中完成综合并下板,对于学生实现基于FPGA的模型机设计具有很好的指导意义。通过在FPGA平台上设计完成一个具有CPU、存储器、端口并能执行一个指令系统的模型机,有助于学生计算机系统能力的培养。

1 模型机架构分析

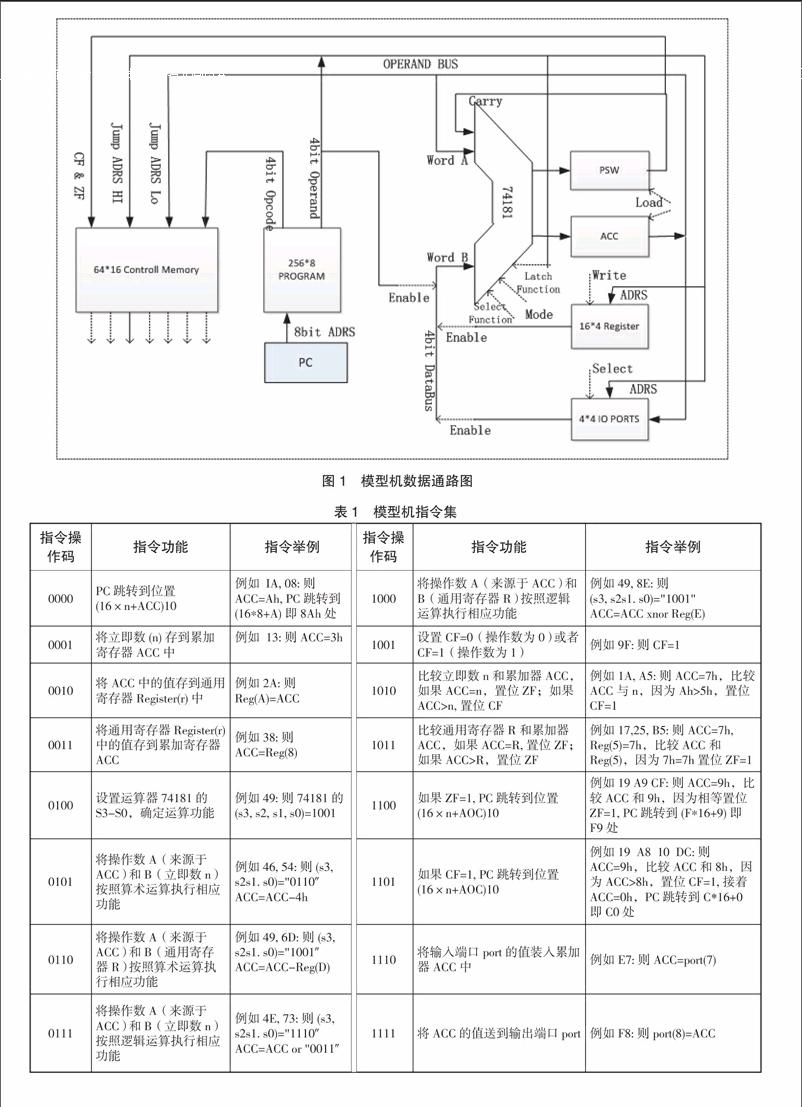

该模型机包括运算器、控制器、程序存储器、数据寄存器、微程序存储器和输入输出端口组成 ,模型机数据通路见图1。

模型机采用学生熟悉的74181作为算术逻辑运算单元,运算操作数均为4bit数据。一个操作数来源于累加器,另一个操作数通过4位数据总线从内存、寄存器和输入端口发送给ALU。地址总线为8位。数据通路中包含累加器、16个通用寄存器、4个输入输出端口。模型机采用8位程序计数器、微程序解释的方法执行指令,指令存储器为256字节,控制存储器为1K位。指令系统有16条8位的机器指令,包括数据传送指令、算术逻辑运算指令、比较和跳转指令。此模型机为实验教学引入,用VerilogHDL语言设计实现。

2 模型机设计

2.1 模型机指令系统设计

模型机的指令由高4位操作码和低4位地址码构成,1条指令字长为1个字节。由于操作码为4位,指令集里一共有16条指令,表1为模型机指令集。

指令集包括算术逻辑运算指令、比较和跳转指令和数据传输指令。

指令#4、#5、#6、#7、#8、#9为算术逻辑运算指令。运算器的设计采用74181作为算术逻辑运算部件。为了让模型机可以完成74181支持的32种算术逻辑运算,首先通过指令#4设置“S3—S0”的值并存入alu-func寄存器,再通过指令#5或指令#6完成算术运算,指令#7或指令#8完成逻辑运算。相同类型运算区别在于第2操作数是来自立即数还是寄存器。指令#9完成对CF的置位或复位。

指令#1、#2、#3、#E、#F为数据传输指令,数据的传送都经过累加器。指令#1将4位立即数操作数从程序存储器送到累加器。累加器和寄存器之间的数据传输由指令#2和指令#3实现。指令#E和指令#F实现累加器和4个输入输出端口的数据传输。

指令#0、#C、#D实现无条件跳转和条件跳转。条件跳转之前需要执行比较指令#A和#B,算术逻辑部件74181完成累加器和立即数或者寄存器的比较,并设置ZF、CF标志位。通过把跳转指令中给出4位立即数作为目标地址的高4位,累加器中的数作为目标地址的低4位,组合成8位的绝对地址从而寻址到整个256字节的程序空间。

2.2 微指令设计

指令操作码字段决定控制存储器的微指令入口地址,每条机器指令的执行都是通过执行控制存储器中的4个微指令序列来完成。由于每个时钟周期完成1条微指令,1条机器指令的执行需要4个时钟周期。定义微指令字长为16位,从高位到低位依次为F15—F0,表2显示了对应信号的含义。

每个机器指令对应4个微指令序列,相应的控制存储器存储64条微指令,表3为控存中微指令真值表。

2.3 模型机硬件系统设计

模型機由运算器、程序计数器、程序存储器、微程序控制器、输入输出端口等部分构成,采用Verilog HDL语言实现模型机各功能模块设计。

(1)程序存储器u_prog_memory容量为256字节,存储机器指令,最多可以存储256条8位指令。

(2)程序计数器u_prog_counter模块实现8位程序指针pc,指明下一条指令的地址。顺序执行指令,pc每次自加;若为跳转指令,pc修改为要跳转的绝对地址。该模块也提供2位微地址指针。

(3)指令的执行是通过微指令解释实现的:4位指令操作码和2位微程序指针被送入控制存储器u_control_memory,控制存储器的输出为16位。每条机器指令对应4条微指令,根据操作码和微指针,每个时钟周期微程序存储器都有1个16位的输出F15—F10,输出的值与表3中对应单元的编码一致。

(4)运算器包含算术逻辑运算模块u_alu_74181、累加器u_acc、数据寄存器u_reg、标志寄存器u_alu_flag和181功能选择寄存器u_alu_func。模块u_alu_74181实现74181的32个算术逻辑运算功能[4],模块u_alu_func存储指令#4给出的功能选择编号并提供给u_alu_74181[s3:0]。操作数A来源于累加器u_acc,另一个操作数B来源于立即数u_prog_memory[inst3:0],或者数据寄存器u_reg,或者输入输出端口u_port。运算结果影响标志位,存储在标志寄存器u_alu_flag中。模型机设计实现16个通用寄存器,4个输入输出端口。endprint

(5)顶层exe_model中将以上9个模块实例化并连接用来构成完整模型机。exe_model定义的clk为外部输入的时钟,res为外部输入的复位信号,port为连接外设的双向数据线。图2为最终的完整模型机设计图。

3 模型机功能测试

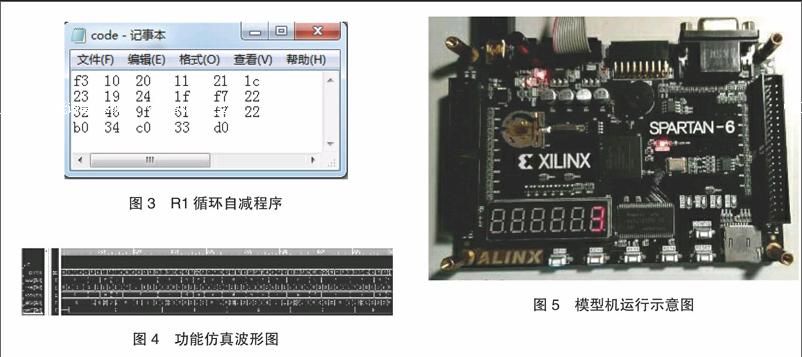

設计好各模块后,对模型机进行功能仿真测试。在完成每条指令的功能测试后,用模型机指令设计程序,图3的程序实现先将R1赋初值0,再循环自减。

在模块u_prog_memory中通过系统任务 “$readmemh("./code.txt",mem);”将程序存入模型机程序存储器中。图4为在Debussy下通过调用Modelsim生成的波形图。从图4中可以看出,模型机运行正确。

进一步优化程序,将R1递减的值以1秒频率在数码管显示。首先在Vivado里综合仿真过的Verilog文件。此时微程序存储器模块和程序存储器模块均在Vivado下通过ip核实例化实现,初值通过对应的coe文件进行初始化。经过综合、布局布线、管脚映射等步骤后,将生成的exe_model.bit下载到Spartan开发板进行电路验证。数码管循环依次显示F—0,见图5[5-7]。

4 结 语

模型机的设计开展随着理论教学同步进行。结合课程教学采用的教材[8],计算方法和运算器学习结束后完成74181模块设计和仿真;存储器学习结束后完成指令存储器、控制存储器模块的描述和仿真;指令系统和处理器学习结束后学生理解模型机数据通路,进行指令系统和微指令分析设计,并完成累加器、标志寄存器等模块设计;在学期末组成原理课程设计的集中实践时间里进行顶层电路设计,实例化各功能模块并连接,完成模型机功能仿真然后下板进行电路测试。

从实施效果来看,通过EDA在FPGA平台上完成模型计算机设计,学生不仅建立了整机概念,具备了基本的系统分析设计能力,更激发了学习热情和创新能力,培养了计算机系统分析设计能力。目前的模型机不支持堆栈和子程序调用等功能,后续可以考虑提升课程设计的复杂度,扩大指令规模,引入具有中断、Cache等工作机制的模型机设计,充分激发学生的能动性和创造性,进一步加强学生系统设计能力的培养。

参考文献:

[1] 袁春风, 杨若瑜, 王帅, 等. 计算机组成与其他课程之间的关联内容分析[J]. 计算机教育, 2015(17): 35-38, 87.

[2] 谭志虎, 胡迪青, 秦磊华. 计算机组成原理课程设计的改革[J]. 电气电子教学学报, 2016(6): 110-112.

[3] 袁春风, 张泽生, 蔡晓燕, 等. 计算机组成原理课程实践教学探索[J]. 计算机教育, 2011(17): 110-114.

[4] 潘松, 潘明. 现代计算机组成原理[M]. 北京: 科学出版社, 2007.

[5] 张胜, 胡建明, 蔡虹. 基于FPGA技术的8位模型机设计与实现[J]. 南昌航空大学学报(自然科学版), 2010(3): 21-26.

[6] 徐爱萍, 张玉萍, 涂国庆. 基于VHDL 之CPU 设计与实践[J]. 实验室研究与探索, 2014(5): 120-124.

[7] 肖铁军, 刘芳. 基于FPGA的“计算机组成原理”模型机设计[J]. 电气电子教学学报, 2009(4): 81-82, 85.

[8] 白中英, 戴志涛. 计算机组成原理[M]. 北京: 科学出版社, 2015.

(编辑:孙怡铭)endprint