开源片上系统FreedomE310调试过程原理分析

,,

(酒泉卫星发射中心,酒泉 735000)

开源片上系统FreedomE310调试过程原理分析

雷思磊,王军,张海燕

(酒泉卫星发射中心,酒泉 735000)

Freedom E310是第一款基于RISC-V指令集架构的开源商业片上系统,可以依据具体应用场景对其进行深度定制,在介绍Freedom E310中与调试有关的模块、地址空间、控制状态寄存器之后,从原理上分析了halt、resume、step、断点设置等调试指令的实现过程。

RISC-V;Freedom E310;JTAG

引 言

伯克利大学于2014年发布了开源指令集架构RISC-V,其目标是成为指令集架构领域的Linux,应用覆盖IoT(Internet of Things)设备、桌面计算机、高性能计算机等众多领域[1]。RISC-V自发布以来受到多方关注与参与,RISC-V的生态环境逐渐完善,涌现了众多开源处理器及SoC(System on Chip)采用RISC-V架构,其中Rocket-Chip就是由伯克利大学发布的基于RISC-V的可配置SoC,通过配置不同的参数可以得到不同性能、应用于不同场合的SoC。RISC-V的迅速发展还激励其设计人员成立了SiFive公司,专注于定制化SoC设计,其产品线包括:

① 开源处理器核Coreplex IP系列,包括Coreplex U、Coreplex E两个系列。其中Coreplex U系列目前有U5 Coreplex子系列,其是64位RISC-V架构处理器,支持多核、多级缓存、硬件支持的单精度与双精度浮点运算;Coreplex E系列目前有E3 Coreplex子系列,其是32位RISC-V架构处理器,依据应用环境可配置支持RV32E、乘法、除法、浮点运算等,目标是低功耗的嵌入式控制器。

② 开源SoC Freedom系列,包括Freedom Unleashed、Freedom Everywhere两个系列。其中Freedom Unleashed系列是基于U5 Coreplex的SoC,包括U500子系列,其外设控制器包括DDR3/DDR4 DRAM 控制器、PCIe 3.0控制器、1 Gb Ethernet控制器、USB 3.0控制器等,支持Unix等多种操作系统;Freedom Everywhere系列是基于E3 Coreplex的SoC,包括E300子系列,其具有片上Debug单元、平台级中断控制器等,支持FreeRTOS等多种操作系统。

③ Freedom E310是Freedom Everywhere的子系列E300的一个流片实例,目标应用场合是微控制器、IoT、可穿戴设备等,其处理器核是E3 Coreplex子系列的一个实例——E31,支持RV32IMAC指令集[2]。其采用180 nm工艺流片成功,主频可以达到320 MHz以上。

④ 开源开发板HiFive1,是第一款采用Freedom E310作为核心控制芯片的Arduino兼容开发板。作为深度开源的代表,其微控制器对应的RTL代码、电路图设计文件、PCB设计文件等完全开源。

本文首先简单分析了Freedom E310的Debug单元、Debug地址空间、与Debug相关的控制状态寄存器(Control Status Register,CSR),然后给出了使用OpenOCD+J-Link适配器的调试方案,并分析了OpenOCD与Freedom E310之间通信的原理,最后对调试过程的原理逐一进行分析,包括halt、resume、step、硬件断点、软件断点等命令的执行原理。

1 Freedom E310介绍

1.1 Freedom E310的组成

Freedom E310的组成如图1所示。处于核心的是单发射、顺序执行处理器E31,支持RV32IMAC指令集,具有16 KB的指令缓存和16 KB的数据SRAM,在满足一定工艺条件下的最高主频可达320 MHz。

图1 Freedom E310的组成

Freedom E310有多个外设,通过TileLink互连总线将多个外设连接到处理器。主要外设包括[3]:

① AON(Always-ON domain,始终在线):不受处理器核心电源管理的影响,包括实时计数器、看门狗、复位与电源管理部分。

② GPIO(General Purpose Input/Output,通用输入输出)控制器:每一个引脚都可以设置成输入或者输出,并可以设置是否能够引发中断。E31的GPIO可以复用为UART、I2C、SPI、PWM等。

③ PLIC(Platform-Level Interrupt Control,平台级中断控制器):用于接收外部的中断信号,然后按照优先级送给处理器,支持52个外部中断源、7个中断优先级。

④ Debug Unit(调试单元):支持外部调试器通过标准JTAG接口进行调试,支持2个硬件断点、观察点。

⑤ QSPI(Quad-SPI):QSPI Flash控制器,用于访问Flash,可以支持eXecute-In-Place模式。

1.2 Debug单元

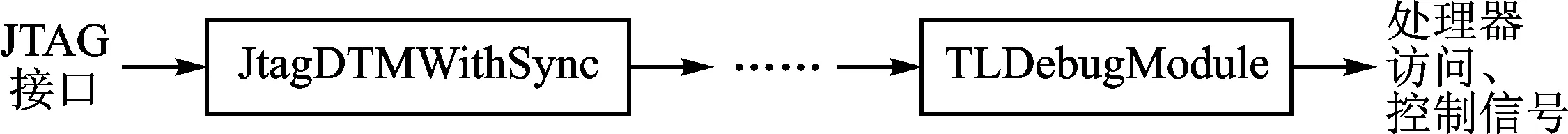

图2 Debug单元的主要结构

Debug单元的主要结构如图2所示。Freedom E310有一个标准的JTAG(Joint Test Action Group)接口,如表1所列。外部调试工具可以通过该接口进行调试,包括:设置断点、设置观察点、单步执行、查看寄存器、访问存储器等操作,所有的外设、中断控制器也可以通过JTAG接口进行访问。外部调试工具将调试命令(如设置断点)通过JTAG接口送入Freedom E310,后者有两个主要的模块处理该命令,首先是JtagDTMWithSync模块,该模块的作用是按照JTAG协议的要求分析JTAG接口送入的命令,其内部有一个状态机,实现了TAP(Test Access Port)控制器,可以将其理解为一个串行转并行接口。提取出的指令经过一系列处理,最后送入TLDebugModule模块,该模块按照调试命令,对处理器发出实际的控制信号。

表1 Freedom E310的JTAG接口

1.3 Debug地址空间

Freedom E310的Debug地址空间占用地址为0x0~0xFFF,共4 KB。其地址分配情况如表2所列。

表2 Freedom E310的Debug地址空间

0x100、0x104、0x108、0x10C都是“只能写”的地址空间,如果向这个地址空间写入一个处理器核的ID,那么就执行相应的动作,比如向地址0x100写入1,那么就会清除处理器核1的Debug中断。

Debug RAM是Debug中断例程可以使用的RAM,在Freedom E310调试过程中,OpenOCD可以向该空间写入调试相关代码。

Debug ROM中存放的是Debug中断例程,Debug中断例程是固化在Debug ROM中的。Freedom E310的Debug中断例程的源码位于debug_rom.S中。

1.4 Debug相关的控制状态寄存器

Freedom E310与Debug相关的主要控制状态寄存器如表3所列。

表3 Freedom E310与Debug有关的CSR[4]

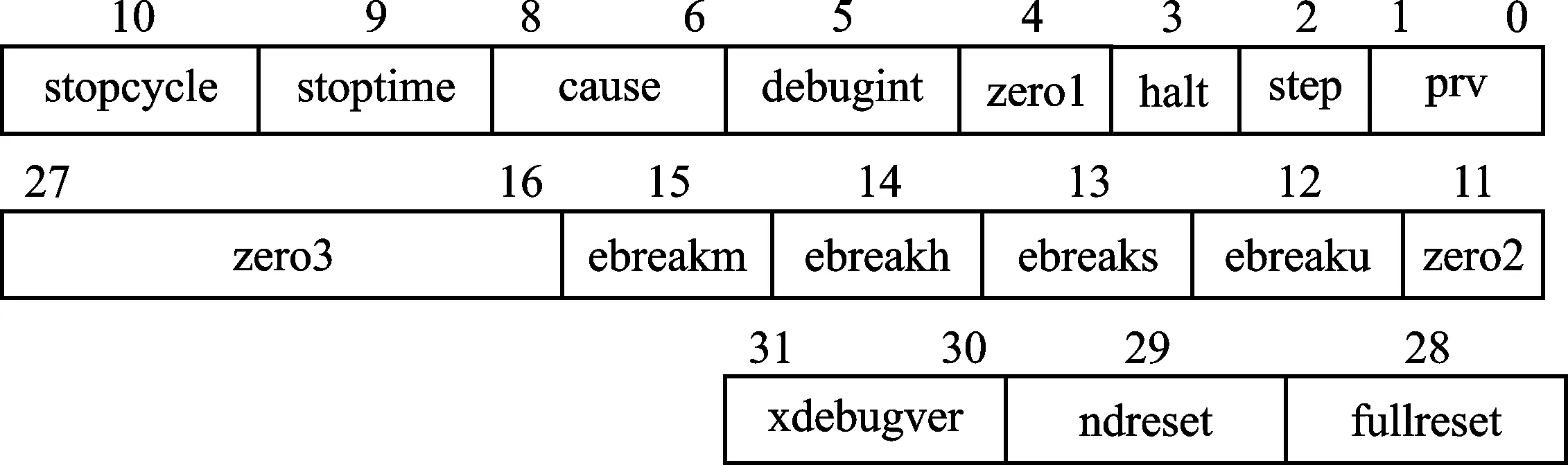

触发器选择寄存器、触发器数据寄存器1、触发器数据寄存器2用来设置硬件断点。Debug指令地址寄存器中存储的是退出Debug模式时将要执行的下一条指令地址。DCSR的结构如下所示:

其中的关键字段如下:debugint为是否由Debug中断发生;halt为是否暂停运行;cause为暂停运行的原因。

2 Freedom E310调试方案

可以使用OpenOCD、J-Link对Freedom E310进行调试。OpenOCD起源于2005年的奥格斯堡应用科学大学,并迅速发展成为一个应用广泛的开源项目,其目标是为嵌入式系统提供调试、在系统编程、边界扫描测试等功能[5]。J-Link 是 SEGGER 公司为支持仿真 ARM 内核芯片推出的 JTAG仿真器。使用OpenOCD、J-Link对Freedom E310进行调试的整体结构设计如图3所示。OpenOCD运行在主机上,主机通过USB接口连接J-Link,后者通过JTAG接口连接Freedom E310。J-Link接收OpenOCD通过USB口送入的调试指令,然后通过JTAG接口送入Freedom E310,并将Freedom E310的响应信息回传给OpenOCD。

图3 Freedom E310调试方案整体结构

OpenOCD的调试指令来自于用户通过Telnet或者GDB的输入,用户可以输入各种调试指令,如暂停运行(halt)、继续运行(resume)、单步执行(step)、查看寄存器(reg)、设置断点(bp)等。

3 OpenOCD与Freedom E310通信过程原理分析

前文已述,Freedom E310的Debug单元包含一个JTAG TAP控制器,其中包含若干个JTAG寄存器,可以按照IEEE Std 1149.1-2013的标准访问相应的JTAG寄存器,访问过程有两步:

① 使用JTAG IR(Instruction Register)选择要访问的JTAG寄存器。

② 如果是读操作,那么读取JTAG DR(Data Register),其内容是上一步选择的JTAG寄存器的值;如果是写操作,那么将要写的数据写入JTAG DR即可,该值会最终写入上一步选择的JTAG寄存器。

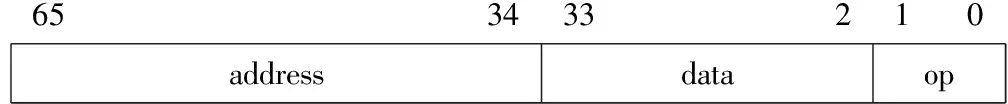

Freedom E310有一个特殊的JTAG寄存器,是Debug Bus Access(Debug总线访问)寄存器,其结构如下所示:

653433210addressdataop

寄存器结构分为三个部分,分别是地址(address)、数据(data)、操作符(op),OpenOCD通过J-Link操作该Debug Bus Access寄存器,便实现了对Freedom E310内部任意地址的读写操作,操作符指明是读操作还是写操作。对于写操作,数据部分是要写入的数据;对于读操作,数据部分是读取到的数据。

4 调试过程原理分析

4.1 halt命令执行过程分析

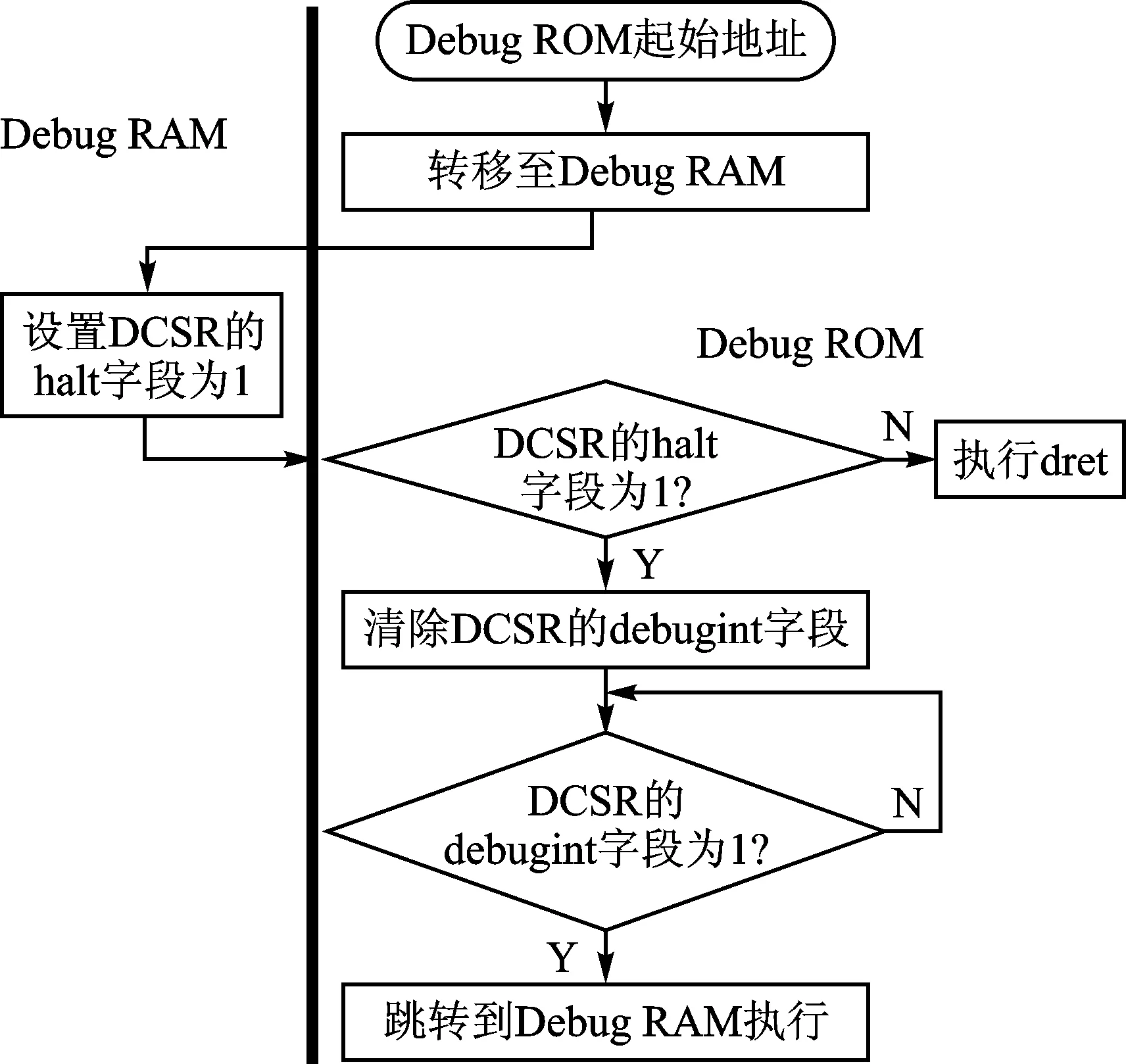

halt命令的作用是使处理器暂停运行。用户在Telnet或者GDB中输入halt命令,该命令被送入OpenOCD,后者通过Debug Bus Access寄存器向Freedom E310的Debug RAM(起始地址是0x400)处写入4条指令,作用是设置DCSR的halt字段为1,并在写入第4条指令的时候引发Freedom E310的Debug中断。该中断会设置DCSR的debugint字段为1,Freedom E310随后转入Debug中断处理例程,也就是转移到Debug ROM(起始地址是0x800)处开始执行,随后的过程如图4所示。首先转移至Debug RAM,执行OpenOCD传入的4条指令(最后一条指令是转移指令),接着转移回Debug ROM,然后清除DCSR的debugint字段(参考第1.3节,通过向地址0x100写入处理器核的ID,即可实现),最终进入一个循环,在循环中不断读取DCSR的debugint字段,判断是否有中断发生,如果没有,那么继续读取DSCR的debugint字段。这就是Freedom E310对halt命令的处理过程,最后进入了一个循环中,从用户的角度,可以认为Freedom E310进入了停止运行状态,实际上还是在不停地运行。

图4 Debug ROM中断例程对于halt命令处理过程

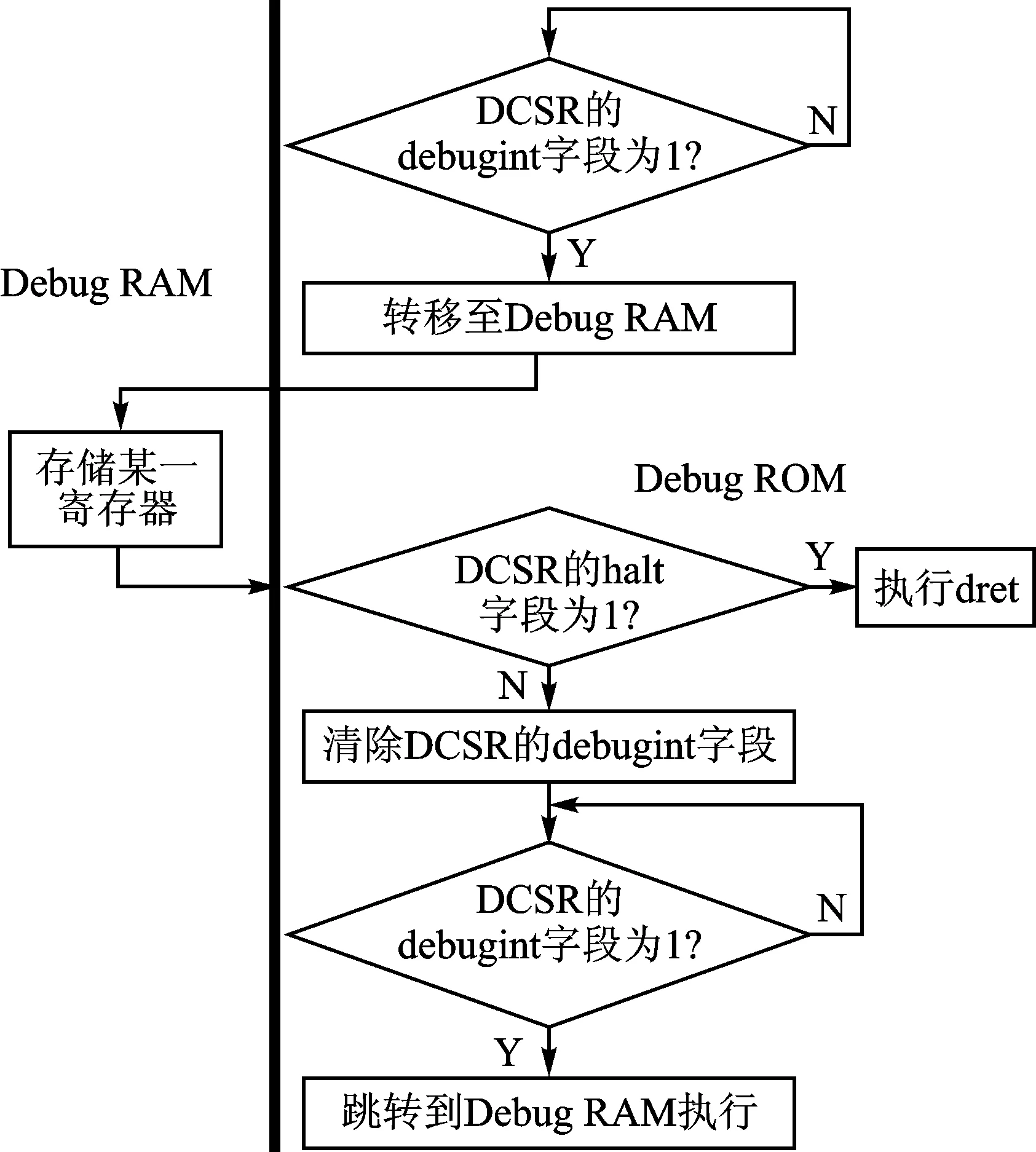

随后,OpenOCD通过Debug Bus Access寄存器读取硬件上下文,包括通用寄存器x1-x31、Debug PC寄存器、DCSR寄存器等。读取方法为:首先通过Debug Bus Access寄存器在Debug RAM中写入一条指令,该指令就是存储某一寄存器的指令(一般为store指令,将目标寄存器存储到Debug RAM的0x410处),随后引发Debug中断,但是此时已经在Debug中断处理过程了(执行halt命令导致的),由于Debug中断不嵌套,所以该中断不会使处理器转移至Debug ROM起始部分,仅仅会设置DCSR的debugint字段为1,参考图4可知,Freedom E310将再次转移到Debug RAM中执行,执行其中的存储某一寄存器的指令,执行完成后,Freedom E310再次转移到Debug ROM中,最后进入循环等待状态。这一过程如图5所示。

图5 OpenOCD获取上下文寄存器的过程

此时,OpenOCD通过Debug Bus Access直接读取地址0x410的数据,就获取了目标寄存器的值。OpenOCD将读取到的通用寄存器x1~x31、Debug PC寄存器、DCSR寄存器等的值都保存在自己内部的一个结构体中。

4.2 resume命令执行过程分析

resume命令与halt命令是配合使用的,可以使Freedom E310继续运行用户程序。当用户在Telnet或者GDB中输入resume命令,该命令被送入OpenOCD,后者通过Debug Bus Access寄存器向Freedom E310的Debug RAM处写入4条指令,作用是恢复Debug PC的值,并在写入第4条指令的时候引发Freedom E310的Debug中断,但是此处已经在Debug中断处理过程了(执行halt命令导致的),由于Debug中断不嵌套,所以该中断不会使处理器转移至Debug ROM起始部分,仅仅会设置DCSR的debugint字段为1,随后的过程如图5所示。只是将图中Debug RAM中的代码换为“恢复Debug PC寄存器”。

之后,OpenOCD再次通过Debug Bus Access寄存器向Freedom E310的Debug RAM处写入4条指令,作用是设置DCSR寄存器的halt字段为0,并在写入第4条指令的时候引发Freedom E310的Debug中断,随后的处理过程如图5所示,只是将图中Debug RAM中的代码换为“设置DCSR的halt字段为0”,并且,转移至Debug ROM后,由于DCSR的halt字段为0,所以会执行dret指令,Freedom E310从中断处理例程返回,继续执行Debug中断前的代码,从用户的角度,可以认为Freedom E310继续运行了。

4.3 step命令执行过程分析

一般是在halt命令输入后,再输入step命令,该命令是单步执行命令。当用户在Telnet或者GDB中输入step命令后,该命令被送入OpenOCD,首先按照第4.2节resume命令的执行过程进行处理,但是此时图中Debug RAM中的代码会设置DCSR的step字段为1。Freedom E310检测到该字段为1,会在执行完一条指令之后再次触发Debug中断,进入Debug ROM开始执行,最终还是进入循环等待状态,参考图4。

4.4 硬件断点实现过程分析

用户在Telnet或者GDB中输入bp命令,可以设置断点,bp后面加上参数hw,就表示设置的是硬件断点,该命令被送入OpenOCD,后者通过Debug Bus Access寄存器向Freedom E310的Debug RAM处写入指令,作用是通过Trigger Select、Trigger Data1、Trigger Data2设置硬件断点寄存器,Freedom E310默认配置了两个硬件断点寄存器。在写入最后一条指令的时候引发Freedom E310的Debug中断,Freedom E310转移至Debug ROM

Debugging Process Principle Analysis of Open-source SoC Freedom E310

LeiSilei,WangJun,ZhangHaiyan

(Jiuquan Satellite Launch Center,Jiuquan 735000,China)

Freedom E310 is the first RISC-V instruction set architecture based on open-source commercial SoC,which can be customized according to the specific needs.In the paper,after the introduction of the debugging module,the address space and the control status register in Freedom E310,the realization process of halt,resume,step,breakpoint setting and so on.

RISC-V;Freedom E310;JTAG