晶体管阵列老炼时结温测量方法研究

吕贤亮,麻 力,任 翔,孙 明

(中国电子技术标准化研究院 基础产品研究中心,北京 100176)

研究与试制

晶体管阵列老炼时结温测量方法研究

吕贤亮,麻 力,任 翔,孙 明

(中国电子技术标准化研究院 基础产品研究中心,北京 100176)

对PNP晶体管阵列采用矩阵热阻法和温度敏感参数法(TSP)两种结温测量的方法进行对比分析研究,并采用红外热像进行试验验证。结果表明,采用矩阵热阻法可以综合考虑各芯片之间的耦合作用,但由于矩阵热阻法试验程序较为复杂,且需要多次换算,从而较容易引入误差。而温度敏感参数法操作简单,测量准确,可以实现实时监测阵列管工作状态下的结温。

晶体管阵列;老炼;结温;温度敏感参数;矩阵热阻;红外热像

电子器件在功率老炼时通常要求在最高结温TJmax下进行[1-2],其老炼的难点和重点均为结温的测量。现今对于分立器件结温测量的研究主要集中在单芯片器件,而对多芯片器件的研究则相对较为匮乏。单芯片器件的结温测量方法对于多芯片器件又不完全适用。

国内普遍采用热阻换算的方式来确定器件当前工作状态下的结温,这种简单的热阻换算方式只适用于单芯片器件,而对于复杂的多芯片器件则无法适用。还有学者提出了通过校温曲线间接获得器件结温的方式[3],该方法强烈依靠器件校温曲线的线性度,只能对校温曲线线性度较好的器件进行测试,另外该方法也只适用于单芯片器件。

对此,国外学者在这方面进行了相应的研究,并提出了一些解决方法。在热阻方面主要有平均热阻法[4]和芯片独立热阻法[5-6]。该两种热阻方法,各自都存在一些不足之处,其中平均热阻法未考虑器件内部各芯片的热分配和变化问题,并且只能给出各芯片的平均温度,不适用于结温有较大差异的情况;而芯片独立热阻法对器件中无功耗的芯片不适用,且该方法未考虑芯片之间的耦合热传递作用[7]。在结温直接获得方面,有通过三个直流功率直接获得器件结温的方法[8],但是该方法要求三个功率下器件的结温必须相同,否则,器件的β或Vbe线性度将会严重影响测试准确性。

本文采用了矩阵热阻法和温度敏感参数法对晶体管阵列的结温测量方式进行了研究。前者综合考虑了芯片之间的热耦合作用;后者通过结温和温度敏感参数的一一对应关系很好地回避了校温曲线线性度和在线监测的问题。

1 结温测量方法理论基础

由于器件的结温无法直接测量,只能通过间接的方式来获得器件的结温。通常器件的结温获得方法有热阻法和温度敏感参数法两种。

a)热阻法

通常器件的结温测量方法是通过器件的热阻值来换算,根据热阻计算公式:

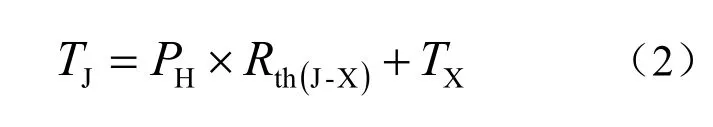

式中:TX指热阻测试的温度参考点,当TX为TA时表明温度参考点为试验环境,当TX为TC时表明温度参考点为器件管壳,当 TX为 TL时表明温度参考点为器件引线,根据不同类型的器件一般采用的温度参考点为TA或TC;加电功率为PH;结温为TJ。

通过热阻公式可得到:

从而只需提前获得器件的热阻Rth(J-X)就可以通过加电功率PH和参考点的温度TX获得结温TJ。

b)温度敏感参数法

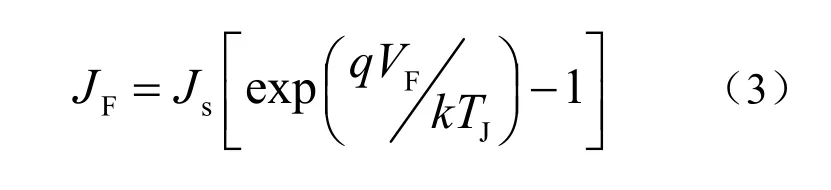

根据半导体分立器件内的PN结肖克莱方程[10],正向电流密度JF:

式中:VF为正向压降;Js为反向电流密度;q为电子电荷;k为波尔兹曼常数,有:

式中:Dn、Dp为电子、空穴扩散系数;np0、pn0为电子、空穴平衡浓度。Ln、Lp为电子、空穴扩散长度。

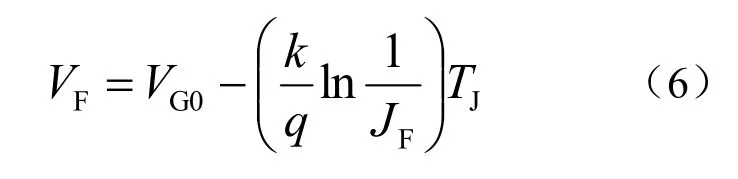

通过换算可得:

式中:VG0为热力学温度零度时,PN结材料导带底和价带顶的电势差。

从上述公式中可以得到当 PN结材料和正向电流一定的情况下,其正向压降VF与结温TJ成一一对应的关系。

因此,对于相同正向电流(此处指的是正向压降VF的测量电流,而不是工作电流)的器件,可以通过相同的正向压降VF来表征器件的结温TJ。

2 实验及分析讨论

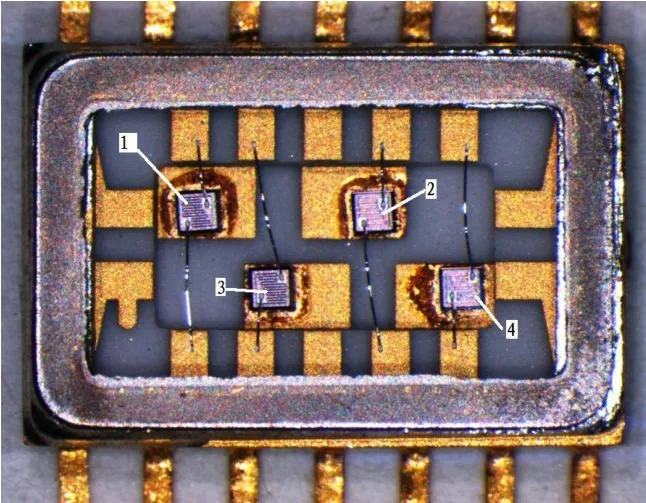

以某PNP晶体管阵列(以下简称阵列管,见图1)为例,其老炼试验条件:t=1000 h,加电功率为VCE=13 V,IC=20 mA,通过调节环境温度 TA使TJ=150 ℃。

图1 PNP晶体管阵列结构图Fig.1 Construction of the PNP transistor array

2.1 矩阵热阻法

对于多芯片器件,综合考虑各芯片之间互相的热耦合作用,可定义某一X芯片的结温为:

式中:TXi为第i个芯片对目标X芯片的热影响; TREF为参考点的温度,从而结合得到:

可得到:

式中:

首先测量图1中的1号芯片对每个芯片的热阻值。对1号芯片施加功率为VCB=13 V,IC=20 mA,然后分别测量各芯片的热阻:R11=314.5 ℃/W,R21=23.1 ℃/W,R31=24.3 ℃/W,R41=20.8 ℃/W。

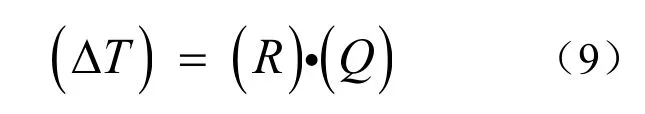

对剩余3个芯片也同样处理,最终得到20个热阻值。把其列成矩阵可得到:

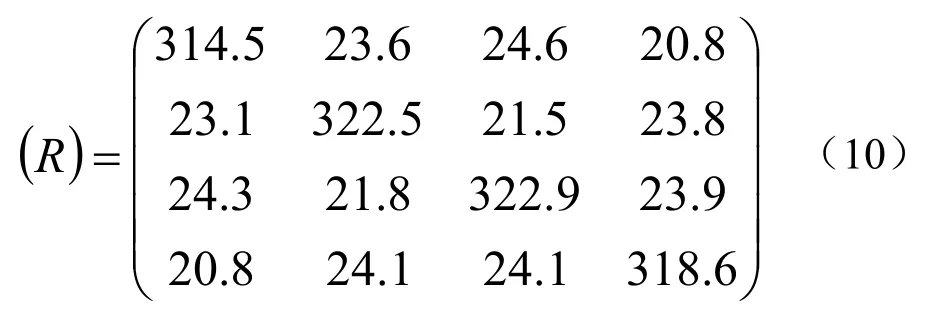

结合器件各芯片的加电功率和式(10)可得到表1。

表1 矩阵法得到的温差ΔTTab.1 ΔT with matrix test

从表1中可知在环境温度42~50 ℃时,施加功率 VCB=13 V,IC=20 mA,可以使得器件的结温TJ=150 ℃。

2.2 温度敏感参数法

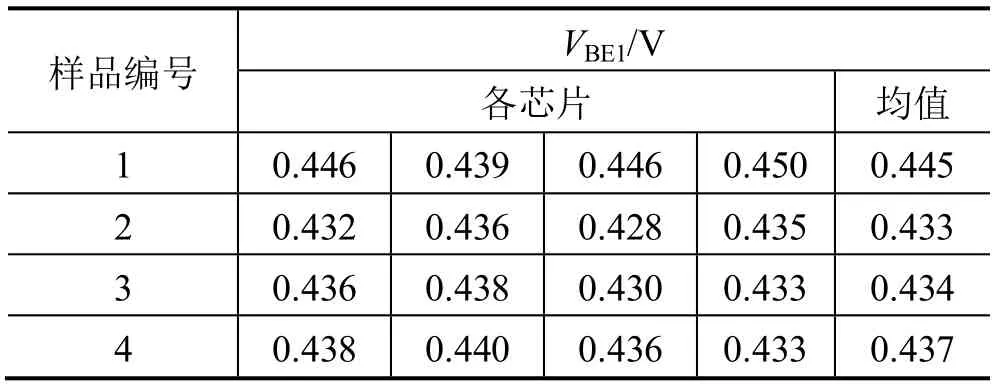

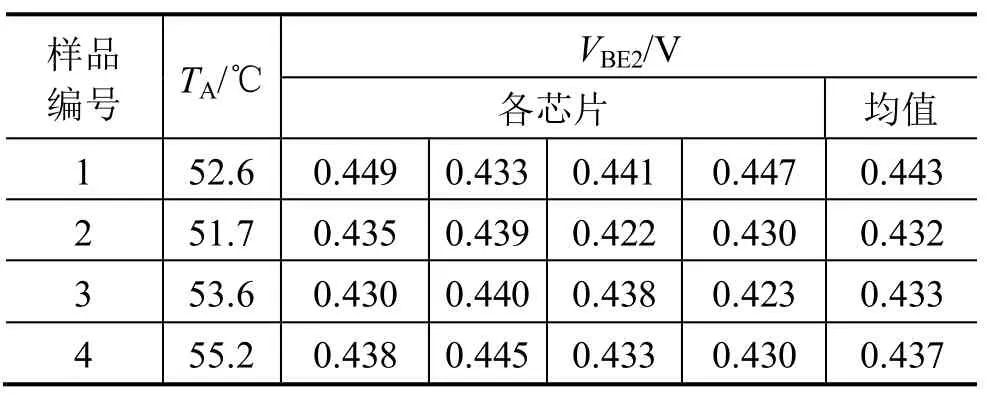

把器件安装在老炼板上,在不加电的情况下放入高温箱中,高温箱的温度稳定在150 ℃,此时器件的结温TJ即为高温箱温度150 ℃,依次测量器件四个芯片的正向压降VBE1,测试结果见表2。然后,把高温箱和器件的温度降低到35 ℃,使用备用电源分别为三个芯片加电(VCB=13 V,IC=20 mA),待稳定后采用 PHASE12热阻测试系统对剩下的一个芯片加电(VCB=13 V,IC=20 mA),并测量其正向压降VBE2。

其中正向压降 VBE2的测量主要利用了PHASE12热阻测试系统的快速测试切换功能。它可实现10 μs内在工作状态和测试状态之间切换,并准确测量芯片内部寄生二极管的结电压。

比较VBE2和VBE1的大小后调整高温箱的温度,再重复上述步骤测量VBE2,直到VBE2=VBE1。此刻高温箱的温度就是老炼时的环境温度TA。

根据上述步骤试验,并对比表2后得到表3,当TA=(53±2)℃时,芯片的 VBE2=VBE1,即器件的结温TJ=150℃。

表2 150 ℃下阵列管正向压降VBE1Tab.2 VBE1of transistor array at 150 ℃

表3 阵列管温敏参数法得到的TA及VBE2Tab.3 TAand VBE2of transistor array by using TSP

2.3 试验验证

为确定温敏参数法测得的结温是否准确,采用红外热像测试系统进行试验验证。在温度敏感参数法试验过程中,在器件的侧面固定一热电偶对器件的壳温(TC)进行监测,待器件VBE2=VBE1时记录器壳温(见表4)。

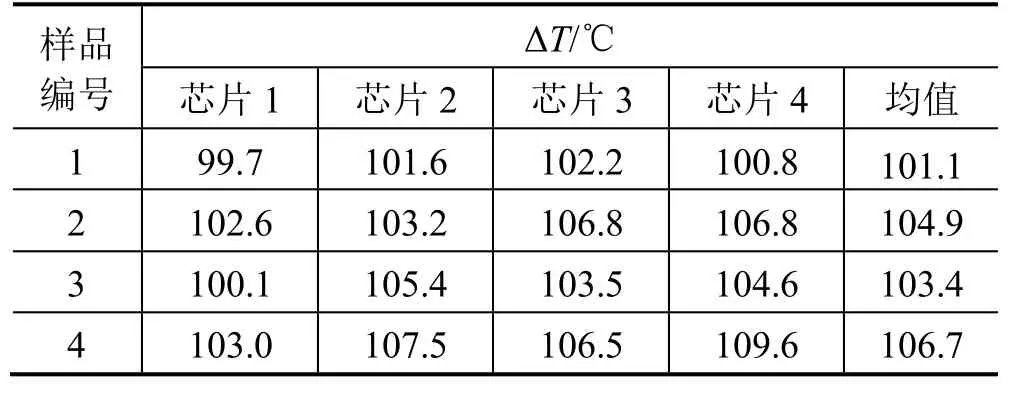

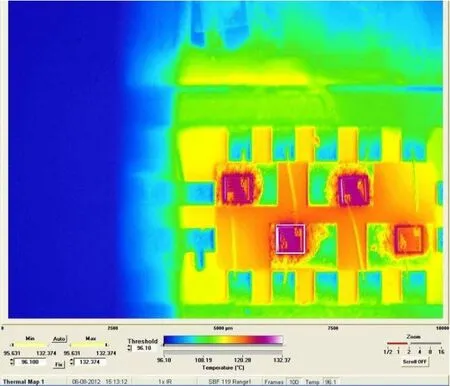

对开帽后器件的各芯片加电(VCB=13 V,IC=20 mA),通过红外热像测试系统的控温台控制器件结温使其平均结温达到125 ℃(器件内部温度分布见图2),此时,对监测点的壳温进行记录(见表4)。

从表4中可以看出红外热像法和温敏参数法得到的监测点壳温基本相同(红外热像法由于开帽使得部分热量通过热辐射和热对流散失,而使器件壳温偏低)。

表4 阵列管壳温对比Tab.4 Comparison of transistor array tube temperatures

图2 阵列管红外热像图Fig.2 IR thermal map of the transistor array

2.4 结果分析对比

矩阵热阻法获得的老炼试验条件综合考虑了阵列管内部各芯片之间的热耦合作用,从而在理论上可以准确获得目标芯片的结温。

但是在实际操作过程中,由于矩阵热阻法是通过热阻的测量换算获得器件的结温,而芯片之间的耦合热阻偏小,在测量过程中较易引入测量误差,并在结温换算时会把测量误差扩大,使得最终得到的结温不准。另外,矩阵热阻法由于需要对阵列管内部各芯片进行多次测量,从而在程序上较为复杂,将耗费大量人力物力。

温度敏感参数法是调节环境温度的同时,通过结电压 VBE测量器件正常工作状态下的结温,由于是一一对应的关系,其测量误差基本可以避免。该方法可以在老炼试验过程中对器件结电压 VBE进行实时监测,从而可以根据需求在老炼过程中有效地调整器件的结温。另外,红外热像法试验验证也证实了温敏参数法可实时监测结温。

3 结论

器件结温是否满足要求,会严重影响老炼的可信度和器件寿命预计的准确性。

本文重点针对较为复杂的晶体管阵列,通过理论和实验分析了矩阵热阻法和温度敏感参数法结温测量方法,并通过红外热像法进行了试验验证。最终得出:矩阵热阻法通过矩阵热阻可以综合考虑各芯片之间的热耦合作用,但由于需要多次测量耦合热阻,试验程序较为复杂,从而较易引入测量误差。温度敏感参数法操作简单且准确,可以实时监测阵列管正常工作状态下的结温,达到对其有效控制的目的。

[1] 国防科工委. GJB 128A——1997半导体分立器件试验方法 [S]. 北京: 国防科工委军标出版发行部, 1997.

[2] 国防科工委. GJB 33A-1997半导体分立器件总规范 [S].北京: 国防科工委军标出版发行部, 1997.

[3] 贾颖, 曾晨晖, 梁伟, 等. 稳态工作条件下功率晶体管结温的测量与控制 [J]. 封装测试技术, 2006, 36(1): 35-39.

[4] BAR C. Thermal management of air-and liquid-cooled multiple modules [J]. IEEE Trans Compon hybird manuf technol, 1987, 10(2): 62-65.

[5] SULLHAN R, MONAGHAN T, AGARWAL A. Thermal moduling and analysis of multiple modules [C]// Process of the 7th Annual IEEE Muti-chip Module Conference. NY, USA: IEEE, 1992: 18-22.

[6] JOINER B, ADAMS V. Measurement and simulation of junction to board thermal resistance and its application in thermal modeling [C]//Process of Semitherm. NY, USA: IEEE, 1999: 22-26.

[7] HARVEY I R, CLEMENS J M L. The Development of libraries of thermal models of electronics components for an integrated design environment [G]//Model Generation in Electronic Design. Germany: Springer, 2012: 63-89.

[8] MARSH S P. Direct extraction technique to derive the junction temperature of HBT’s under high self-heating bias conditions [J]. IEEE Trans Electron Devices, 2000, 47(2): 288-291.

[9] SHOCKLEY W. The theory of p-n junctions in semiconductors and p-n junction transistors [J]. Bell Syst Tech, 1949, 28: 435.

(编辑:陈渝生)

Junction temperature measurement method study for transistor array under burn-in

LYU Xianliang, MA Li, REN Xiang, SUN Ming

(Research Center of Foundational Product, China Electronics Standardization Institute, Beijing 100176, China)

According to PNP transistor array, two kinds of junction temperature measurement methods of matrix thermal resistance method and temperature sensitive parameter method (TSP) were analyzed and compared. The results show that the use of matrix thermal resistance method can consider the coupling effect of each chip. However, due to the complexity of the matrix thermal resistance test program, and the need of multiple conversions, it is easier to introduce errors. The temperature sensitive parameter method is simple and accurate, and can realize the junction temperature of the array tube in real time.

transistor array; burn-in; junction temperature; temperature sensitive parameter; matrix thermal resistance; IR thermal map

10.14106/j.cnki.1001-2028.2017.09.006

TN307

A

1001-2028(2017)09-0026-04

2017-06-23

吕贤亮

吕贤亮(1985-),男,浙江义乌人,工程师,主要从事电子元器件的可靠性检测、热性能及失效分析研究,E-mail: xianliang_001@163.com 。

时间:2017-08-28 11:08

http://kns.cnki.net/kcms/detail/51.1241.TN.20170828.1108.006.html