基于单稳态结构的时钟丢失检测电路设计

李月香

(中国电子科技集团公司第四十七研究所,沈阳110032)

基于单稳态结构的时钟丢失检测电路设计

李月香

(中国电子科技集团公司第四十七研究所,沈阳110032)

单片机可以看成是在时钟驱动下的时序逻辑电路,单片机工作过程中,所有的工作都是在时钟信号控制下进行的。针对MCU的硬件监控技术及复位系统,依据单稳态结构特性,设计一款时钟丢失检测电路。该电路采用电流源取代电阻的方式,实现单稳态电路的阻容结构。电路上电使能后,监测时钟上升沿,通过时钟上升沿的触发,使电路保持单稳态工作状态。采用0.25 μm CMOS工艺进行仿真,仿真结果显示,如果时钟保持在高电平或低电平的时间大于258.4μs时,单稳态电路将超时,并产生一个复位信号。此电路结构简单,便于集成在MCU复位系统,可对系统时钟进行丢失监测。

时钟丢失;单稳态;触发器;单片机;复位系统;时钟监测

1 引言

单片机可以看成是在时钟驱动下的时序逻辑电路,没有时钟,单片机无法执行指令,可以说时钟是单片机的心脏,它控制着单片机的工作节奏[1]。许多MCU芯片的硬件监控技术都包含上电复位或置位、欠压检测、“看门狗”复位等复位电路[2],很少有对MCU所使用的系统时钟进行检测复位。文中阐述一种基于单稳态结构的时钟丢失检测电路,针对系统时钟的丢失产生一个复位信号,用于集成在MCU复位系统,对系统时钟进行丢失监测。

2 单稳态原理简介

单稳态触发器具有如下工作特点:输出只有一个稳态,当有外触发脉冲作用时,它能从稳态转到暂稳态,但在暂稳态维持一段时间以后,能自动返回稳态,暂稳态维持的时间长短取决于电路本身的参数,与外触发脉冲信号的宽度无关[3]。由于具备这几个特点,单稳态触发器被广泛应用于数字系统中的整形、延迟以及定时等[4]。

目前,工程上应用最多的单稳态电路是NE555芯片[5],且单稳态的暂态通常靠RC电路的充、放电过程维持[6],这在用分立器件设计时是可以办到的。在集成电路设计时,大的电阻和电容将占据极大的版图面积[7],该电路采用一种电流源取代电阻的方式,设计一款具有单稳态特性的时钟丢失检查电路。

3 电路设计

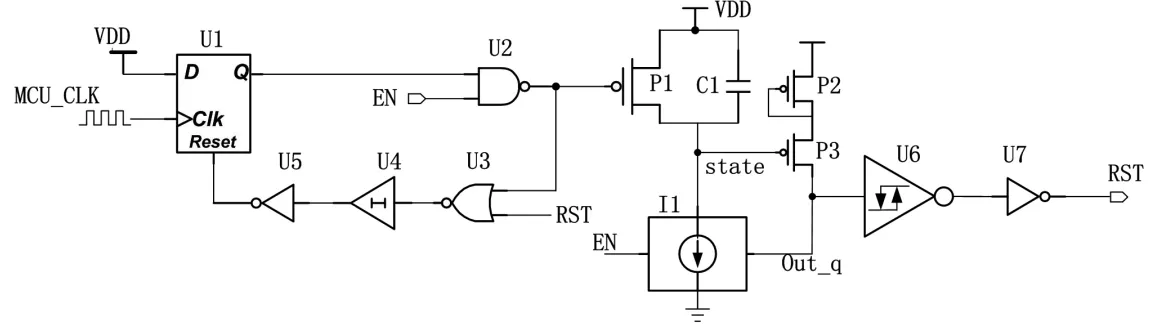

根据单稳态电路特性,设计一款时钟丢失监测电路,通过系统时钟上升沿的连续触发,使电路保持在暂态,如果系统时钟丢失,电路经过一段时间返回到稳态,产生复位信号。整体电路设计框图如图1所示:

图1 时钟丢失检测电路框图

U1为具有复位端的上升沿D触发器,其输入信号为VDD;U2为两输入与非门,其中一个输入端为电路的使能控制端EN;U4为延迟BUFFER单元,I1为电流源,U6为施密特反向器,其余单元为常见的逻辑门单元,整体电路工作状态如下:

状态1:丢失时钟检测关闭状态。此状态EN为0,使U2输出为1,P1关闭,I1不工作且输出端Out_q为0,RST端口输出为0。

状态2:丢失时钟检测开启状态。此状态EN为1,待时钟上升沿到来触发后,U1输出为1,U2输出为0,使P1开启,并开始为C1下极板充电,使state线网快速充电到VDD电平,保持P3关闭,RST输出为0。

状态3:触发器复位状态。EN为1,时钟上升沿触发后U1输出为1,U2输出为0,经过U4延迟时间T1后,U5输出0,使触发器U1复位并输出0,使U2输出为1,P1关闭。

通过状态2和状态3使P1开启的时间近似为T1,此期间state线保持VDD电平。P1关闭后,C1通过恒定电流I1放电,使state线网电压下降。

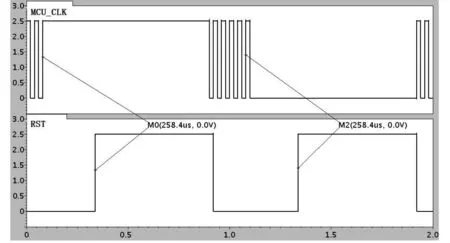

图2 时钟丢失检测仿真结果

状态4:丢失时钟检测复位状态。承接状态3,U2输出为1,经过U4延迟时间T1后,U5输出1使触发器U1退出复位。此时,如果时钟到来则进入状态2,如果时钟丢失,即时钟保持高电平或低电平不变,则U2保持输出1,C1保持放电,state线网电压持续下降,经过时间T2(T2>>T1),其电压下降到P3管阈值点,P3开启使Out_q电压大于U6输入高电平阈值,最终使RST输出为1,产生复位信号,提供MCU。

状态5:等待时钟触发状态,由于状态4中RST输出为1,信号经过U3—U5单元后输出为1,触发器复位关闭,此状态下,如果有时钟上升沿触发,进入状态2,使RST输出为0。

4 电路仿真

设计采用0.25 μm CMOS工艺,仿真软件Spectre进行仿真,图2为时钟丢失检测电路仿真结果图。

仿真时,考虑时钟丢失可能发生在高电平期间或低电平期间,因此对高、低电平都要进行监测。由图2可知,在时钟高电平丢失258.4μs时,RST产生复位信号,当时钟再次出现时,RST信号变为低电平,由于电路设计中U1采用的是时钟上升沿触发器,对于时钟在低电平丢失的监测时间为时钟最后一个上升沿到RST产生复位的时间,同样也为258.4μs。

5 结束语

根据MCU系统时钟的重要性及复位系统硬件的实现情况,依据单稳态电路工作特点[8],提出一款时钟丢失检测复位电路,此电路简单便于实现,可用于MCU复位系统,仿真结果显示,时钟保持在高电平或低电平的时间大于258.4μs,将会产生复位信号。

[1]周小军.MCU芯片的复位电路与多模式时钟系统设计[D].成都:电子科技大学,2007.Zhou Xiaojun.MCU Reset Circuit of Chip and Multimode Clock System Design[D].Chengdu:University of Electronic and Tech,2007.

[2]Jean J,Labrosse.MicroC/OS_II The Real-Time Kernel(Second Edition)[M].USA:CMP Books,2002.

[3]Fiorif P.S.A New Compact Temperature CompensatedCOMS Current Reference [J].IEEE Transaction on Circuits and Systems,2005(11):721-728.

[4]K.Itoh,K.Sasaki,Y.Nakagome.Trends in Low-Power Trigger Circuit Technologies[J].Proceedings of the IEEE,1994:83-90.

[5]何乐年,王忆.模拟集成电路设计与仿真[M].北京:科学出版社,2008.He Lenian,Wang Yi.Analog Integrated Circuit Design and Simulation[M].Bei Jing:Science Press,2008.

[6]K.Osada,etal,A 2ns Access 285MHz Two Port Cache Macro Using Double Global BitLine Pairs[J].IEEE ISSCC Digest of Technical Papers,1997:402-403.

[7]施凯青,夏晓娟,孙伟锋.一种单稳态倍频电路的实现[J].电子器件,2008,31(2):612-614.Shi Kaiqing,Xia Xiaojuan,Sun Weifeng.Realization of a Single Steady State Frequency Circuit[J].Electron Device,2008,31(2):612-614.

[8]朱小伟,汪东旭.大脉冲单稳态触发器的设计[J].微电子学,2002,32(3):225-227.Zhu Xiaowei,Wang Dongxu.Design of Large Pulse Single Steady State Trigger [J].Microelectronics,2002,32(3):225-227.

《微处理机》2018年度征订通知

《微处理机》期刊由中国电子科技集团公司第四十七研究所主办,是经国家科委批准的国家级工程技术刊物,并被《中国科技论文统计与分析》和《中国电子科技文献数据库》以及Internet网上的重要源数据检索刊物之一。自办,国内外公开发行。

主要刊载国内外最新的各种微处理器、微控制器、微机外围电路、专用电路的发展动态、设计、测试、开发与应用和微机系统与微机软件的开发以及微机在各领域中的应用等方面的科技论文。

本刊系双月刊,大16开本96页。全年定价:90.00元。

用户可直接向天津半导体杂志社订购(代号:8385),有漏订的用户可直接在我处订阅。

通讯地址:沈阳市皇姑区陵园街20号《微处理机》编辑部 邮编:110032

开 户:中国电子科技集团公司第四十七研究所

账 号:2100 1423 6010 5000 5715

开户银行:建行三台子支行

Design of the Missing Clock Detector Circuit Based on the Monostable Structure

Li Yuexiang

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

Single-chip microcontroller may be regarded as the sequential logic circuit driven by clock,in which all the work was conducted under the clock signal control.According to the hardware monitoring technology of MCU and reset system,a missing clock detector circuit based on the structural characteristics of monostable is designed,which uses the current source to replace the resistance,and realizes the resistance-capacitance structure of the monostable circuit.After the circuit being powered on,clock rising edge is monitored,which maintains a monostable working state by triggering the clock rising edge.Using the 0.25μm CMOS technology to the simulation,the simulation results show that if the time of the clock holding in high level or low level is greater than 258.4μs,the monostable circuit will time out,and generate a reset singal.The circuit structure is simple,which is easy to integrate in the MCU reset system and can monitor the system missing clock.

Missing Clock;Monostable;Tigger;Microcontroller;Reset system;Clock monitoring

10.3969/j.issn.1002-2279.2017.04.006

TN402

A

1002-2279-(2017)04-0020-03

李月香(1988—),女,辽宁省丹东市(东港)人,助理工程师,主研方向:集成电路技术研究。

2016-06-15