一种CMOS伪随机序列信号发生器的版图设计

保慧琴

(西北工业大学明德学院,陕西 西安,710124)

一种CMOS伪随机序列信号发生器的版图设计

保慧琴

(西北工业大学明德学院,陕西 西安,710124)

集成电路版图设计是实现集成电路制造必不可少的设计环节,版图设计的优劣直接关系到芯片的工作性能和制造成本。采用CMOS 2μm的λ设计规则,利用Tanner Pro软件设计了一种CMOS伪随机序列信号发生器。Tanner Pro软件是一套集成电路设计软件,利用S-edit完成伪随机序列信号发生器的原理图设计,利用L-edit完成伪随机序列信号发生器的版图设计,并通过T-spice软件进行仿真,仿真结果表明,所产生的伪随机序列信号循环长度为6,伪随机序列信号由D触发器的初始状态决定。

集成电路;版图;伪随机序列;版图设计规则;触发器;循环长度

1 引言

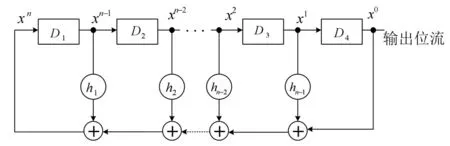

伪随机序列良好的随机性和接近于白噪声的相关函数,使其易于从信号或干扰中分离出来,广泛应用于密码学、通信、雷达、导航等多个领域,常用的产生伪随机序列信号的电路是线性反馈移位寄存器,所产生的序列只与寄存器的初始状态和反馈方式有关。n位线性反馈移位寄存器最多可以产生2n-1个状态。如图1所示。hi=1,表示接通反馈线;hi=0,表示断开反馈线。

图1 线性反馈移位寄存器

2 伪随机序列信号发生器电路设计

2.1 C M O S异或电路

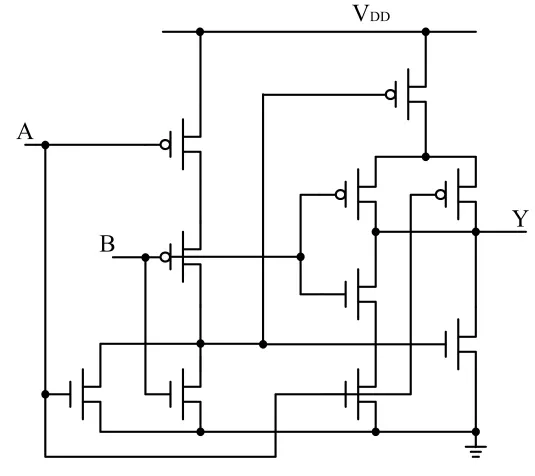

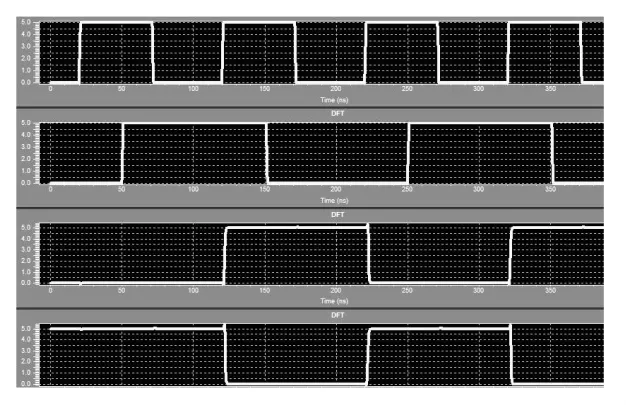

异或与同或电路都是应用广泛的逻辑单元,异或电路在两个输入变量相异时输出为高电平,即逻辑1。异或的功能可以表示为。静态CMOS逻辑电路中NMOS逻辑块和PMOS逻辑块具有互补性能,无论输入条件是什么,上拉开关网络和下拉开关网络都不会同时形成导通通路,因此,静态CMOS逻辑门电源和地之间没有直流通路,静态功耗非常小。如果用CMOS静态逻辑门实现异或电路,需要对上述逻辑表达式进行变换,变换成最终带“非”的逻辑形式,也就是用与或非逻辑实现。用静态CMOS逻辑门实现任意的组合逻辑,有多种不同的实现方案,对集成电路设计者来说要综合考虑电路的面积、速度和功耗等因素,选择最佳方案。对电路性能的比较要利用电路仿真工具。其中一种方案是,包含10个MOS晶体管。静态CMOS逻辑电路图如图2所示,T-spice仿真结果如图3所示,波形中信号从上到下依次为输入A、输入B和输出Y,从波形中可以看出,输入相同时输出为0,相异时输出为1。

图2 异或电路图

图3 仿真波形

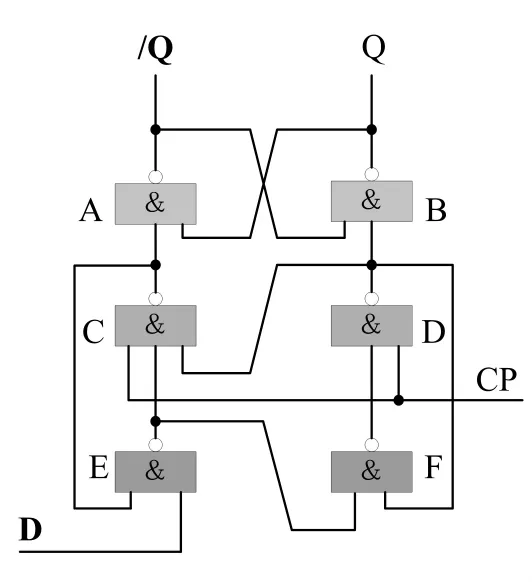

2.2 边沿D触发器

图4 边沿D触发器

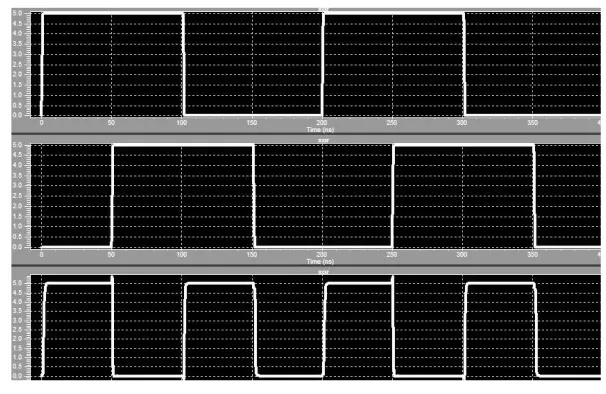

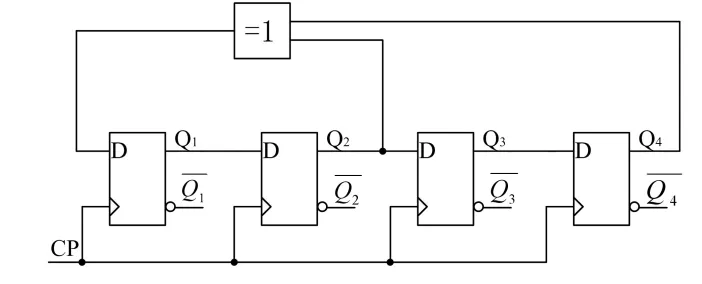

触发器是能存储数字信息的逻辑部件,它是一种时钟控制的记忆器件。边沿触发器的抗干扰能力强,工作可靠性高。图4所示为上升沿触发的CMOS维持-阻塞D触发器,由6个CMOS与非门交叉耦合而成,触发器的状态只能在时钟CP的上升沿发生变化,其他任何时刻触发器状态保持不变。D触发器的电路图如图4所示,仿真结果如图5所示,波形中信号从上到下依次为时钟CP、输入D和输出Q和Q。从波形中可以看出,输出在CP上升沿时刻才对输入信号响应,其他时刻输入信号变化不会引起触发器状态的变化。

图5 仿真波形

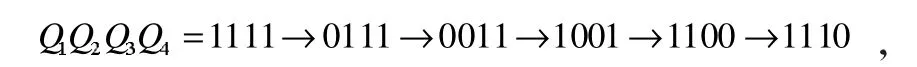

2.3 伪随机序列信号发生器

伪随机序列信号发生器由四个D触发器和一个异或门构成,反馈方式如图6所示。该伪随机序列信号发生器产生的序列信号和初始状态有关,不同的初始状态产生的序列信号不同。以初始状态为例,产生的序列信号长度为6,不是最大序列信号长度,6个序列信号分别为

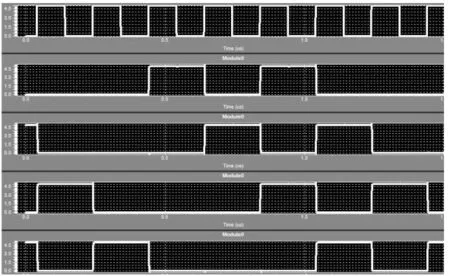

仿真结果如图7所示。波形中信号从上到下依次为CP、Q1、Q2、Q3和Q4,从波形中可以看出四个D触发器的输出在1111~1110这六个状态之间来回周期性循环。

图6 伪随机序列信号发生器

图7 仿真波形

3 伪随机序列信号发生器的版图设计

3.1 异或电路版图设计

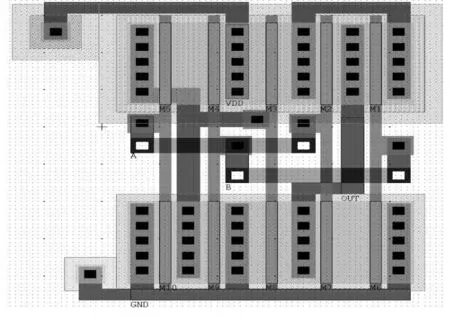

采用全定制版图设计方法,利用Tanner软件中的L-Edit工具进行版图设计,CMOS工艺规则为2μm的λ设计规则,利用源漏极共享原理,将晶体管原先独立的源漏区合并,这个合并的区域既可以是一个晶体管的源,同时也可以是另外一个晶体管的漏,合并至所有的晶体管之间端点组接成对。采用此类设计方法不仅消除了晶体管之间的空间,通过合并器件的相关部分可使空间更节省,最终设计出的版图面积为最小。异或电路的版图如图8所示。

图8 异或逻辑门版图

3.2 D触发器版图

上升沿D触发器由6个CMOS与非门构成,版图一共由10个绘图层套合而成,包括Metal1、Metal2、Via、Active contact、Poly contact、Poly、Active、N-select、P-selsct、N-well。考虑金属连接造成接触电阻的影响,为了限制总的电阻,采用设计规则允许的尽可能多的接触孔,将接触孔设计为并联,n个接触等效电阻为R/n。并且采用5个接触孔并联的结构减小接触电阻。边沿D触发器版图如图9所示。

图9 边沿D触发器版图

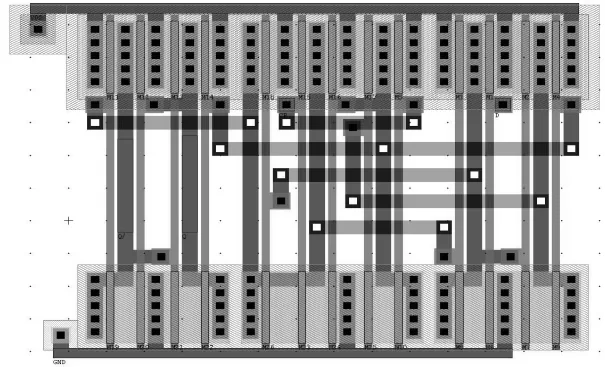

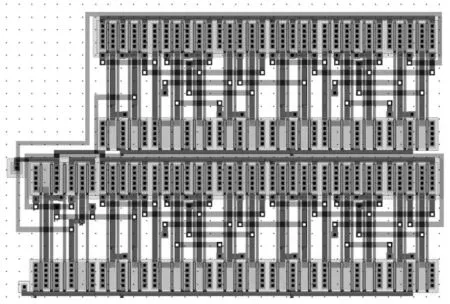

3.3 伪随机序列信号发生器版图

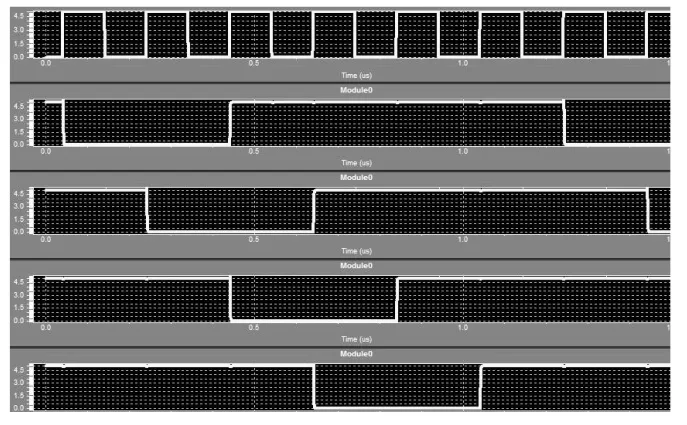

将4个D触发器和1个异或门的版图进行布局并完成级联。为了防止体硅工艺中闩锁效应的发生(即NMOS的有源区、P衬底、N阱以及PMOS的有源区构成PNPN结构,若寄生三极管导通会使电流增加,导致VDD和VSS短路,通常会破坏芯片,严重时会导致电路失效),在版图设计过程中,将NMOS晶体管的P衬底通过P衬底接触连接到VSS,将PMOS晶体管的N衬底通过衬底接触连接到VDD。伪随机序列信号发生器的版图如图10所示,仿真结果如图11所示,波形中信号从上到下依次为CP、Q1、Q2、Q3和Q4,从波形中可以看出四个D触发器的输出在0101-0010-0001-1000-0100-1010这六个状态之间来回周期性循环。

图10 伪随机序列信号发生器版图

图11 伪随机序列信号发生器版图仿真结果

4 结束语

集成电路版图设计在集成电路设计流程中位于后端,它是集成电路设计的最终目标。版图设计的优劣直接关系到芯片的工作速度和面积,因此版图设计在集成电路设计中起着非常重要的作用。伪随机

The Layout Design of a CMOS Pseudo-random Sequence Signal Generator

Bao Huiqin

(Northwestern Polytechnical University Ming De College,Xi’an,710124)

IC layout design is the indispensable design link of integrated circuit manufacturing,the quality of layout design are directly related to the working performance and manufacturing cost of chip.By using CMOS 2μm λ design rules and Tanner Pro software,a CMOS Pseudo-random sequence signal generator is designed.Tanner Pro software is a set of integrated circuit design software,using S-edit to complete the schematic diagram design,and using L-edit to complete the Layout design.By the T-spice software,simulation is performed and its results show that the cycle length of this Pseudo-random sequence signal generator is six,and the sequence signal is determined by the initial state of D flip-flops.

Integrated circuit;Layout;Pseudo-random sequence;Layout design rules;Flip-flop;Cycle length

10.3969/j.issn.1002-2279.2017.04.003

TN79

A

1002-2279-(2017)07-0004-04

保慧琴(1986—),女,青海省西宁市人,助教,硕士研究生,主研方向:集成电路版图。

2017-02-28