基于RF SOI CMOS工艺高线性低功耗LNA设计

何 全,陈忠学,2,章国豪

(1.广东工业大学 广东 广州 510006;2.广州钧衡微电子科技有限公司 广东 广州 510006)

基于RF SOI CMOS工艺高线性低功耗LNA设计

何 全1,陈忠学1,2,章国豪1

(1.广东工业大学 广东 广州 510006;2.广州钧衡微电子科技有限公司 广东 广州 510006)

基于IBM公司的0.18 μm RF SOI CMOS工艺,设计了一款应用于S波段的高线性低功耗低噪声放大器。在传统共源共栅拓扑结构的基础上,本文提出使用有源偏置电路、级间匹配网络和并联反馈结构,使设计的放大器具有噪声低、线性度高和功耗小等特点。仿真结果表明,该放大器在2.3~2.7 GHz频段,电源电压为 1.8 V,功耗为 9.8 mW 的条件下,噪声系数小于 0.8 dB,增益大于 14 dB,输入回波损耗和输出回波损耗均大于10 dB,隔离度大于27 dB,输入三阶交调截取点大于15 dBm,满足无线基础架构接收器对低噪声放大器的所有性能要求。

SOI;低噪声放大器;高线性;低功耗;S波段

近年来,随着手持智能终端的不断普及和各种移动应用的蓬勃发展,移动数据流量呈现爆炸式增长,数据传输率也不断提升。为了应对巨大的移动数据业务和高速率数据传输率的要求,目前应用于无线通信的频谱资源已经进入到S波段(2~4 GHz),如无线局域网 (WLAN) 和移动通信(LTE,WCDMA,TD-SCDMA)等[1]。

为了支持各种无线通信标准和众多移动应用,这就不可避免地给手持智能终端提出更加严格的要求,特别是射频前端组件。低噪声放大器(LNA)是射频前端无线基础架构接收器的一个关键模块[2],它的性能直接影响并决定着接收器的灵敏度和动态范围,必须满足低噪声、高线性度和无条件稳定等关键要求[3-4]。

目前,在LNA的诸多实现方案中,源简并共源共栅结构应用的最多,虽然具备高带宽、高增益和高反向隔离度等特点,但线性度低。采用的绝大多数都是GaAs pHEMT和CMOS工艺,虽然工艺成熟,但噪声大、功耗高,不利于手持智能终端的续航[5]。针对上述问题,文中提出使用SOI CMOS工艺,通过添加反馈网络和漏端到接地之间连接串并联CR网络,能有效改善传统低噪声放大器中线性度低、噪声大和功耗高等缺陷。

1 低噪声放大器设计

1.1 器件工艺选择

SOI(Silicon-On-Insulator绝缘体上硅) CMOS是最近十几年才出现的一种新型半导体原材料[6],与传统的Bulk CMOS器件相比,SOI CMOS在器件和衬底之间加入了一层绝缘埋氧层,如图1所示。绝缘埋氧层不仅能有效减轻体效应,消除Latch-Up(闩锁效应),而且还能在一定程度上抑制Bulk CMOS器件的寄生效应,除此之外,SOI CMOS器件还具有导通电压低,噪声小和集成度高等优点[7]。

LNA的噪声系数和增益受到ft,fmax和FET栅极电阻的影响,而SOI CMOS提供了一个极低的电容器件,因此有助于ft和fmax。在许多领域,SOI CMOS已成为蜂窝和Wi-Fi开关的适用技术。SOI CMOS允许优化的开关和LNA在前端模块中进行集成,从而改善LNA的性能。为了解决复杂的多频带和多标准设计,射频前端组件要求进一步集成多个射频单元(如功率放大器、低噪声放大器和天线开关)以满足高线性和低功耗等要求,SOI CMOS无疑是最佳的工艺选择[8]。

图1 SOI CMOS晶体管截面图

1.2 拓扑结构选择

共源共栅拓扑结构不仅具有噪声系数低和线性度好等优点,而且还可以减小晶体管的Miller效应和有限输出阻抗所带来的影响,具备高带宽、高增益和高反向隔离度等特点[9]。

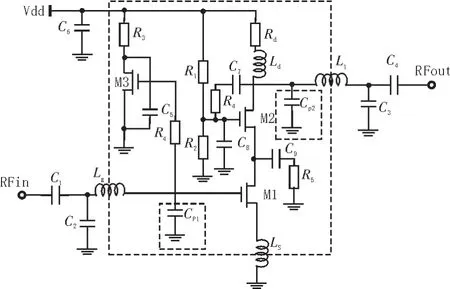

区别于传统的源简并共源共栅拓扑结构,本文改进的低噪声放大器通过采用有源偏置电路、级间匹配网络和并联反馈结构来实现高线性、低噪声和低功耗等性能要求。具体拓扑结构如图2所示,其中虚线方部分采用RF SOI CMOS工艺实现,而虚线方框以外的部分则是通过多层基板、绑定线和SMT元件实现。

晶体管M1和M2构成低噪声放大器共源共栅的主体结构。晶体管M3与M1构成电流镜结构,为放大管M1提供稳定的偏置电流,使其不随工艺、温度和电源电压的变化而变化[10]。电阻R1和R2构成电阻分压式偏置网络给晶体管M2提供稳定的栅压偏置,通过选择合适的偏置电阻阻值,可以使线性度达到最佳。漏端到接地之间连接的串并联CR级间匹配网络,在低频时可以用来充当高阻抗,而在高频时则可以用来充当分流电阻,有利于器件的稳定,同时对线性度也有一定的影响。器件输出和输入之间采用并联反馈,有利于IP3、增益和回波损耗的调整,但会降低噪声系数,通常只用于共栅极设计[1]。

图2 低噪声放大器拓扑结构

1.3 噪声系数和输入匹配

噪声系数和输入回波损耗是低噪声放大器设计时需要考虑的主要因素。共源共栅设计的共源级主要是为了获得最佳的噪声系数、输入阻抗匹配和目标漏源电流下的P1dB,而共栅极则是在不影响其他性能指标的前提下获得最佳的IP3、输出阻抗匹配和P1dB。

图3 简化的小信号等效模型

低噪声放大器的简化小信号等效模型如图3所示。由小信号等效模型可得到噪声系数表达式为[11]

由此可见,器件的噪声不仅与晶体管内部的噪声有关,而且还与外部的输入匹配网络和电感Ls的Q值有关。通过采用合适的晶体管宽度和多晶体管并联等技术,可以使内部噪声达到最小;通过采用高Q值的外部元件,可以使外部噪声达到最小。在综合考虑噪声系数、增益和线性度之后,选取晶体管M1和 M2 的宽度为 240 μm(80 fingers×3 μm)。

图4显示了2.5 GHz时共源共栅拓扑结构在Smith圆图中的噪声系数圆和可用增益圆,考虑SMT元件的寄生效应和传输线损耗,在0.6 dB噪声圆和16 dB增益圆内选取源阻抗Zs=102+j*83 Ω,作为噪声、增益和输入回波损耗之间的权衡点。输入匹配网络选用高Q元件C1、C2和Lg实现,以获取最佳的噪声系数,C1还用于直流阻隔。

图4 可用增益和噪声系数圆

1.4 线性度和输出匹配

除了噪声系数和输入匹配之外,线性度也是低噪声放大器的一个重要考虑因素。低噪声放大器要在存在很强干扰情况下接收比较弱的信号时保持线性工作,否则就会使接收器的灵敏度降低并且产生交叉调制,严重影响接收器的性能。在低噪声放大器中,普遍采用三阶截取点(IP3)来度量线性度[2]。

输入匹配网络对噪声系数有很大的影响,而输出匹配网络对噪声的影响可以忽略不计。所以,在输出匹配里面主要考虑的是增益。当源与阻抗ZS=102+j*83 Ω完成输入匹配后,IP3将取决于输出匹配,与反馈网络、分压式偏置网络和级间匹配网络也有一定的影响。放大器的输出负载可以通过负载牵引技术扫描得到,输出匹配网络由 Ld、Rd、L1、C3和直流阻隔电容C4完成。

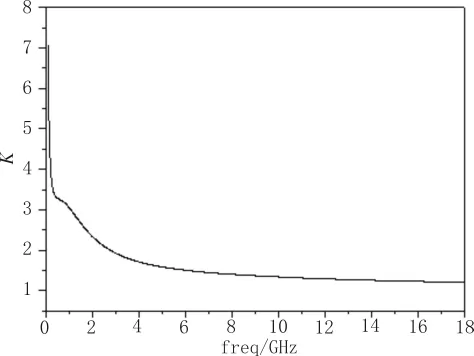

1.5 稳定性

绝对稳定性是指放大器在任何输入和输出条件下都不会产生振荡,它是低噪声放大器最重要的要求之一。低噪声放大器要在最高达18 GHz的频率下能够保持绝对稳定工作,而且每一级也要满足绝对稳定工作的要求,包括所有条件下的所有外部元件和偏置。在此频率范围内的多数情况下,低噪声、高增益的器件往往会变得很不稳定。

为了稳定器件同时满足这些要求,必须采用稳定性设计技术。本文通过加入源级反馈电感Ls、漏级到接地之间的串并联电阻CR网络和共栅极输出与输入之间的RC并联反馈,可以实现绝对稳定工作。

2 低噪声放大器仿真结果及其分析

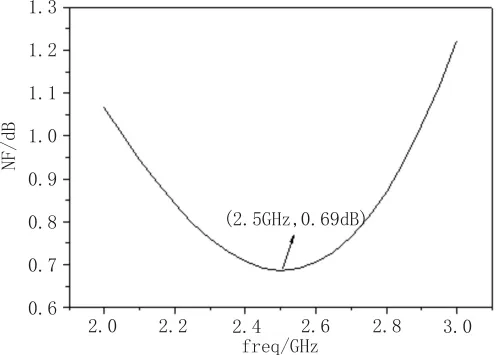

文中所设计的低噪声放大器是基于IBM公司的0.18 μm RF SOI CMOS工艺实现,并在ADS2011仿真平台下进行设计、优化和仿真。在综合考虑输入输出匹配网络、级间匹配网络、SMD元件寄生阻抗、传输线损耗、绑定线和晶体管输入输出寄生电容的影响后,所得到的噪声系数和S参数仿真结果如图5,图6所示。

图5 噪声系数

图6 S参数

仿真结果显示,在电源电压为1.8V,功耗为9.8 mW的条件下,噪声系数小于0.8 dB,小信号增益大于14 dB,输入输出回波损耗均大于10 dBm,隔离度大于27 dB。取得了不错的噪声性能,而且小信号增益大,输入输出匹配良好。

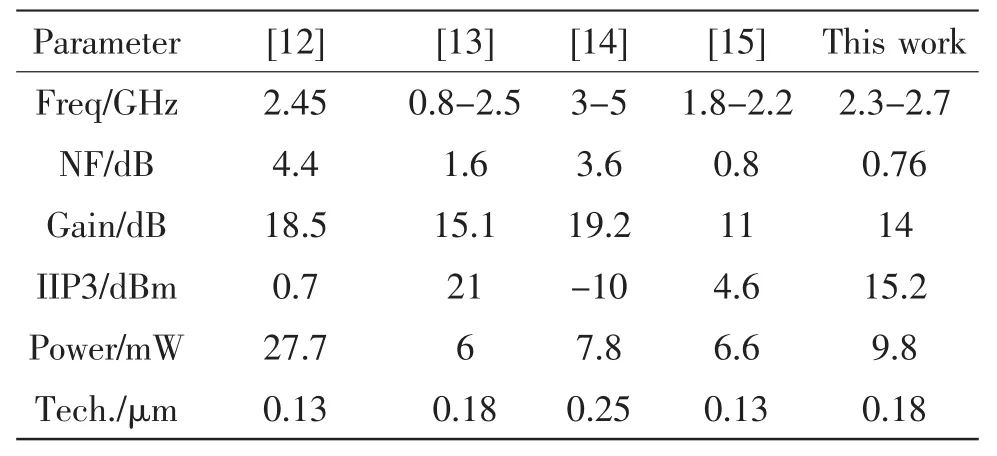

线性度的衡量是采用仿真模型估算在工作频率下的两个相隔5 MHz音调的IP3,使每个音调的输入功率为-20 dBm。仿真模型估算结果如图7所示,在 2.3~2.7 GHz 频段内,IIP3 大于 15 dBm,OIP3 大于30 dBm,实现了高线性度。放大器的稳定系数如图8所示,在高达18 GHz内均大于1,符合绝对稳定的工作条件。[12-13]增益和线性度都不错,但噪声系数略大。本文的噪声系数和功耗都比较低,线性度较好,增益也较高。(文献[12-13]为 Bulk CMOS工艺,文献[14-15]为SOI CMOS工艺)

图7 线性度

图8 稳定系数

表1 性能比较

3 结 论

基于 IBM 公司 0.18 μm RF SOI CMOS 工艺设计了一款应用于S波段的低噪声放大器。仿真结果表明,该放大器在 2.3~2.7 GHz频段,电源电压为 1.8 V,功耗为9.8 mW的条件下,噪声系数小于0.8 dB,增益大于14 dB,输入三阶交调截取点大于15 dBm,满足无线基础架构接收器对低噪声放大器的要求。同时,该设计也表明RF SOI CMOS作为一种新兴工艺,有着比传统Bulk CMOS更加优越的性能,可以很好地应用于射频前端组件中,以满足高线性和低功耗等要求。

[1]张胜标,张志浩,章国豪.用于S波段的高线性低噪声放大器[J].电子器件,2016,39(1):57-61.

[2]Thomas H.Lee.CMOS射频集成电路设计 [M].2版.余志平,周润德,等译.北京:电子工业出版社,2012.

[3]高向可.C波段低噪声放大器的仿真设计[J].电子设计工程,2011,19(22):94-97.

[4]方方.基于ADS的C波段的低噪声放大器仿真设计研究[J].电子设计工程,2013,21(1):67-69.

[5]Hassan M,Olson C,Kovac D,et al.An Envelope-Tracking CMOS-SOS Power Amplifier With 50%Overall PAE and 29.3 dBm Output Power for LTE Applications [C]// 2012 IEEE Compound Semiconductor Integrated Circuit Sym-posium(CSICS).La Jolla,CA:IEEE,2012:14-17.

[6]林俊明,郑耀华,郑瑞青,等.应用于移动手机的SOI线性射频功率放大器的设计 [J].电子技术应用,2015,41[9]:60-62.

[7]Madan A,Mcpartlin M J,Masse C,et al.A 5 GHz 0.95 dB NF Highly Linear Cascode Floating-Body LNA in 180 nm SOI CMOS Technology[J].IEEE Microwave and Wireless Components Letters,2012,22(4):200-20.

[8]郑直.SOI功率器件的新结构研究[D].成都:电子科技大学,2013.

[9]Moezzi M,Bakhtiar S.Wideband LNA Using Active Inductor With Multiple Feed-Forward Noise Reduction Paths[J].IEEE Transactions on Microwave Theory and Techniques,2012,60 (4):1069-1078.

[10]刘祖华,刘斌,黄亮,等.应用于WLAN的低噪声放大器及射频前段的设计 [J].电子技术应用,2014,40(1):38-40.

[11]Razavi B.RF Microelectronics[M].New York:Prentice Hall,2011.

[12]Arshad S,Ramzan R,Zafar F,et al.Highly linear inductively degenerated 0.13μm CMOS LNA using FDC technique [C]//2014 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS).Ishigaki:IEEE,2014:225-228.

[13]Thacker M B,Awakhare M,Khobragade R H,et al.Multi-Standard Highly Linear CMOS LNA[C]//2014 International conference on Electronic System,Signal Processing and Computing Technologies.Nagpur:IEEE,2014:63-68.

[14]IJI A,Xi Zhu,Heimlich M.A 3-5 GHz LNA in 0.25μm SOICMOS ProcessforImplantable WBANs[C]//2012 IEEE 55th International Midwest Symposium on Circuits and Systems(MWSCAS).Boise ID,IEEE,2012:766-769.

[15]Hossein N,Miles S,Naveen Y,et al.A 0.8dB NF,4.6dBm IIP3,4.6dB IIP3,1.8-2.2GHz,Low-Power LNA in 130 nm RF SOI CMOS Technology[C]//Wireless and Microwave Circuits and Systems (WMCS).Waco,TX:IEEE,2015:1-4.

A high-linearity and low-power LNA in RF SOI CMOS technology

HE Quan1,CHEN Zhong-xue1,2,ZHANG Guo-hao1

(1.Guangdong University of Technology,Guangzhou 510006,China; 2.Guangzhou Junheng Micro-Electrics Tech Ltd.,Guangzhou 510006,China )

A high-linearity and low-power low noise amplifier was implemented in IBM's 0.18 μm RF SOI CMOS technology for S band application.Based on conventional cascode topological structure,this improved LNA achieves high linearity,low noise and low power while using an active bias circuit combined with inter-stage matching network and a parallel feedback structure.The SOI CMOS LNA has a simulated noise figure of less than 0.8 dB,gain of greater than 14 dB,input return loss and output return loss of more than 10 dB,reverse isolation of more than 27 dB,input third order intercept point of more than 15 dBm over 2.3 to 2.7 GHz under the conditions that the power supply voltage is 1.8 V and the power dissipation is 9.8 mW,satisfying all the need for LNA in wireless receivers.

SOI; low noise amplifier; high-linearity; low-power; S band

TN722.3

A

1674-6236(2017)17-0111-04

2016-07-25稿件编号:201607175

广东省战略新兴产业重大专项(2012A010701002)

何 全(1990—),男,湖北荆州人,硕士研究生。研究方向:射频与微波集成电路设计。