基于FPGA的DDS多功能信号发生器的设计

黄玉健,黄永庆

(1.2.梧州学院 图像处理与智能信息系统广西高校重点实验室,广西 梧州 543002)

基于FPGA的DDS多功能信号发生器的设计

黄玉健1,黄永庆2

(1.2.梧州学院 图像处理与智能信息系统广西高校重点实验室,广西 梧州 543002)

多功能信号发生器作为一种基本电子设备在教学、电子信息工程和科研等领域,都有着广泛的使用。该文以直接数字频率合成技术(DDS)为核心,描述了基于FPGA的DDS多功能信号发生器的原理结构和设计方法,重点阐述了FPGA的DDS内核设计方法。设计结果表明,与普通的信号发生器相比,基于FPGA的DDS为核心技术的信号发生器能够灵活产生更加精准、更加稳定和更宽频率范围的正弦波、方波、三角波和锯齿波等信号。

多功能信号发生器; DDS; FPGA

0引言

信号发生器作为一种基本频率源发生器无论是在教学、电子信息工程和科研等领域,都有着广泛的使用。随着通信技术、卫星定位系统、精密机械控制以及航空航天测控等领域对测控技术要求的不断提高,对信号发生器的稳定度、精确度和频率带宽等要求越来越高,而传统振荡器由于产生的频率信号精度不高、太单一或者只能在比较小范围内调节频率而不能满足要求[1]。 利用频率合成技术就是解决该问题的最好方法之一。直接数字频率合成技术DDS(Direct Digital Synthesizer)是一种新型的频率合成技术,它是把一系列数字信号通过D/A 转换器转换为模拟信号的合成技术[1]。DDS能够在频率带宽比较宽的范围内实现比较高的频率分辨率,可以实现快速频率切换,并且在频率改变时能够保持相位的连续,比较容易实现频率、相位和幅度的数控调制[2]。

利用专门DDS芯片设计产生信号源也是设计信号发生器的一种方法,该方法优点是输出正弦信号频率范围大、波形好;缺点是DDS芯片的ROM里一般都只存储正弦波,产生其他波形需要加上一些外围电路的方式获得,产生波形速度受到很大的限制,频率带宽受影响严重,导致使用不够灵活[3]。为了增加灵活性,使产生的各种波形都能在频率带宽比较宽的范围内实现比较高的频率分辨率,实现快速精确的频率、相位和幅度的数字化控制,可以采用FPGA实现DDS技术,把DDS中的ROM改用SRAM,SRAM作为一个波形抽样数据的公共存储器,事先存储多种波形数据,只要改变存储波形的数据以及输入的频率字,就可以灵活地产生多种波形不同频率的信号。

本文的组织结构如下:第2节对FPGA的DDS信号发生器原理进行理论分析;第3节应用FPGA内部丰富的逻辑电路,按照DDS电路的结构特点,构造出相应的电路,并进行仿真和输出波形分析。第4节对本文进行总结。

1DDS基本原理[2]

1.1 DDS理论原理

对于正弦波信号来说,可以用公式(1)进行描述:

F=Asinθ=Asin(2πft)

(1)

公式(1)中,F是正弦信号波形;A是正弦波信号的幅度,f是正弦波信号的频率。需要注意的是,公式(1)中的时间t是连续的。为了实现数字化设计,必须对公式(1)进行离散化处理,方法是用基准时钟clko进行抽样。

根据公式(1),正弦波信号的相位θ为:

θ=2πft

(2)

因此,在一个基准时钟clko周期内Tclko,相位θ的变化量Δθ为:

(3)

现在对Δθ进行数字量化,对公式(3),把2π分成2N等份,这样Δθ可以用量化值BΔθ来表达为:

(4)

公式(4)中BΔθ为整数。联立公式(3),得:

(5)

这样,正弦波信号发生器的输出可以描述为:

(6)

公式(6)中θk-1指clko前一个周期的相位值。根据公式(4),可以得到:

(7)

从推导可以知道,正弦波信号的当前相位值可以通过对相位的量化值进行累加运算的方法得到,信号的输出频率f由相位增量量化值BΔθ决定,从公式(5)可知,两者是简单的线性关系。

DDS信号发生器就是根据上述理论原理设计的,下面根据上述理论原理进行具体的设计分析。

1.2 DDS多功能信号发生器设计原理

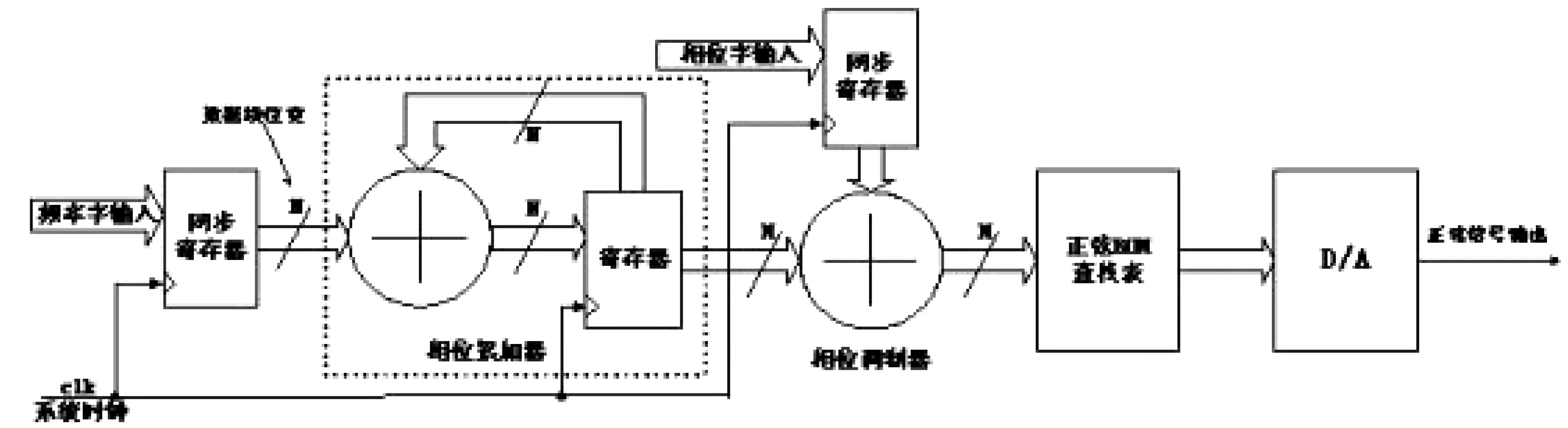

图1 DDS结构原理图

图1是根据上述DDS理论原理而设计出的数控频率合成器的结构原理图。它的几个主要构成部分为:相位累加器、相位调制器、正弦ROM查找表以及DA转换器。这样输出得到的是正弦波,当需要输出方波、三角波和锯齿波时,只需把正弦ROM查找表中的数据换成相应波形ROM查找表就可以了。后面的设计分析均是以生成正弦波为例。图1 的数字部分相位累加器、相位调制器、正弦ROM查找表具有数控频率合成功能,所以又称为NCO(Numerically Controlled Oscillators)。

相位累加器的功能是完成相位累加功能,是DDS的核心。它的输入是相位增量BΔθ,由式(5)可知,输出频率f与BΔθ相位增量之间是线性关系,当基准时钟fclko刚好等于2N时,相位增量BΔθ就等于输出频率f。相位累加器的输入就是频率字经过同步寄存器后的输出,同步寄存器的功能是当频率字改变时相位累加器的正常工作不至于被干扰。 相位调制器的作用是对相位累加器的输出信号进行相位调制,其中相位字输入到相位调制器之前也要先经过同步寄存器保持。一般而言,相位字输入的数据宽度M通常远小于频率字输入数据宽度N。

正弦波ROM查找表的功能是完成一个周期离散正弦数据查表的转换,相位调制器的输出就是ROM的地址值,根据地址值找到相应的离散正弦数据,输出一个周期的离散正弦波数据后经D/A转换器转换成模拟信号,就得到最终的正弦波信号。

下面计算DDS结构中常用参数:

① 由DDS原理推导公式(5)可以得出输出频率为

(8)

公式(8)中,fclko是基准时钟的频率,N是相位累加器的数据位宽度,BΔθ是频率控制字,也称频率输入字,在硬件设定已经确定,也就是fclko和N都设计定型了的情况下,输出频率值就由当时输入的BΔθ来确定。需要注意的是,频率控制字的数据位宽度也是N,即BΔθ的最大值就是二进制N个1,此时输出频率值达到最大值,与基准频率相等,即fmax=fclko。

② DDS系统的频率分辨率Δf,即俗称输出频率最小步进值,就是频率控制字BΔθ步进一个最小间隔,亦即BΔθ=1对应的频率输出值。由公式(8)得到:

(9)

由公式(8)和公式(9)可知,只要基准频率fclko足够高频足够稳定,同时N足够大,利用DDS技术,可以实现输出任意频率和任意精度的正弦信号波形[4],而同在FPAG中利用锁相环技术,fclko实现高频高稳定基准时钟功能是很容易的。在具体设计中,只要更改ROM查找表中的正弦波形数据为其他波形数据,就可以实现其他的波形信号输出。这就是DDS多功能信号发生器的设计原理。

2基于FPGA的DDS应用设计及仿真分析

2.1基于FPGA的DDS应用设计[2]

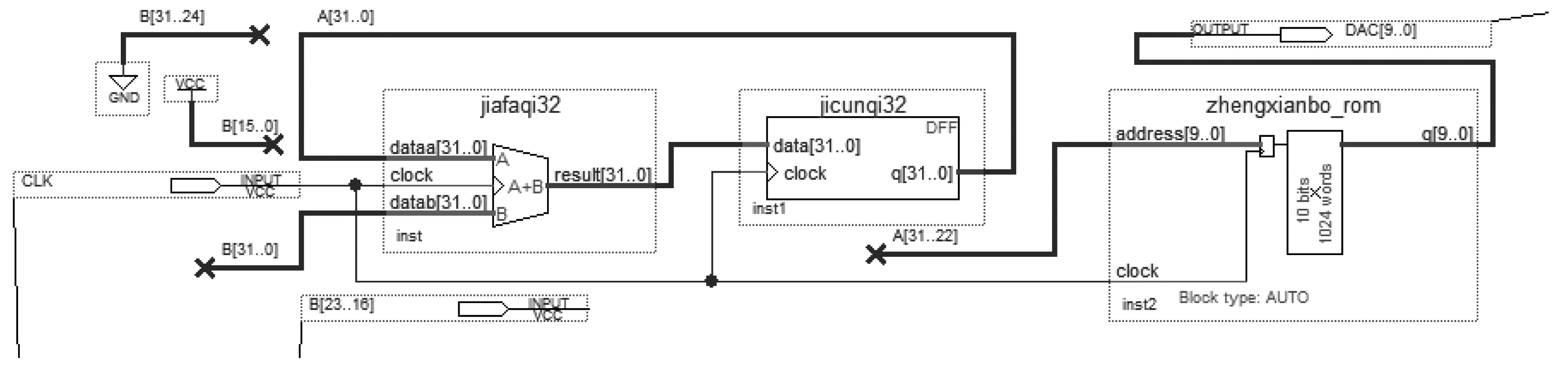

图2是根据图1 DDS结构原理图而设计的DDS正弦波信号发生器顶层电路原理图,图中相位累加器的数据位宽度N=32。下面对主要模块和接口分别进行介绍。

① 32位加法器模块jiafaqi32,由宏模块LPM_ADD_SUB设计而成。为保证此加法器模块具有比较高的运算速度和输入数据稳定性,特意设置了2阶流水线结构。

② 32位寄存器模块jicunqi32,由宏模块LPM_FF设计而成。它和加法器模块jiafaqi32一起构成数据位宽度N为32的相位累加器。因为该设计中正弦波查找表ROM的地址线是10位,因此把高10位A[31..22]设置为正弦波查找表ROM的地址。

③ 正弦波产生模块zhengxianbo_rom,由宏模块ROM:1-PORT设计得到。考虑输出波形质量和硬件配置,设置地址线为10位,亦即,一个周期的离散正弦波数据为210=1024个;数据线位宽也设置为10位,亦即,每个波形数据有10位。需要注意,该模块的输出波形是离散的正弦波型,需要接一个10位高速D/A转换器才可以得到连续的模拟正弦波信号。

④ 频率控制字输入接口B[23..16]。设计的频率控制字是32位的,这里暂时把B[31..24]输入预先设置成0,B[15..0]输入预先设置成1,目的是为了更好地仿真和实验,这样需要输入的B[23..16]8位数据就容易从实验箱或实验板上输入得到。

由公式(8)可以得到输出正弦波信号DAC[9..0]的频率f与频率控制字B[31..0]的关系为:

(10)

公式(10)中fclko是输入基准时钟CLK的频率,在本设计里fclko=50MHz。根据公式(9)可得输出频率分辨率Δf最小为0.012Hz,频率字每变化56H,输出频率变化1Hz。若不考虑DAC的速度限制,本设计理论上输出信号频率最高为50MHz。如果需要更高的频率,可以通过接入锁相环并配合高速DAC的方式得到。

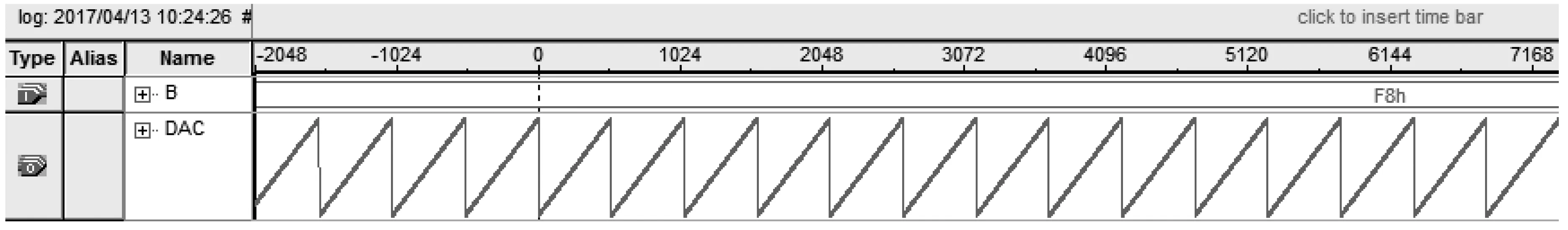

2.2 电路仿真及输出信号波形分析

图3是图2 DDS正弦波信号发生器顶层电路原理图的输入输出仿真图。这个图只是截取了局部的输入输出仿真数据,通过该图能看出DDS信号发生器频率控制字输入B[23..16]与输出信号DAC[9..0]的关系:随着B[23..16]的加大,输出信号DAC[9..0]的数据输出速度跟着提高。图3中当B[23..16]分别等于1DH、66H、F8H时,DAC[9..0]的数据输出速度明显不同,输入F8H时的输出信号频率明显高于输入1DH时的输出信号频率。

下页的图4和图5分别是DDS信号发生器在B[23..16]=66H和B[23..16]=F8H时输出信号为正弦波时的SignalTap II实时数据采样波形图。

图2 DDS正弦波信号发生器电路顶层原理图

图3 DDS正弦波信号发生器电路顶层原理仿真波形图

图4 DDS信号发生器在B[23..16]=66H时正弦波SignalTap II实时数据采样波形图

图5 DDS信号发生器在B[23..16]=F8H时正弦波SignalTap II实时数据采样波形图

从图4和图5可以看出,生成的正弦波光滑整洁,几乎没有毛刺,B[23..16]=66H时输出的正弦波频率明显低于B[23..16]=F8H时输出的正弦波的频率。

图6 DDS信号发生器在B[23..16]=F8H时方波SignalTap II实时数据采样波形图

图7 DDS信号发生器在B[23..16]=F8H时锯齿波SignalTap II实时数据采样波形图

图8 DDS信号发生器在B[23..16]=F8H时锯齿波SignalTap II实时数据采样波形图

图6、图7和图8分别是B[23..16]=F8H时输出方波、锯齿波和三角波的SignalTap II实时数据采样波形,可以看出输出的波形质量较好。

图9 DDS信号发生器输出方波时带测频功能电路顶层原理图

图10 B[23..16]=F8H时测量方波频率SignalTap II实时数据采样图

图11 采用DAC900输出方波信号频率为10MHz时SignalTap II实时数据采样图

为了检测所设计的DDS信号发生器输出信号的频率精度,在图2的基础上加上测量频率的模块。如图9所示,就是DDS信号发生器输出方波时带测频功能电路顶层原理图。其中fangbo_rom模块的地址线和数据线位宽跟产生正弦波时是一样的,也都是10位,不同的地方仅仅是离散波形数据,这里是一个周期的方波离散数据。pinlvji_32B是频率测量模块,测量频率的信号取自方波信号输出的最高位q[9],因为方波数据中各位数据是一样的,也可以取输出的其他位。SEG7[6..0]是输出频率数据经七段译码后的数据,接到七段数码显示器。由于8个七段数码显示器采用动态扫描的形式显示,LEDCOM[7..0]接到8个七段数码显示器的位选口。

图10是B[23..16]=F8H时测量方波频率SignalTap II实时数据采样图,其中data_out是频率测量模块pinlvji_32B内部频率测量后七段译码前的数据,是输出方波数据DAC[9..0]的实时频率数据。根据输出信号频率公式(10)可知,B[23..16]=F8h时,输出频率为:

而从图10可知B[23..16]=F8H时输出方波的测量频率也是189972Hz。下页表1是DDS信号发生器输出方波信号时15个理论值和实际输出测量值对比,可见输出信号的频率精度非常高,输出频率步进值也能稳定达到1Hz。由于输出其他波形信号时仅仅是产生波形模块里的离散波形数据不一样,其他都是一样的,所以其输出频率精度也是一样的。需要说明的是,虽然本设计的DDS信号发生器信号输出频率精度非常高,但在输出高频信号时,需要DAC芯片的速度也比较高,否则输出信号频率达到一定值时,信号质量会受影响。例如采用DAC0832,由于DAC0832的输出速度额定值最高只有1MHz,当输出信号频率达到2MHz时,信号形状开始明显变坏。图11为采用高速DAC芯片DAC900时输出信号频率达到10MHz时的波形以及测量值,可见频率精度和波形质量都还非常好。

表1 DDS信号发生器输出方波信号时15个理论值和测量值对比表

输入频率字B[31..0]输出理论值(Hz)实际测量值(Hz)56H11ACH2210C7H5050218EH100100FFFFH76376314F8BH1000100083126FH100001000066FFFFH7858378583F8FFFFH18997218997228F5C29H5000005000004189375H80000080000051EB852H10000001000000A3D70A4H20000002000000199999AH5000000500000033333333H1000000010000000

3总结

本文基于FPGA的DDS理论原理,用EDA方法通过FPGA方式设计了一个DDS信号发生器。仿真结果以及实际输出信号结果证明,该设计方法产生的信号发生器能够输出频率精度高、波形质量好、频率带宽大的正弦波、方波、锯齿波以及三角波。若配合锁相环技术和高速DAC芯片,则可以得到更宽泛频率的信号输出。

[1] 崔永俊,王晋伟,贾磊,等.基于FPGA的DDS信号发生器的设计与实现[J].电子器件,2016,39(2):339-343.

[2] 潘松,黄继业,潘明.EDA技术实用教程—Verilog HDL版[M]. 5版.北京:科学出版社,2013:190-193.

[3] 黄燕.基于FPGA的DDS信号发生器的研究[D].南京:南京林业大学,2012.

[4] 廖磊,何魏,周晓林.单片机与FPGA实训教程[M].北京:科学出版社,2016:310-317.

(责任编辑:覃华巧)

2017-03-30

梧州市科学研究与技术开发项目(200933(58))

TN741

A

1673-8535(2017)03-0010-07

黄玉健(1975-),男,广西滕县人,梧州学院图像处理与智能信息系统广西高校重点实验室讲师,研究方向:智能控制。

黄永庆(1968-),男,广西贵港人,梧州学院图像处理与智能信息系统广西高校重点实验室副主任,高级工程师,研究方向:智能控制。