基于三角函数内插法的Gardner位定时同步环的FPGA实现

邱文静

(南京熊猫汉达科技有限公司,江苏 南京 210014)

基于三角函数内插法的Gardner位定时同步环的FPGA实现

邱文静

(南京熊猫汉达科技有限公司,江苏 南京 210014)

位定时同步是全数字接收系统中的关键组成部分,对系统性能有重要影响。Gardner定时同步环结构简单便于工程实现,三角函数内插法结构简单内插精度高。文章将三角函数内插法应用于Gardner定时同步环,降低了实现难度。

三角函数内插法;位定时;Gardner算法

在加性高斯白噪声(Additive White Gaussian Noise,AWGN)信道条件下,根据最佳接收机理论导出的相关解调器或者匹配滤波器都必须在t=T时刻抽样判决,这里T是符号周期。t=T是最佳抽样判决时刻,超前或者滞后都会使误码率增加。在全数字无线通信接收系统中,收发双方通常采用完全独立的基准时钟源,两个时钟源的频率不可能完全匹配,再加上信号在传输过程中的延时一般未知,以及噪声等的影响,导致在接收采样过程中,最佳采样点不能直接采样得到,从而影响后续解调判决结果。这就需要对采样信号进行处理,获得最佳采样点。Gardner等通过分析异步采样对全数字接收机带来的影响,提出了基于内插的同步算法。

本文针对实际系统的需求,搭建了一种适用于PSK的通用的Gardner位定时同步电路。其中的插值滤波器采用了实现结构简单,内插精度高,适合于FPGA实现的三角函数内插算法。在Modelsim上对该电路进行了仿真,并进行了FPGA实现。该方案已经应用于实际系统中,能稳定可靠工作,性能良好。

1 Gardner位定时同步环模型

Gardner位定时同步环主要由内插滤波器、定时误差检测(Timing Error Detection,TED)、环路滤波器和控制器四部分组成。其基本结构如图1所示。

在该模型中,位同步的实现具体过程是,TED模块产生误差信号,经过环路滤波和控制器运算后产生了由overflow控制的内插时刻基准点和由μ控制的小数时间间隔,内插滤波器通过反馈过来的插值时刻信息进行插值操作,产生的数据送给TED模块产生新的定时误差信号,以逐步调整内插时刻,从而使信号尽可能地接近最佳采样点的值。

图1 位定时环路结构

2 FPGA实现及其Modelsim仿真

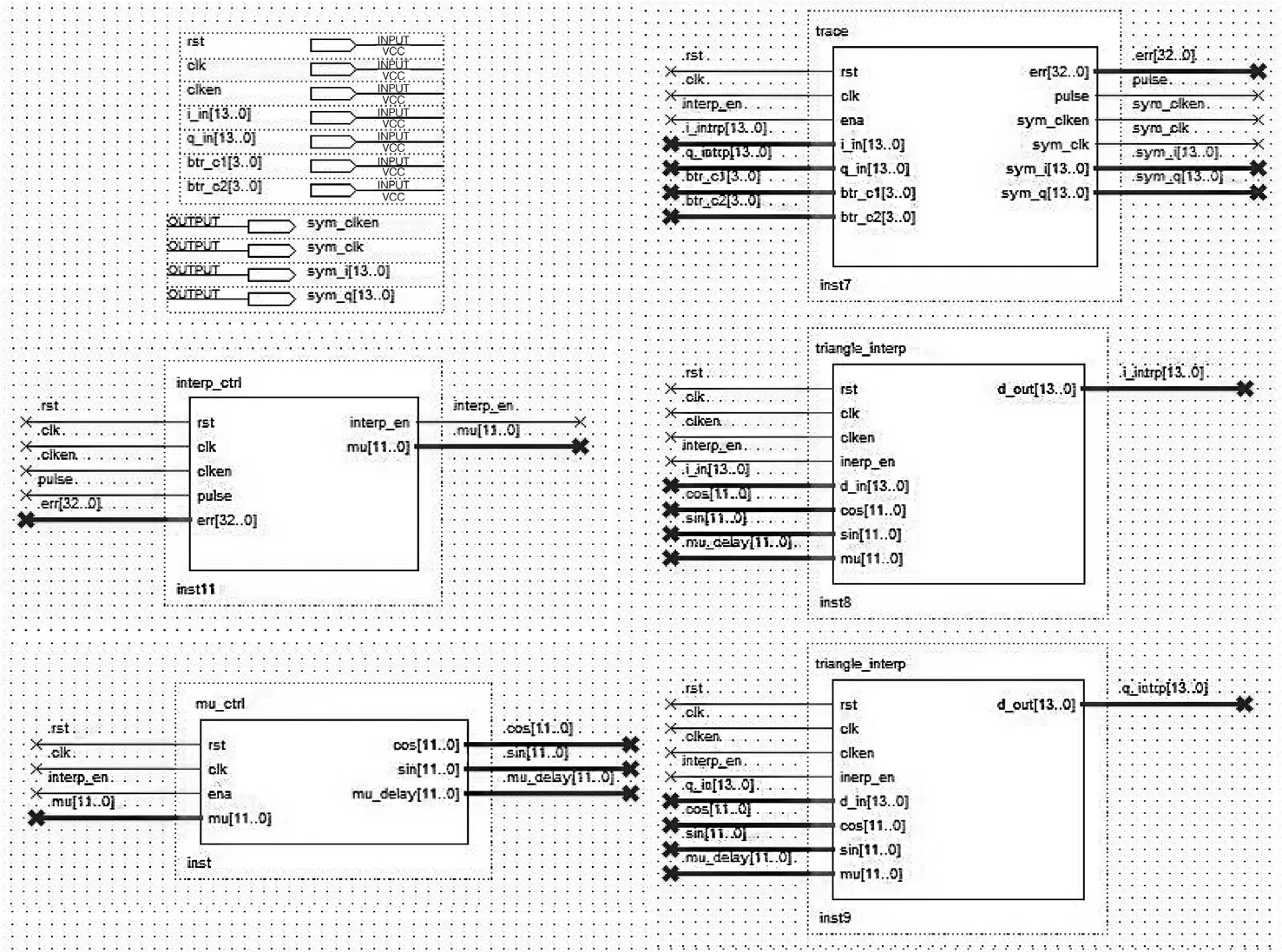

FPGA实现的顶层框图如图2所示,由三角函数插值滤波器、定时误差检测、环路滤波、插值控制等部分组成。本文仿真采用了BPSK调制方式,升余弦滤波器的滚降系数为1,采样数据经过与发端一致的平方根升余弦匹配滤波器,采样速率为每个符号4个采样点,设置本端采样周期与1/4个符号周期相比较偏小的T/512。具体模块描述如下。

图2 FPGA实现顶层

内插滤波器选用了内插精度高、适合于FPGA实现的三角函数内插滤波器,如图2中的triangle_inerp模块。该内插算法使用三角函数多项式代替传统的代数多项式,其中三角函数多项式的系数可以通过对N个采样点做N点离散傅立叶变换得到(N为插值需要的采样点数)。在实际应用中,N为4时就已经能够满足精度要求,且此时算法的实现结构非常简单。本设计采用三角函数内插的系数以及内插结果表达式。

定时误差检测采用了Gardner算法,提取一个误差信号一个符号只需要两个采样点,容易实现且不受载波相位偏移的影响。环路滤波采用锁相环中常用的比例积分结构,它具有较好的跟踪性能,两个系数K1和K2决定了环路的调整精度和速度。这两部分由上述公式中的trace模块完成。在本设计中环路滤波器的参数btr_c1和btr_c2通过右移位的方式实现乘法器功能,节省了资源提高了工作频率。同时两个参数对外放开,当应用环境发生变化时,可以通过外围电路重新配置。图4给出了该模块中定时误差处理的结果,依次是定时检测误差,环路滤波器比例支路的处理结果,积分支路的处理结果,以及提供给插值控制电路的控制字。此外该模块还输出最佳采样点的符号值供后级电路解调判决。

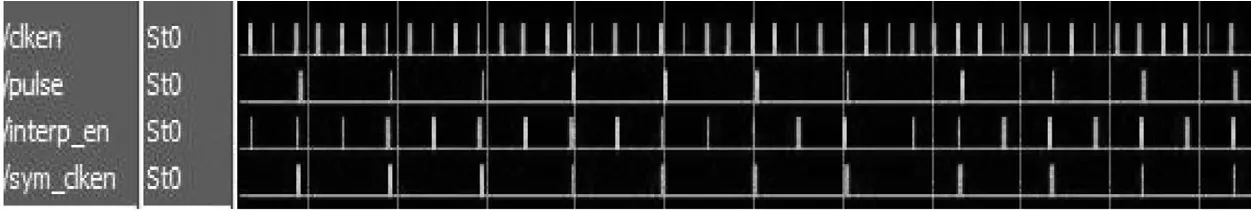

插值控制部分是内插滤波器的时序控制控制单元,由公式中的interp_ctrl模块完成。本设计采用了递减的模1计数器型NCO,工作时钟为采样时钟,NCO相位累加器的累加值为η(m+1)=(η(m)-W(m))mod1,其中的W(m)由环路滤波器输出的误差信号控制,工作时钟为符号时钟,其更新表示为W(n)=1/2+err(n)。当η(m)<0时,NCO向下溢出,其周期约为1/W(m)≈2,为两个采样时钟或者是1/2个符号周期,该时刻表示插值的基准点位置。所以有一个符号插值两个点满足了Gardner定时误差检测器的要求。当NCO向下溢出发生时,插值的小数间隔便可以由μk=η(mk)/W(mk)计算得出。图5给出了本次仿真中上述各工作时钟的时序关系,由上往下依次是采样时钟,环路滤波器输出定时误差信号的时钟,插值时钟,符号时钟,由图5可以看出各个工作时钟满足设计的需求,能保证该模块的正常工作。

图3 插值间隔及查找表结果

图4 定时误差处理结果

图5 插值控制模块时钟关系

3 结语

本文设计了一种适用于PSK调制方式的基于三角函数内插法的Gardner通用位定时同步环,并进行了FPGA实现和Modelsim仿真。在设计中从多方面优化了系统,降低了系统的资源开销。仿真和实际测试表明该位定时同步环路性能良好,稳定可靠。

[1]张公礼.全数字接收机理论与技术[M].北京:科学出版社,2005.

[2]PROAKIS J G. Digital Communication[M].New York:McGraw-Hill, 1995.

[3]GARDNER F M. A BPSK/QPSK timing-error detector for sampled receivers[J].IEEE Transcations on Communication, 1986(34):423-429.

[4]GARDNER F M. Interpolation in digital modems-part I:fundamentals[J].IEEE Transactions on Communnications, 1993(41):501-507.

[5]ERUP L, GARDNER F M, HARRIS R A. Interpolation in digital modems-part II:implementation and performance[J].IEEE Transcations on Communication, 1993(41):998-1008.

[6]DENGWEI F, ALAN N.Willson.Trigonometric polynomial interpolation for timing recovery[J].IEEE Transactions on Circuits and Systems, 2005(2):338-349.

FPGA implementation of Gardner Bit timing synchronization loop based on trigonometric polynomial interpolation

Qiu Wenjing

(Nanjing Panda Electronic Co., Ltd., Nanjing 210014, China)

Bit timing synchronization is one of the key component of all digital receiver, which directly affects the performance of the system. Gardner timing recovery loop has a simple structure, which is easy for engineering realization, trigonometric polynomial interpolation has a simple structure and enjoys high interpolation performance. In this paper, trigonometric interpolation method is applied to Gardner Bit timing synchronization loop and it reduces the dif fi culty of implementation.

trigonometric polynomial interpolation; bit timing synchronization; Gardner algorithm

邱文静(1982— ),女,江苏南京。