基于FPGA的多功能数据采集系统设计

刘晓东, 吴佳琪, 黄 旭, 李俊杰, 曹逢源

(同济大学 机械与能源工程学院,上海 201804)

基于FPGA的多功能数据采集系统设计

刘晓东, 吴佳琪, 黄 旭, 李俊杰, 曹逢源

(同济大学 机械与能源工程学院,上海 201804)

设计了一种以现场可编程门阵列(FPGA)为核心的数据采集系统。系统具有4个采集通道,直接通过上位机的指令配置,可根据实际需求选择实时采样或高速采样。设计了采集系统的硬件电路,开发了FPGA程序,以实现数据采集、存储、自动电桥平衡、状态反馈等功能,采用RS—232串口方式与上位机通信。实验证明:系统实现了预期功能,可达到实时采样频率为2.88 kHz和高速采样频率为91.5 kHz的数据采集。

数据采集; 现场可编程门阵列; 自动电桥平衡; RS—232串口

0 引 言

数据采集系统广泛应用于航空航天、医疗器械和机械工程等工业领域中[1]。在实际应用中,对采集系统有着多样化的需求:有的要求实时采集,有的要求高速采集,在对电桥电路的输出信号采集前还需对电桥初始不平衡进行调节。以切削力测量为例,如果采用市场上的标准仪器,则需同时配备电阻应变仪、示波器和信号分析仪等。

现场可编程门阵列(field programmable gate array,FPGA)是由可编程逻辑块组成的数字集成电路[2],具有速度快、抗干扰能力强、程序设计灵活方便等优点[3]。只要FPGA规模够大,理论上能形成一切数字系统,包括单片机甚至中央处理器(central processing unit,CPU)。目前FPGA的主要器件供应商有Altera,Xilinx,Lattice,Actel等[4]。

本文设计了以FPGA为处理器的多功能数据采集系统,实现实时采集、高速采集、自动电桥平衡等不同功能。

1 系统总体设计

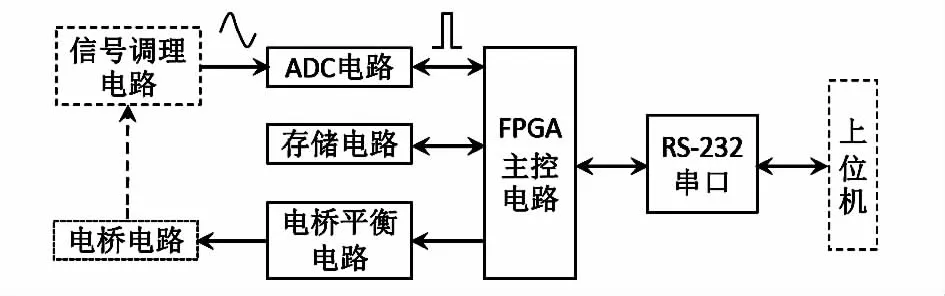

系统组成框图如图1所示,FPGA主控电路负责控制和协调各模块的工作;模/数转换(ADC)电路用于模拟信号的采集;存储电路用于数据存储;平衡调节电路用于对电桥初始不平衡的自动调节。FPGA和上位机之间的通信由RS—232串口实现。实时采样时,A/D转换后的数字信号经FPGA处理后直接由串口传送给上位机程序;高速采样时,A/D转换后的数字信号先在存储器中进行暂时存储。

图1 系统组成框图

2 系统硬件设计

2.1 FPGA选型及其配置

本文选用的FPGA芯片来自于Altera公司的Cyclone II系列,型号为EP2C5T144C8的FPGA,用户可用I/O管脚数89,工作电压3.3 V,内核电压1.2 V。系统采用JTAG配置模式,配置器件使用EPCS4,使用50 MHz的有源晶振连接FPGA全局时钟管脚。

2.2 采集及存储电路设计

采用的ADC芯片为MAX1301,为4通道16位分辨率的串行ADC,最高采样频率可以达到115 kSPS,工作电压为+5 V。输入输出引脚供电使用3.3 V,与FPGA I/O电平相兼容。由于是串行ADC,FPGA只需通过CS,DIN,SSTRB,SCLK,DOUT 5个引脚完成A/D采样,因此,A/D转换电路设计简单、占有空间少。电路原理图如图2所示。

系统采样速度大于串口传输速度时会出现数据阻塞。因此,需设计存储电路用于临时存储高速采样的数据,避免数据传输错误、丢失。本文选用赛普拉斯半导体公司的CY7C1018DV33静态存储器(SRAM),存储容量为128 kB。

图2 ADC电路原理

2.3 电桥平衡电路设计

采用数字电位器与控制器相结合的方法实现自动电桥平衡。为减少电位器对电桥输出的影响应尽量选择阻值大的电位器。但是数字电位器的抽头数有限,电位器阻值越大则跳变一次的阻值越大,导致调整精度减小。综合考虑,选用阻值分别为 1 kΩ和10 kΩ的X9C102和X9C103[5],作为电桥粗调和细调的执行器。电路原理图如图3所示。两个电位器并联后将滑动端S1_IN—输出连接到应变电桥的一个输出端上,即可实现对电桥输出的电压差补偿。

图3 电桥平衡电路原理

2.4 串口通信电路

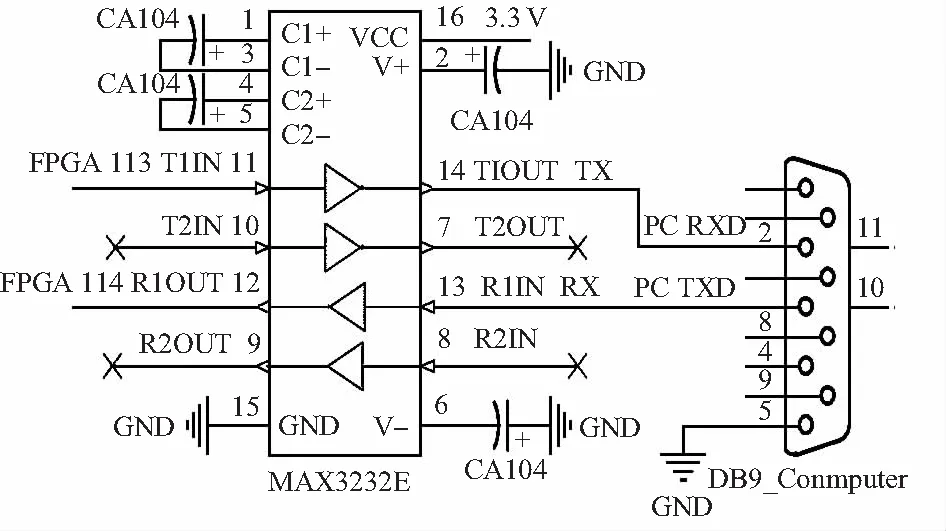

由于RS—232串口通信简单、可靠,且速度满足一般的采集系统要求。RS—232采用±3~±15 V电平标准,而FPGA只能兼容LVTTL以及LVCMOS电平标准,故两者不能兼容,需要进行电平转换。本文使用MAXIM公司的MAX3232E芯片进行电平转换。电路原理图如图4所示。

图4 MAX3232E电路原理

3 系统软件设计

采用Verilog硬件语言,在Quartus II平台进行数据采集系统的软件开发。FPGA软件设计采用模块化的方法,根据功能的不同,可将FPGA内部划分为不同的模块。通过模块化设计,实现了数据采集、数据存储、电桥平衡调节、简单数字滤波、指令识别、系统当前状态反馈等功能。

3.1 ADC控制模块

ADC控制模块用于控制ADC对经过信号调理之后的电桥信号进行采样。系统上电后,在进行采样前,需要先对MAX1301所需的通道进行模拟输入配置(analog input configuration)和工作模式配置(mode-control)。配置完成后即可按照控制指令的要求进行信号采集。

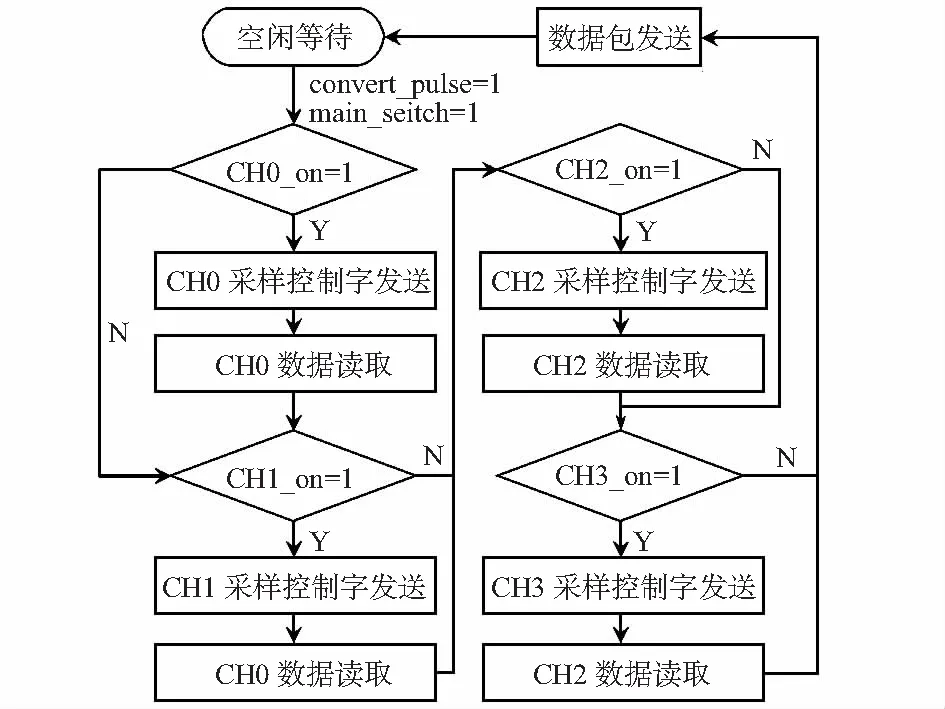

ADC控制模块的工作流程如图5所示。空闲等待状态下发生状态跳转的先决条件是检测到一个采样控制脉冲convert_pulse并且全局开关main_switch打开。此时根据CH0_on,CH1_on,CH2_on和CH3_on的状态来控制所需通道的采样控制字发送和数据读取。最后将数据打包发送,回到空闲等待状态。

图5 ADC控制模块工作流程

ADC控制模块的输出数据需要进行数字滤波。采用中值滤波法和滑动平均滤波法相结合,既能减少随机干扰,又能滤除明显的脉冲干扰,具有良好的滤波效果[6]。

3.2 存储器模块

存储器模块用于测试系统进行高速采集时的数据存储,可以实现高速存储和低速读取的目的。

存储器模块的工作流程如图6所示。初始状态下一直处于空循环,使能信号M68_enable拉高之后,模块开始按照存储器地址从低到高的顺序依次写入数据并计数。数据写入计数器i,溢出,则将其清空并开始从存储器中读出数据并发送给下一模块,通过延时以匹配串口的传输速度。数据读出计数器n溢出后对其清零并判断是否需要进行下一轮数据存储操作。

3.3 自动电桥平衡模块

自动电桥平衡模块采用闭环反馈控制原理,以实现自动、快速的电桥平衡调节。先由MAX1301对滤波放大后的电桥信号进行采样,得到电桥的不平衡量;再分别对两个数字电位器进行调整,减小电桥的不平衡量。调平完成的判别依据如图7所示。当输出电压穿过0 V时(即从正变成负或从负变成正),计算上一次采样值与0 V的差值ΔU1和当前的输出与0 V的差值ΔU2。若ΔU1<ΔU2,则撤销最后一次电位器操作,并发送调平完成信号;若ΔU1>ΔU2,则保留最后一次电位器操作,并直接发送调平完成信号。

图7 调平完成判断依据

3.4 指令识别模块和数据识别模块

采集系统的工作状态需要由上位机进行控制,控制过程通过发送指令的方式来实现。控制指令识别模块用于对指令的解读指令信息并调动、协调各模块的工作。本采集系统与上位机约定了5种指令,分别为开始采样、停止采样、采样频率配置、采样通道配置、电桥平衡调节。指令包含标识符、信息数据、校验位3部分。其中开始、停止采样为系统的全局控制指令,没有具体的配置对象,故不携带信息数据。控制指令识别模块的有限状态机(finite state machine,FSM)如图8所示。

图8 指令识别模块状态机

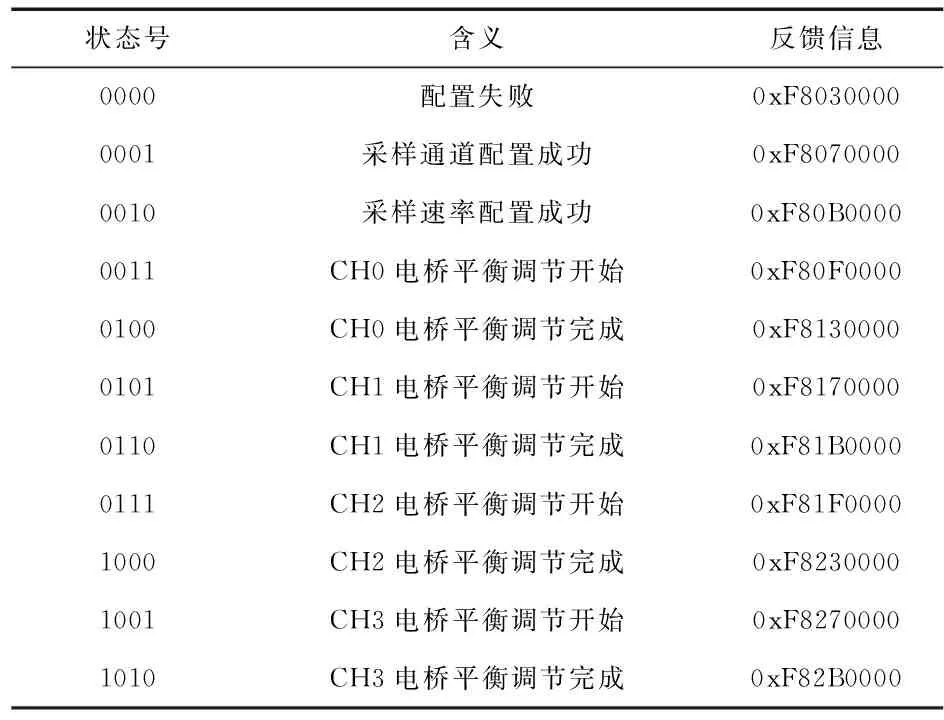

数据采集系统向上位机传输的数据包括各个通道的采集数据和状态反馈数据。数据识别模块用于选择当前时刻向上位机传送数据的类型、数据来源。其中反馈信息最优先传输,数据识别模块根据收到的状态号向上位机进行状态反馈,状态号和预置的反馈信息对应关系如表1所示。

表1 状态号和反馈信息对应关系

4 实验结果

4.1 电桥平衡调节实验

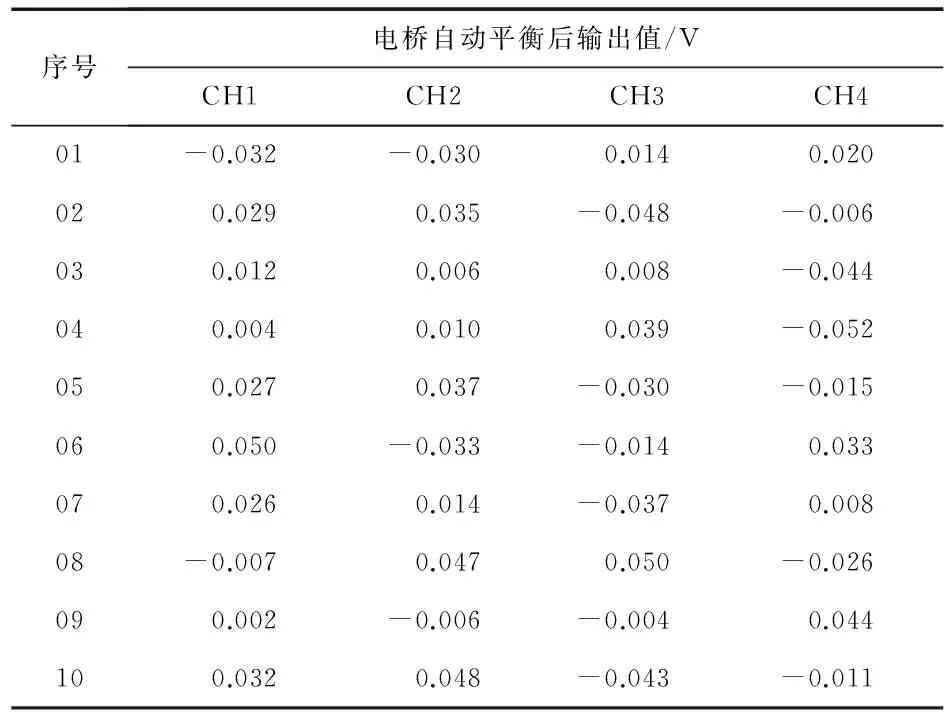

采用自主研发的4通道应变式测力仪,经过放大、滤波后接入采集系统。通过上位机发送调平指令后,调节完成后测得结果如表2所示。由表中可知:误差在±50 mV内,而所用时间不到5 s。

表2 电桥调平后测得电压值

4.2 数据采集实验

采用信号发生器作为信号源,分别产生幅值为±1 V的三角波、±2 V的方波以及±3 V的正弦波,频率均为2 Hz;再采用稳压源产生+4 V的恒定电压。将这4个信号分别接入4个通道,并通过上位机配置采集系统以200 Hz的频率进行数据采集。采集完成后对所采集数据进行保存,并截取其中400个数据点进行波形绘制,如图9所示。实验结果证明:采集系统工作稳定可靠,可达到实时采样频率2.88 kHz和高速采样频率91.5 kHz的数据采集。

5 结 论

本文设计了一种基于FPGA的多功能数据采集系统,并对设计过程进行了详细的描述。实验结果证明:本文设计的采集系统具有一定的应用价值。

图9 采集结果波形

[1] 于得钰.基于FPGA的A/D数据采集系统的设计[D].哈尔滨:黑龙江大学,2012.

[2] Clive“Max”Maxfield.FPGA设计指南[M].北京:人民邮电出版社,2007.

[3] 刘振国.分析仪器常用控制功能的FPGA实现[D].杭州:杭州电子科技大学,2012.

[4] 王 诚,蔡海宁,吴继华.Altera FPGA/CPLD设计(基础篇)[M].2版.北京:人民邮电出版社,2011:147-153.

[5] 纪宗南.高精度的数字电位器X9C103[J].集成电路应用,1999(4):6-9.

[6] 赵 毅,牟同升,沈小丽.单片机系统中数字滤波的算法[J].电测与仪表,2001,38(6):5-8.

吴佳琪,通讯作者,E—mail:wujiaqish@163.com。

Design of multi-functional data acquisition system based on FPGA

LIU Xiao-dong, WU Jia-qi, HUANG Xu, LI Jun-jie, CAO Feng-yuan

(School of Mechanical and Energy Engineering,Tongji University,Shanghai 201804,China)

A data acquisition system based on field programmable gate array(FPGA)is designed.The system has four acquisition channels.It is configured by commands of host computer,and can choose real-time sampling or high-speed sampling according to actual needs.Hardware circuit of the acquisition system is designed.FPGA program is developed to implement functions such as data acquisition,data storage, automatic electric bridge balance, and status feedback.FPGA communicates with the host computer via RS—232 serial port.The test shows that the expected functions are implemented, and the system can achieve 2.88 kHz in real-time sampling and 91.5 kHz in high-speed sampling.

data acquisition; field programmable gate array(FPGA); automatic electric bridge balance; RS—232 serial port

10.13873/J.1000—9787(2017)07—0096—04

2017—05—10

TP 274.2

A

1000—9787(2017)07—0096—04

刘晓东(1967-),男,博士,副教授,主要从事精密测量与控制工作。