一种由反相器构成的全定制时钟树

贾柱良 杜 明 黄阁飞

(国微电子有限公司,广东 深圳 518057)

一种由反相器构成的全定制时钟树

贾柱良 杜 明 黄阁飞

(国微电子有限公司,广东 深圳 518057)

本文介绍了一种由反相器构成的全定制时钟树,采用clockmesh+H_tree结构;通过virtuoso画出来的版图对称性更好,然后提取lef和lib导入设计中。设计的时钟树具有时钟延时低、低skew等优点。

全定制时钟树;clockmesh+H_tree;低skew

1 引言

随着集成电路的飞速发展,特征尺寸越来越小,芯片规模越来越大,芯片的工作频率也在不断提高。此时,时钟树综合也在芯片设计中成了一个重点难点。一个好的时钟树,可以使芯片更容易收敛,能够缩短芯片从后端设计到芯片上市的时间[1]。本文提出了一种全定制的clockmesh+H_tree结构的时钟树,能够有效降低时钟延时,减小时钟树skew,提高设计效率。

2 定制时钟树

在innovus中一般提供了平衡树、clockmesh、H_tree等时钟分布方式,我们在这里采用全定制的clockmesh+H_tree结构;clockmesh结构的时钟树具有时钟长度小、延时小等优点,但有局部skew值会较大,影响时序收敛;H_tree结构理论上讲从中心到各个节点的距离是相等的,所以信号延时也是一样,skew值理论上可以为0,由此运用在clockmesh中可以弥补其局部skew值较大的缺点[2]。

clockmesh+H_tree结构的时钟树结构如图1所示,主要由H_tree、时钟网格与local_tree三部分组成。时钟信号从时钟源通过H_tree到时钟网格上,然后到附近的local_tree的输入端,再通过反相器接入到SRAM的CLK端。由于时钟树是全定制模块,所以时钟树可以按照理想排布,时钟输出端靠近SRAM时钟端放置,全定制的时钟结构具有高度对称、时钟长度短、走线长度短等特点。

图1 定制时钟树结构示意图

3 时钟树设计实例

本章以一个65nm工艺下250MHZ的同步单端口SRAM的时钟树设计方法为例,介绍了全定制时钟树设计以及应用到innovus中的实际情况;该设计面积为11540um*9040um,全定制时钟树面积为9736um*6411um,且通过Hspice仿真提取其延迟信息,将其写入SDC约束文件中,通过PT分析验证了该时钟树的时钟长度短、时钟延时小、时钟偏差小的特点。

3.1 SRAM布局

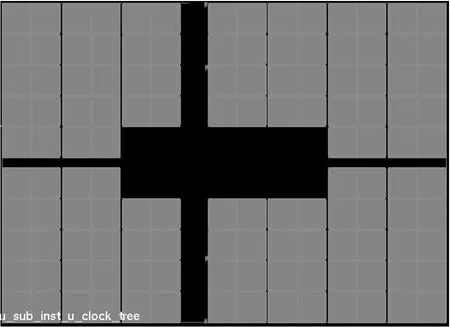

芯片一共用到了128个SRAM模块,其中由两个18位的SRAM组成一个36位的SRAM,所以在floorplan的时候竖直的两个SRAM组成36位的SRAM,通过对称摆放做到X轴对称排列,如图2所示;在virtuoso中设计clockmesh的时候将时钟树的输出端靠近两个SRAM的时钟端摆放,提高速度、降低时钟延时。

图2 SRAM布局图

3.2 时钟树定制

如图3所示为定制时钟树的H_tree结构,由两级H_tree组成,定制时钟树经过3级INV到达了clockmesh时钟网格,H_tree的起点在版图中心,每一级H_tree的输出到下一级输入的走线环境、长度、寄生电阻电容都几乎一致,同时每一级反相器根据走线长度都有不同的驱动能力,保证到能同时到达时钟网络。

如下图4所示为clockmesh的时钟网络,时钟信号通过H_tree到达时钟网格,再通过全局时钟树网络到达就近的local_tree,通过反相器到达SRAM的CLK端。

图3 H_tree结构

图4 时钟网络

3.3 全定制时钟树延时确定

由于该时钟树是全定制时钟树,所以自动布局布线工具innovus不能查找到其时序信息,这时候需要通过仿真工具获得其各支路延时信息;本设计采用Hspice仿真,获得其延时信息,操作流程如下:

(1)采用Assura-QRC流程提取全定制时钟树的各个corner下的寄生信息,提取格式为Hspice格式;再通过Hspice仿真得到其延时信息,生成各个corner的lib文件;

(2)将lib文件导入设计中,完成时钟树延时的反标,完成时序收敛后导出设计进行DRC、LVS等验证;

(3)由于实际设计中会有各种信号线与电源地线的影响,时钟树网络上的电容会有增大,所以(2)中导出设计后单独提出时钟树版图与金属线网,提取寄生文件,重新进行仿真并生成lib文件,导入设计中进行ECO优化,这时候的改动就不会太大,所以记录在innovus中的ECO优化记录,然后在版图中对应的地方参照innovus中的布局布线进行修改,使环境尽量一致。

从Hspice仿真结果得知,时钟树绝对延时为1.19ns,时钟偏差skew值小于37ps。

4 总结

本文通过大面积时钟树延时、时钟偏差考虑,设计了一种由反向器组成的具有clockmesh与H_tree结构的全定制时钟树;通过SRAM的对称排列与H_tree的设计规则性解决了clockmesh局部skew值偏大的影响,同时采用4级反相器结构并设计每一级的驱动能力都足够,通过迭代仿真使时钟树情况更真实。结论表明,该定制时钟树具有时钟长度小、时钟线延时小、时钟偏差skew小的特点。

[1]邓尧之.一种高效时钟树综合实现方法[D].北京:北京工业大学,2012.

[2]陈彦白.Fishbone和CTS时钟树的比较[D].上海:复旦大学,2008.

A FullCustom Clock Tree Consisted of Inverter

Jia Zhuliang Du M ing Huang Gefei

(Shenzhen StateM icroelectronicsCo.,Ltd.,Shenzhen 518057,Guangdong)

This paper introduces a full custom clock tree consisted of inverter,which uses the clockmesh and H_tree structure. The layoutdrew by virtuoso has better symmetrical characteristic.Then the lef and lib filesare extracted and input to the design.The clock treehas theadvantagesof smalldelay and lower skew

full-custom clock tree;clockmesh and H_tree;lower skew

TN47

A

1008-6609(2017)06-0037-02

贾柱良(1979-),男,湖南永州人,硕士研究生,工程师,研究方向为集成电路设计。