一种可用于LVDS接收器的高速CMOS运放

张 印,李海松,韩本光

(西安微电子技术研究所 陕西 西安710065)

一种可用于LVDS接收器的高速CMOS运放

张 印,李海松,韩本光

(西安微电子技术研究所 陕西 西安710065)

本文针对高速LVDS接收器电路,研究设计了一种高速、单位增益带宽1.46 GHz的CMOS运放。充分考虑LVDS的电气特点,采用了高速运放电路结构,基于0.13 μm 1.2 V/3.3 V CMOS工艺,进行了设计与仿真。仿真结果表明:该运放电路可以用于实现LVDS接收器。

LVDS接收器;差分信号;折叠式共源共栅;高速CMOS运放

随着IC工艺的飞速发展,超大规模集成电路(VLSI)设计越来越倾向于高速、低功耗领域。芯片和系统的整体性能也日益受到芯片间输入输出接口(I/ O)电路的速度和功耗限制。而目前LVDS技术已成为高速低功耗数据传输领域的主流技术。它具有信号摆幅小、速度快、功耗低、抗共模噪声能力强、电磁干扰小等优点[1-3]。

LVDS接口技术的原理可简单概括为:由驱动器(driver)将CMOS或TTL信号转换成LVDS差分信号,并经过互连线传输到接收器端,而接收器又将差分信号还原成CMOS或TTL信号。作为LVDS接收器,其一般的电路实现结构为CMOS运放[4-5]。而由于LVDS技术的电气特点,使得对于作为构成接收器的运放必然有相应的指标要求。

文中所设计的运放具有轨到轨的共模输入范围,并具有足够大的单位增益带宽以满足LVDS数据传输速率的要求。设计基于0.13 μm 1.2 V/3.3 V CMOS工艺。

1 运放电路设计

运放电路是LVDS接收器的核心部分。其重要功能是将高速、低摆幅LVDS差分信号进行放大,并实现双端差分信号到单端信号的转换,并最终得到可供后级逻辑模块识别的CMOS信号。 由LVDS接收器的电气特点,得到作为其核心电路——运放的相应指标,并以此指标为依据提出本文所设计的运放具体电路。

1.1 运放设计指标分析

由于LVDS驱动器和接收器可能存在参考地的电势差 Vgpd,接收器端输入的共模电平会产生相对1.2 V标称值的偏移。为了保证可靠的信号接收,LVDS标准TIA-EIA规定,接收电路必须在0.05~2.35 V的输入共模电平范围内稳定工作[6]。

表1所列为IEEE Std 1596.3-1996标准中定义的LVDS接收电路的部分电气规范值。由此得到,运放的输入共模输入范围应该至少包含0.05~2.35 V区间。另一点,本文设计的CMOS运放,期望用于数据传输速率能够达到1 Gbps的接收器,因而对运放的单位增益带宽有所要求。在参考了相关文献的基础上[7],并结合本文实际仿真验证,确定了本文所设计的运放需满足单位增益带宽GBW≥670 MHz。

表1 LVDS接收器电气规范

1.2 运放电路结构分析

结合1.1节中对运放指标的分析,在相关参考文献中LVDS接收器电路结构的的基础上[8-9],本文将用于LVDS接收器的运放电路设计为两级结构:其中,第一级为信号预放大级,将传输过程中被衰减的LVDS差分信号放大到合适的幅值,并对信号的共模电平进行调整,便于后级进行信号处理;同时,考虑到输入信号的共模电平范围很宽,设计了包含NMOS输入运放和PMOS输入运放,分别独立对输入信号进行预放大,如此可以实现轨到轨的输入。第二级为主放大级,功能是将第一级输出的信号进一步放大并实现双端差分信号到单端信号的转换,最终得到可供后级逻辑模块识别的CMOS信号。至此,得到运放的整体框图如图1所示。

图1 运放结构框图

1.3 各模块电路设计

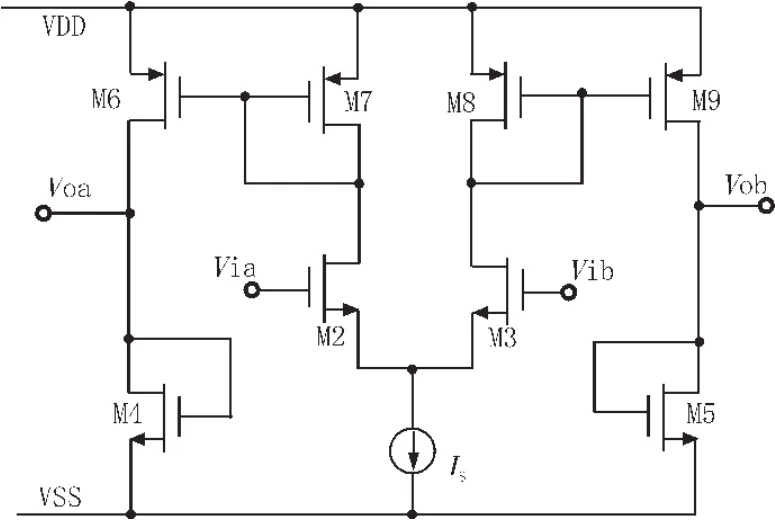

图1中NMOS输入电流转换型运放的具体实现电路如图2所示(PMOS输入型结构为对偶结构,不再给出)。该运放是一种全差分高速CMOS电路,可以很好的抑制输入信号的共模分量的扰动[10-12]。输出信号voa和vob的共模电平得到了很好的稳定,便于后级运放进行处理。

该电路为对称结构,其交流小信号增益只进行半边电路分析即可。记via为输入管M2所加的交流小信号,则M2管产生的小信号电流为viagm2,M6管镜像M7管的电流,并在二极管连接的M4管栅漏端产生输出小信号voa,

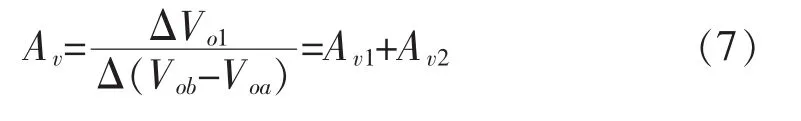

同样的分析,vob与vib的关系与该式相同。via和vib为差分信号,有vib=-via,得到双端输出时的交流小信号增益为:

图2 NMOS输入电流转换型运放

图3 折叠式共源共栅运放

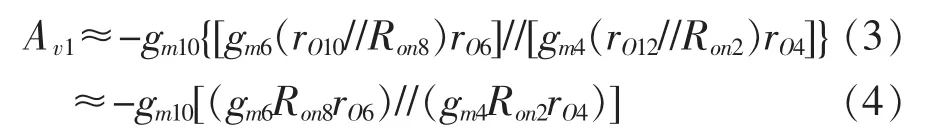

图1中N、P结合型折叠式共源共栅运放的具体实现电路如图3所示[14]。该电路最重要的特点是输入共模范围是从VSS到VDD。其次,该电路的总跨导在共模输入电压约为电源电压VDD的二分之一时达到最大值[15]。设计时,使得前一级运放的输出共模电平值尽量接近VDD的一半,实现两级之间很好的对接。

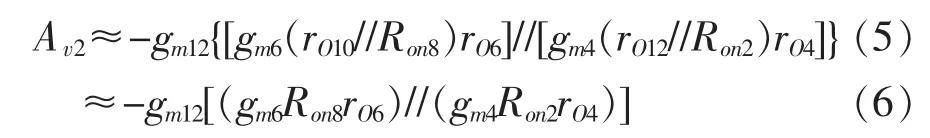

该电路Vb1,Vb2和Vb3为偏置电平,设计时为了实现运放较高的单位增益带宽,将M1~2和M7~8偏置在线性区。M9和M10组成NMOS差分对,M11和M12组成PMOS差分对。输入信号Vob经两条通路到输出Vo1,一条是经过NMOS差分对、M6管,另一条是经过PMOS差分对、M4管。先以第一条信号通路分析。由于M7~8的等效电阻很小,因而该差分对的增益很小,M6管对M8漏极的小信号进行共栅极放大,得到输出Vo1。该通路的小信号增益为:

Ron8和Ron2为线性区管M8、M2的导通电阻。对第二条通路的分析与上类似,小信号增益为:

设计时,使得NMOS管与PMOS管相匹配,有gm10≈gm12,gm6≈gm4及Ron8≈Ron2,因而可得该级运放总的增益为:

2 电路仿真验证

图2所示的NMOS输入型运放的输入共模电平仿真曲线如图4所示。

图4 输入共模电平范围仿真结果

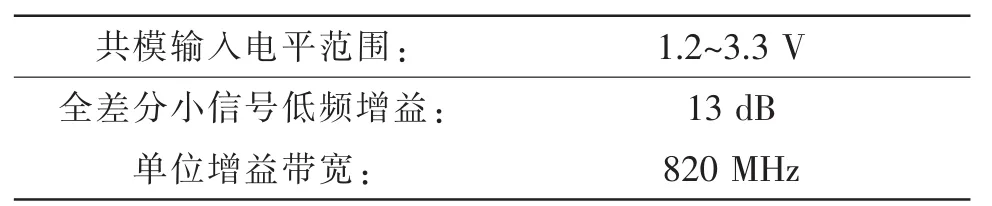

由图4以看出,在1.2~3.3 V范围内,输出随输入呈线性关系,该范围即为输入共模电平范围。NMOS电流转换型运放的其他性能指标如表2所示(电容负载取为100 fF):

表2 仿真结果列表

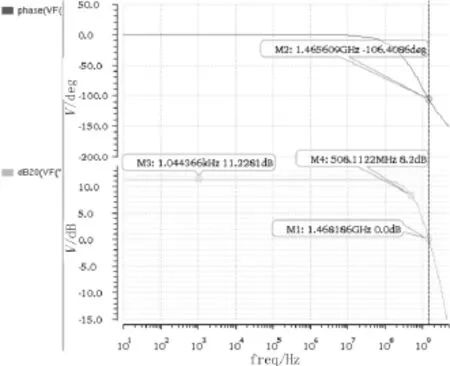

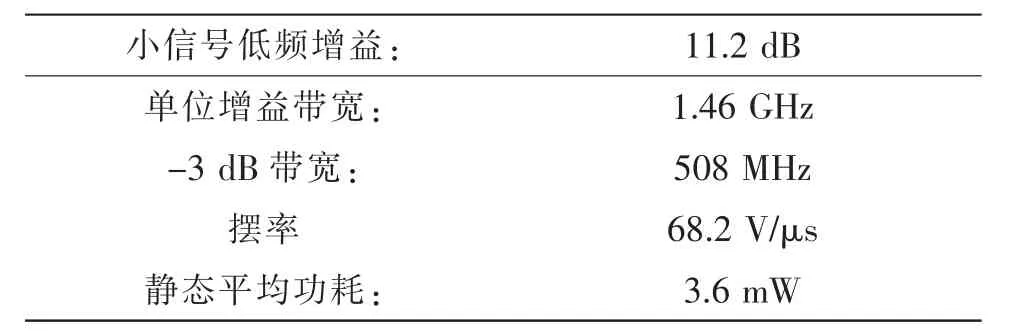

图3示的折叠式共源共栅运放的仿真波形如图5、6所示。图5为运放频率特性仿真结果,可看出运放的单位增益带宽为1.46 GHz。图6为运放瞬态特性仿真波形。

图3所示的折叠式共源共栅运放的性能仿真结果如表3所示(电容负载取为50 fF):

3 芯片测试

图5 运放增益及频率特性图

图6 瞬态特性图

表3 仿真结果列表

文中设计的高速CMOS运放用于某款LVDS接收器,流片后对LVDS接收器的性能参数进行了测试。测试的结果完全符合IEEE Std 1596.3-1996标准。图7为进行测试的电路板。

图7 LVDS接收器测试电路板

按照LVDS的IEEE标准中规定的测试方法,对LVDS接收器阈值及输入共模范围进行测试,测试结果如表4所示。

表4 LVDS接收器测试结果

表4中,Via、Vib分别是LVDS接收器的两个输入端口所加电压值。由测试结果看,接收器的输入差分电压在100 mV至600 mV范围内,接收器的输出状态正确。表明接收器输入阈值及输入共模范围这两个指标均满足要求。

4 结 论

文中基于LVDS接收器的电气特点,设计了其核心部分电路——运放。所设计的运放具有轨到轨的输入范围,且有1.46 GHz的单位增益带宽和高的摆率。设计基于0.13 μm 1.2 V/3.3 V CMOS工艺。所设计的运放电路已用于某款LVDS接收器,且该接收器流片后实测的性能指标均符合IEEE标准。

[1]孙金中,谢凤英.一种高速低功耗LVDS接收器电路的设计 [J].电子科技,2012,25(6):95-97.

[2]陈莹,高双成.基于FPGA的LVDS接口应用[J].电子科技,2012,25(1):8-12.

[3]XU Jian,WANG Zhigong,NIU Xiaokang.Design of high speed LVDS transceiver ICs[J].Journal of Semiconductors,2010,31(7):151-159.

[4]朱红卫,赵郁炜.一种高性能LVDS收发器的设计[J].微电子学,2014,44(4):420-429.

[5]赵耀华,陆铁军,王宗民.基于VLSI的高速LVDS接口设计[J].微电子学与计算机,2009,26(11): 78-81.

[6]IEEE Std 1596.3-1996.IEEE standard for lowvoltage differential signals (LVDS)for scalable coherent interface(SCI)[S].1996.

[7]矫逸书,周玉梅,蒋见花.千兆比特数据率LVDS接口电路设计[J].固体电子学研究与进展,2010,30(1):119-123.

[8]尤扬,陈岚.一种高性能CMOS LVDS接收电路的设计[J].微电子学,2007,37(6):899-902.

[9]孙金中,谢凤英.一种应用于高速数据通信的LVDS接收器设计[J].中国集成电路,2012(6):39-43.

[10]黄君凯,徐卓慧,陈松涛.一种高性能CMOS运算放大器的设计[J].微电子学,2010,40(1):2-3.

[11]宋奇伟,张正平.一种新型高速CMOS全差分运算放大器设计[J].现代电子技术,2012,35(4):2-3.

[12]廖成芳.CMOS低噪声宽带宽全差分运算放大器设计[D].长沙:湖南大学,2007.

[13]王建军,李少青,欧阳干.一种高速LVDS收发器的设计与实现 [C]//计算机工程与工艺全国学术年会,2006.

[14]尹璐.高增益高速运算放大器的研究与改进[D].武汉:华中科技大学,2007.

[15][美]毕查德·拉扎维.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2003.

High speed CMOS amplifier for LVDS receiver

ZHANG Yin,LI Hai-song,HAN Ben-guang

(Micro-electronics Technology Institute,Xi'an 710065,China)

A high speed LVDS receiver circuit has been studied in this paper and a high speed CMOS amplifier which has a unit gain bandwith of nearly 1GHz has been designed.Taking fully into consideration of the electrical characteristic of LVDS receiver,a high speed circuit design has been used,based on the 0.13 μm 1.2 V/3.3 V CMOS technology,the CMOS amplifier circuit has been designed and simulated.The simulation result has showed that the amplifier circuit can be satisfied with the performance of LVDS receiver.

LVDS receiver;differential signal;folded cascode;high speed CMOS amplifier

TN43;TN45

A

1674-6236(2017)10-0128-04

2016-04-11稿件编号:201604109

张 印(1988—),男,陕西咸阳人,硕士研究生。研究方向:模拟集成电路设计。