航天计算机研制中的高速电路仿真技术

李 扬

(奥肯思科技有限公司,北京 100045)

航天计算机研制中的高速电路仿真技术

李 扬

(奥肯思科技有限公司,北京 100045)

主要介绍了高速电路仿真技术在航天计算机研制中的应用,通过某航天计算机主板实际项目的设计和仿真,介绍了高速电路设计中信号完整性仿真的流程和方法;通过前仿真对设计的指导以及后仿真对设计的验证,详细描述了高速电路设计的流程,并提出高速电路设计应注意的问题。

信号完整性;串扰;电磁兼容性;前仿真;后仿真;IBIS模型

0 引言

随着航天技术的发展,对航天计算机处理能力的要求也不断提高,中央处理器CPU及其周边器件工作频率的提高不可避免地引发高速电路问题,因此,高速电路设计也成为航天计算机研制中的一个关键性问题。

在高速电路设计中,随着系统工作频率的提高和布线密度的增加,信号完整性(Signal Integrity)、串扰(Crosstalk)、EMC(Electro Magnetic Compatibility)等问题对于设计高质量的电路越来越重要。要解决这些问题,通过高速电路仿真来辅助设计是十分有效的方法,通过仿真可以掌握信号传播的基本特性[1]。在设计初期,仿真对系统设计起着指导的作用,用来确定在各种可选的情况下做出一种最合理的选择,比如元器件不同的驱动能力、传输线的拓扑结构、终端匹配的方式等。在设计后期,仿真用来验证系统电路设计的可行性。在本设计中,将设计初期的仿真称之为前仿真,设计后期的仿真验证称之为后仿真。

需要注意的是,在实际电路环境中,还存在大量其他因素影响信号质量,这时就需要灵活应用高速电路设计概念及一些基本设计原则以及平时积累的经验来分析问题。通过高速电路的理论知识并结合以往电路设计的经验来确定最终的设计方案。

本文结合一种高性能航天计算机主板研制过程中遇到的高速电路问题及其解决方法,阐述了高速电路设计的基本方法,给出了信号完整性仿真的结果,并提出高速电路设计中应注意的问题。

1 设计流程

本文所述的电路设计采用了Mentor Graphics公司的原理图及PCB设计软件,高速信号完整性仿真采用了Mentor Graphics的HyperLynx SI高速信号完整性仿真软件。

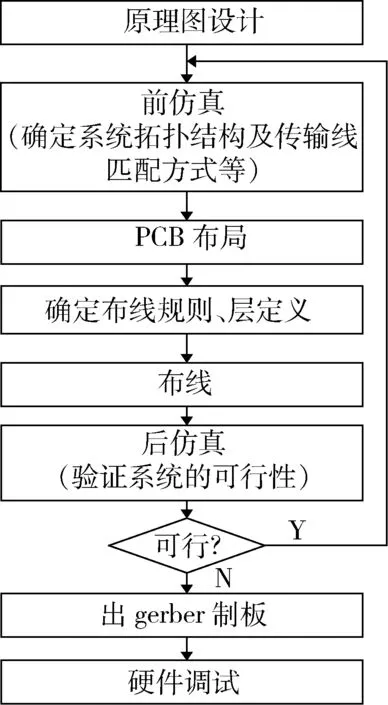

图1 高速电路设计流程图

对于低速电路设计,通常的解决方法是:原理图→硬件实现→样机调试等几个关键的步骤,调试中出现问题的解决方案也多是通过检查原理图、更改原理图设计来实现。而高速电路设计中,即使原理图正确无误,也很可能因为信号完整性等问题会使原理正确的电路在实际中无法正常工作。

通常,高速电路设计中的设计流程一般为: 原理图设计→前仿真→PCB布局→确定布线规则→布线→后仿真→制板→硬件调试[2]。高速电路设计的流程图如图1所示。

原理图设计阶段的主要工作是确定系统的结构、所采用的元器件以及使用的总线等,参考元器件手册,选择元器件的工作方式并进行正确的网络互连。

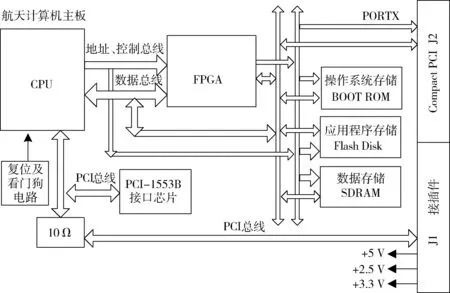

该航天计算机主板上的主要器件为CPU、FPGA、SDRAM、BOOTROM、Flash Disk、1553B接口芯片、Compact PCI接插件等,主板原理如图2所示。

图2 主板原理图

主板上CPU运行时钟可达到250 MHz,处理能力可达到300 MIPS,SDRAM工作频率为100 MHz,PCI总线工作频率33 MHz,都属于高速信号的范畴,这都需要通过高速电路仿真来确定合理的设计方案[3]。

2 设计前仿真

通常,PCB板在设计完成之后要实施有效的解决办法,需要花费大量时间和费用,甚至可能需要重新设计。相比之下,如果在设计初期和设计过程中就综合考虑高速电路可能会造成的影响,修改同样的问题所花的时间和费用要少得多,因此,在电路板设计之前进行深入细致的仿真分析及电路设计的前仿真是非常必要的。

前仿真可根据设计对信号完整性与时序的要求,在布局和布线前帮助设计者合理安排器件布局、规划网络拓扑结构以及确定关键信号的布线策略。

2.1 模型选择

仿真中首先要解决的一个问题是元器件的模型问题,目前常用的模型为Spice模型和IBIS模型,Spice模型由Buffer内部的电路结构和工艺参数构成,因为知识产权等问题,一般厂商并不公开公布。IBIS模型数据来源于Spice模型,它基于Spice仿真结果而采用表格化的V-I及V-T曲线描述Buffer的行为,其特点是运行速度较快,并且保护了厂商的知识产权,便于与用户间的数据交换[4]。IBIS模型已经得到各主要EDA工具厂家仿真工具的支持。本设计中,器件的仿真模型选用了IBIS模型。

从器件厂商网站下载得到的IBIS模型可能会因为非单调等问题需要进行检查和编辑,在本设计中采用的HyperLynx Visual IBIS Editor模型编辑工具对模型进行了检查和编辑,使之符合仿真要求[5]。

2.2 器件驱动能力选择

在进行前仿真之前,有些参数已经基本确定,比如各种信号的线宽、线间距、走线类型、介电常数等参数都应该能确定下来,这些参数实际也是进行仿真的约束条件。在本设计中由于CPU使用手册对地址总线和PCI总线推荐串联10 Ω电阻,这相当于在仿真中采用了串联的终端匹配方式。终端匹配方式确定后,在前仿真中主要的工作就是CPU总线驱动能力的选择以及总线拓扑结构的选择。

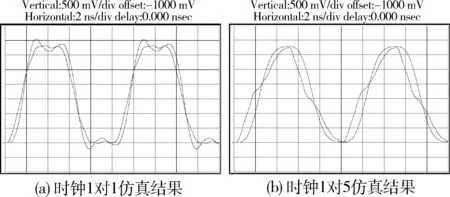

CPU的时钟总共有四路可以提供,而SDRAM需要有5路时钟输入,是采用四路输出到SDRAM,其中第四路分成两路输出,还是采用1路输出后分成5路到SDRAM的负载端,主要需考虑的是CPU时钟信号的驱动能力。

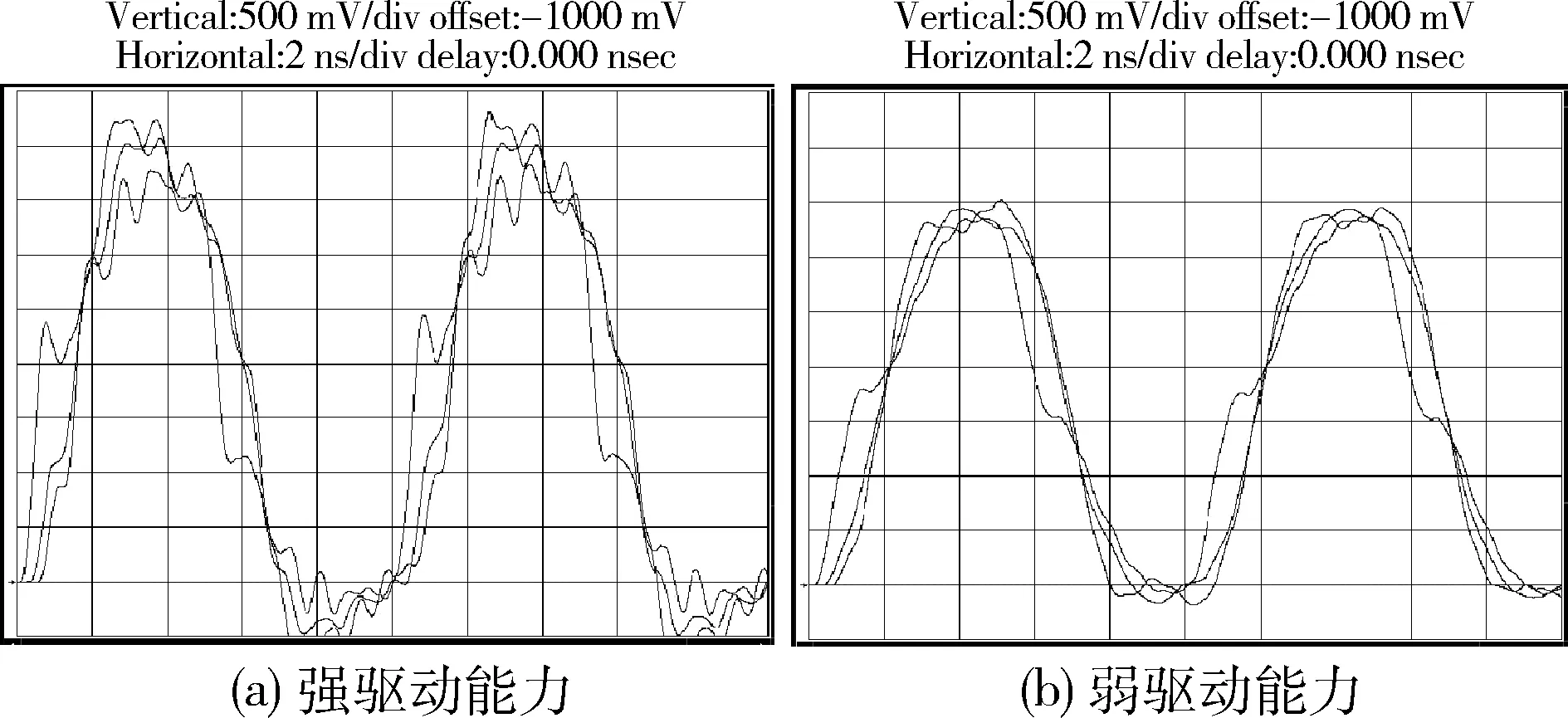

如果CPU时钟信号驱动能力较弱,就需采用前一种方案,如果驱动能力足够强,就应该采用第二种方案。图3给出两种连接方式的仿真结果。

图3 两种时钟连接方式仿真结果

通过仿真可以看出,采用第二种方案能满足信号质量的要求。虽然信号上升时间较第一种稍长,但避免了过冲的出现,并且,对于高速电路设计,在满足时序的前提下,较大的上升时间可以避免传输线效应的过早出现,因而对信号完整性及EMC都是有益的,而且一路输出布线简单,各负载之间的同步更容易保证。所以,本设计采用了第二种方案。因为时钟信号需要考虑同步,其拓扑结构选择为远端分支连接。

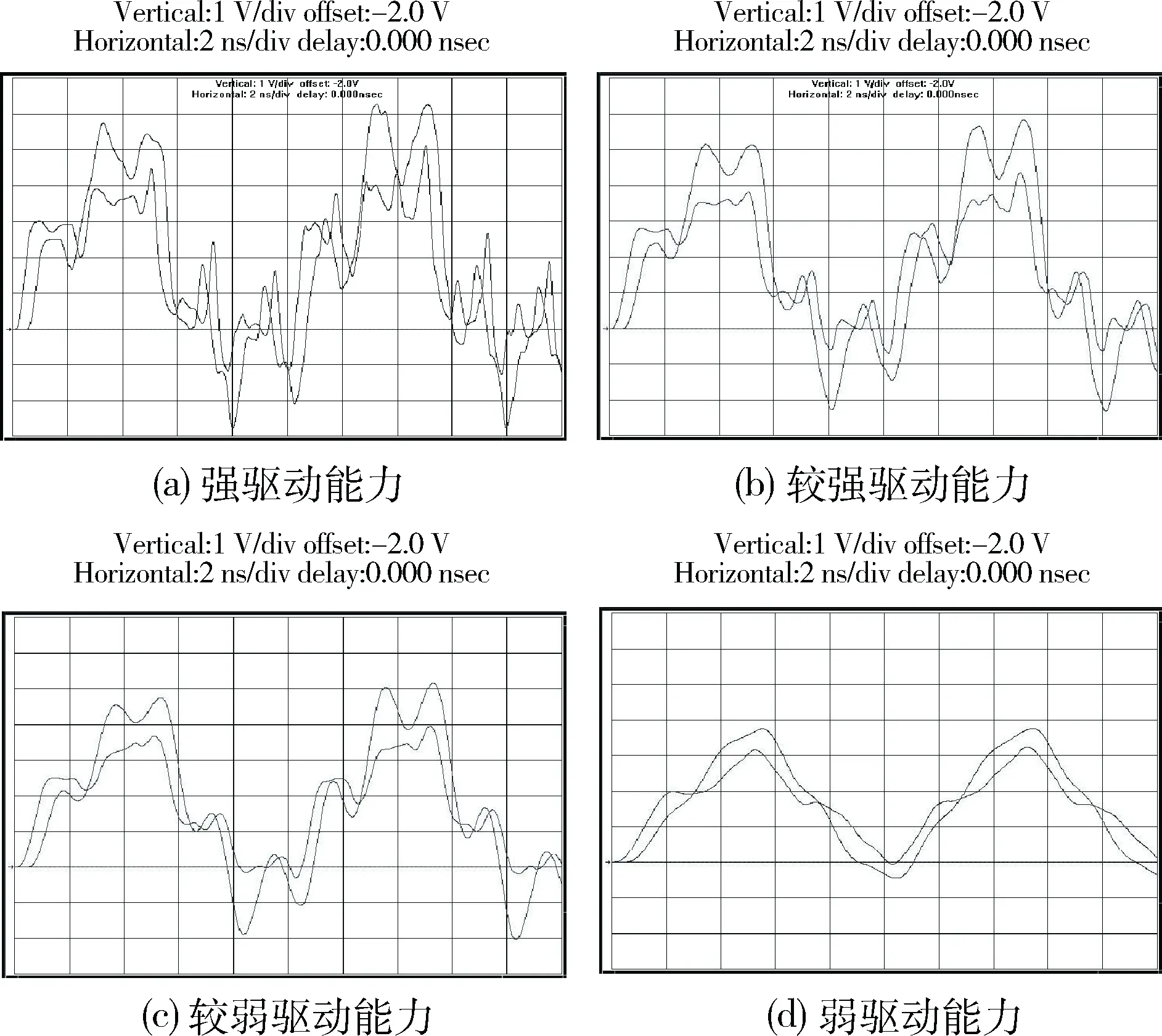

时钟的驱动能力确定后,CPU地址和数据总线驱动能力选择也需要通过前仿真来确定。在本设计中,CPU地址总线有四种驱动能力可供选择,数据总线有两种驱动能力可供选择。

地址总线四种驱动能力下的仿真结果如图4所示。

图4 地址总线的四种驱动能力下的仿真结果

数据总线两种驱动能力下的仿真结果如图5所示。

图5 数据总线两种驱动能力下的仿真结果

从仿真结果可以看出,对于本设计中的CPU,地址总线选择弱驱动能力时,过冲、反射都比较小,信号完整性和EMC特性也比较好;对于数据总线,根据同样的判断原则,也应当选择弱驱动能力。

2.3 规划总线拓扑结构

CPU驱动能力确定后,下一步需要通过前仿真确定总线拓扑结构,图6是几种比较典型的拓扑结构。

点到点(Point-to-Point)拓扑结构比较简单,只要在发送端或接收端进行适当的阻抗匹配便可以得到较好的信号质量;星型(Star)拓扑结构适合于对每个分支要求同步或者均衡的设计;菊花链(Daisy chain)拓扑结构适合于对网络中的每个分支并不需要完全同步或均衡的设计;远端分支(Far-end cluster),跟星型有些类似,只不过分支靠近接收端,通常在时钟信号分支中采用。

当传输线由两段不同特性阻抗的传输线组成时,连接点处也会产生信号反射,传输线上出现的分叉点就是这样一个阻抗不连续点。在高速电路设计中,由于传输线特性的存在,导致多端网络在使用不同的拓扑结构和阻抗匹配方式时,各点得到的信号波形不一样。

在本设计中,地址、数据总线需从CPU连接到FPGA、SDRAM、FALSH DISK等,其中CPU和SDRAM之间的信号为关键信号,通常认为,缩短传输线长度,减少传输线效应是提高信号质量的关键。因此在原理设计时考虑将SDRAM布局离CPU近一些,初步考虑布局时SDRAM应该紧靠CPU。对于地址、数据总线的拓扑结构,根据本设计的实际情况应在星型和菊花链之间进行选择,至于到底是采用星型连接还是菊花链连接,就需要通过仿真来获取合理的答案。

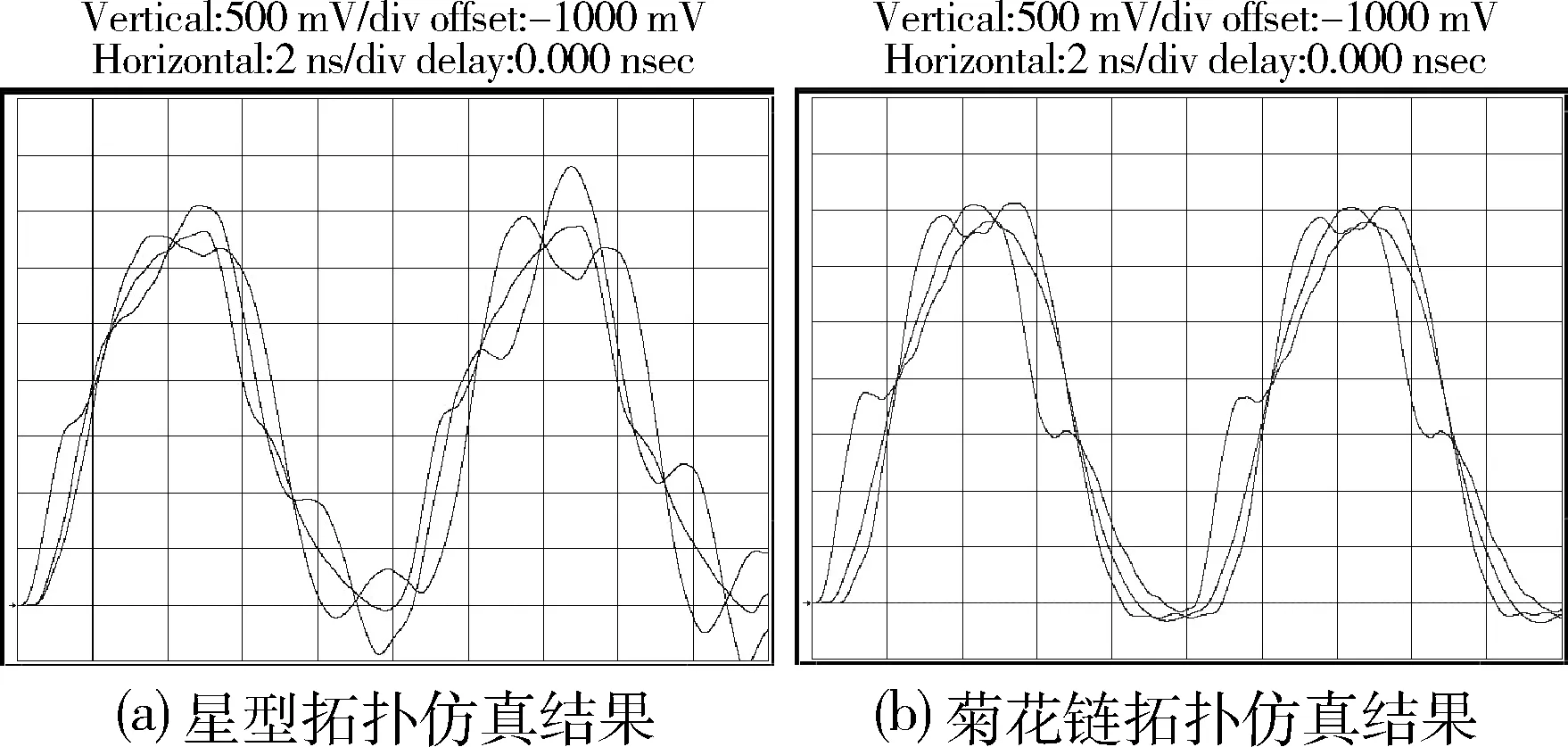

前仿真主要是在HyperLynx SI的前仿真环境LineSim下进行,图7是采用星型和菊花链两种拓扑结构得到的仿真结果。

图7 两种不同拓扑结构仿真结果

从图7仿真结果可以看出,采用菊花链方式信号质量比较好,并且可以得出在菊花链的远端信号质量相对较好,上升时间也较短,所以将速率较高、对信号质量要求较严格的SDRAM放在菊花链的远端,这与最初原理图设计时的考虑恰好是相反的,需要重点关注。

2.4 前仿真结论和对设计的指导

至此,前仿真工作已经基本完成。通过前仿真可得到的结论如下:

(1)地址和数据网络的拓扑结构选择菊花链连接方式,并且将信号质量要求较高的SDRAM放在菊花链的远端。

(2)时钟网络采用1对5的连接方式,拓扑结构为远端分支连接。

(3)CPU地址总线选择弱驱动能力。

(4)CPU数据总线选择弱驱动能力。

(5)串联电阻的匹配方式,在仿真中得到检验,效果较好,能够满足设计要求。

3 布局与布线

前仿真结束后的工作就是电路板布局,布局的原则是参照前仿真结果,并结合以往的设计经验,在PCB设计工具中完成。SDRAM因为处于菊花链的远端,所以放在了离CPU较远的位置,与最初原理设计时的考虑是不同的。

布局完成后的主要工作就是布线,在布线之前首先要设置好布线规则。

布线规则主要是限制各个网络走线的长度、线间距、走线宽度、扇出方式、过孔选择,以及网络拓扑规划等。同时,对电路板的层定义、各层的布线方向、平面层分布、电源分割等也需要在布线前设置完成。

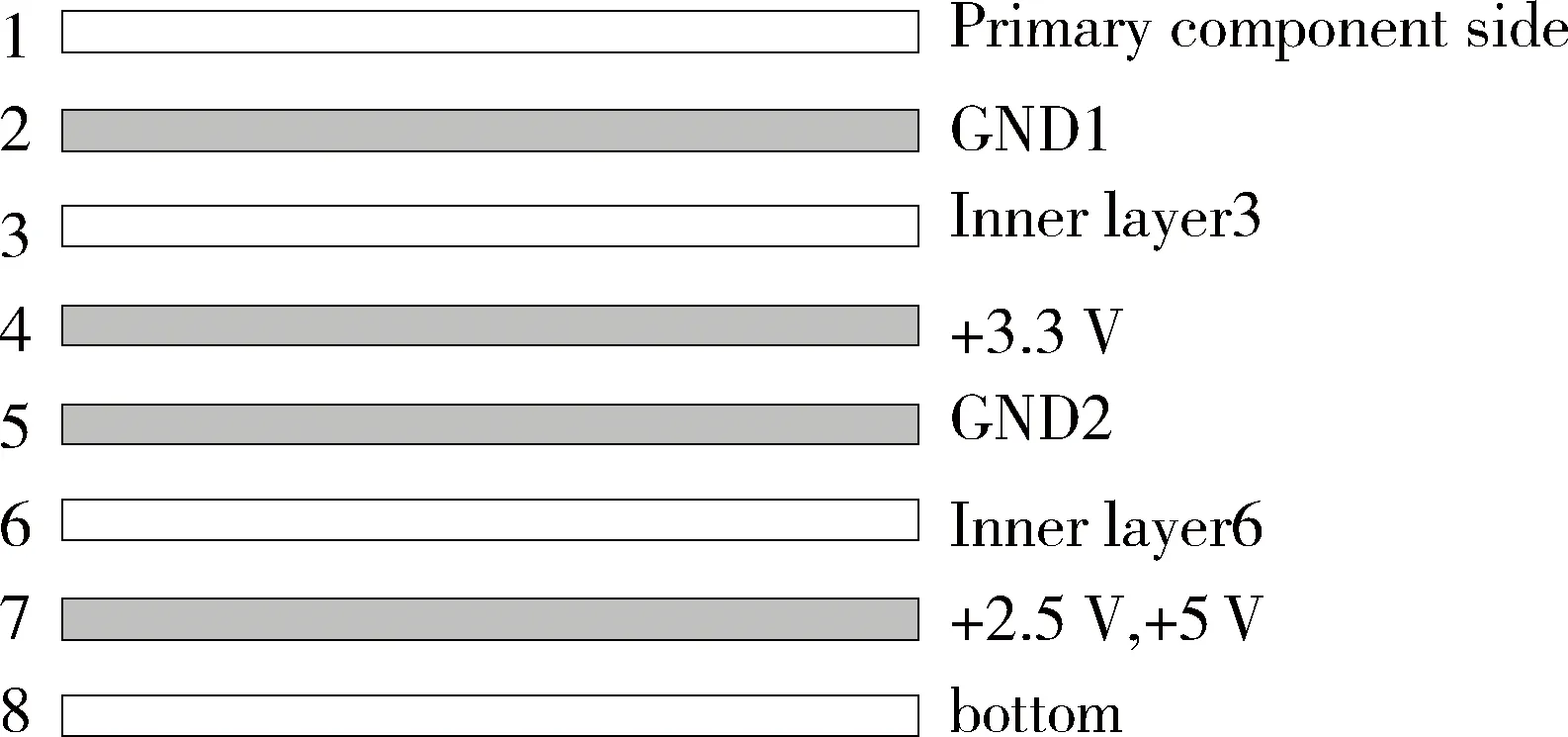

本主板设计为8层板结构,分为四个走线层,四个平面层,电路板各层分布如图8所示,其中白色为走线层,灰色表示平面层(电源平面或地平面)。

图8 电路板各层分布

因为使用+2.5 V和+5 V电源的元器件分布在电路板的不同部位,该设计对第7层进行了电源平面层分割。分割时应当重点考虑平面层的分割线不能阻挡高速信号的通路。

各种规则设定好后就是布线,布线的原则是先布关键信号,然后布比较重要的信号,最后布一般信号;先从信号最密的地方开始布线。同时,给信号安排合适的布线层,确保高速信号有完整的回流路径。本设计采用了手动布线结合自动布线的方法。首先手动完成关键信号和比较重要信号的布线,并将完成的布线锁定保护起来,然后采用自动布线继续布线,直到完成100%。在时间许可的情况下,应尽量采用手动布线,这样才能体现设计者的意图,更能保证信号传输的质量。

4 后仿真验证

布线完成后的工作是对设计进行后仿真,验证电路设计的可行性。

后仿真可分为关键信号仿真和整板仿真,通过关键信号仿真检查关键信号是否满足信号完整性、串扰和EMC的要求;通过整板仿真,检查整个板子上的所有信号,仿真报告会给出提示,说明哪些信号可能会存在信号完整性、串扰和EMC等问题。

后仿真的主要功能是验证电路设计的可行性,如果后仿真不能通过,系统就得重新进行设计[6]。所以,对于高速电路设计,前仿真更为重要。前仿真可以确保系统在一开始就能进行正确合理的设计,前仿真做充分了,后仿真就会有比较满意的结果。如果前仿真没有认真完成就急于开始布局和布线,往往后仿真就不能顺利通过,结果可能是从头再来,人力和资源消耗都比较大,还会耽误项目进度。

后仿真是在HyperLynx SI的BoardSim里进行的,本设计在布线完成后对关键信号和部分重要信号进行了后仿真验证,信号质量均满足信号完整性的要求。

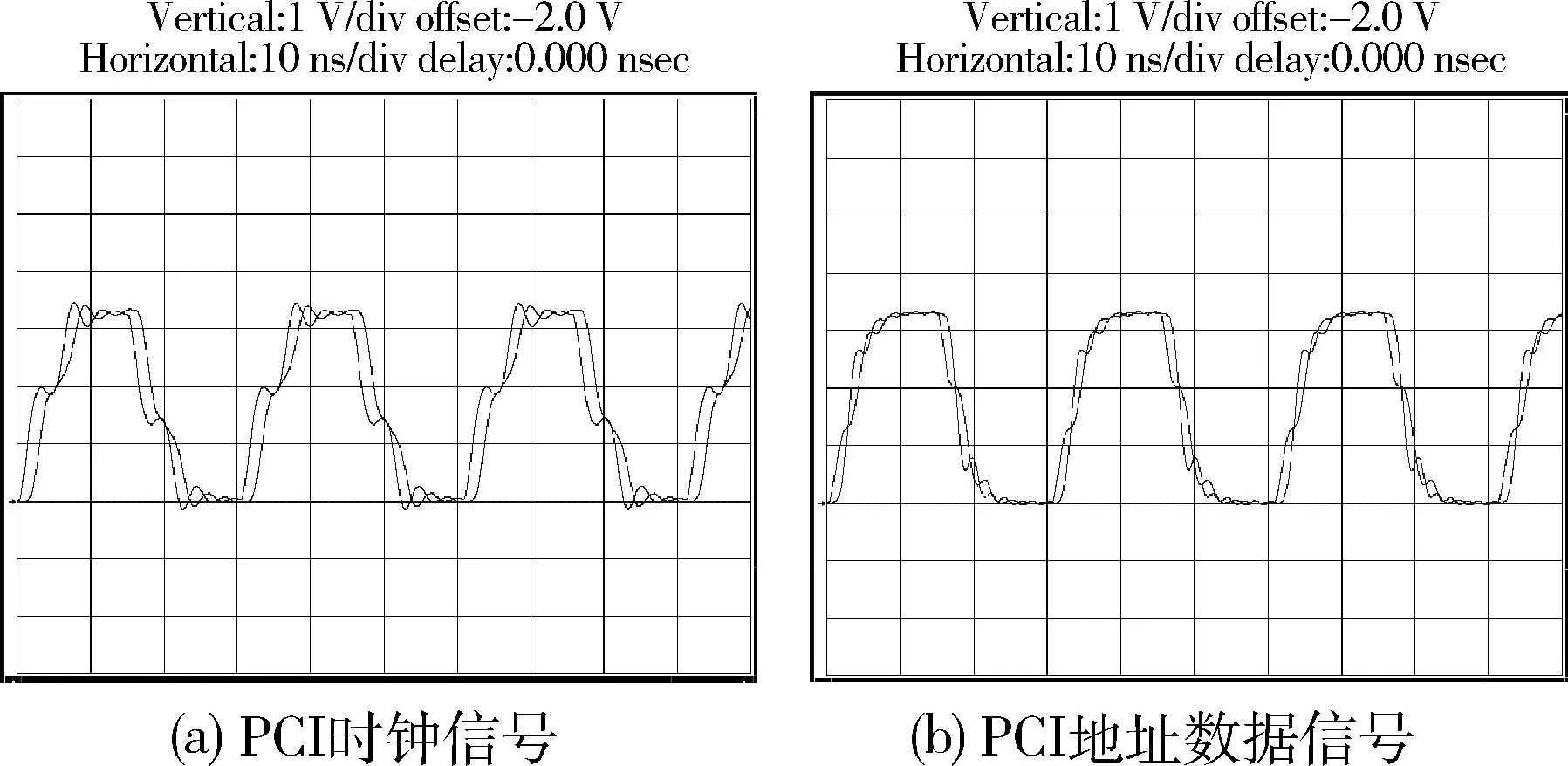

图9给出布线完成后对PCI时钟和地址数据的信号完整性仿真结果。

图9 PCI后仿真验证结果

后仿真验证通过后,在PCB设计工具中进行设计规则DRC检查,检查通过或问题得到确认后,就可以输出Gerber和Drill文件,进行PCB制板、焊接和装配等环节,然后就是硬件电路调试。

该航天计算机主板在硬件电路调试中,采用示波器对关键信号进行了测量,并与HyperLynx SI软件仿真结果进行了比对,测量结果和仿真结果具有较高的一致性,验证了仿真的准确性,仿真对设计也起到了真正的指导作用。

5 结论

本航天计算机主板采用了正确的设计方法,进行了比较充分的信号完整性前仿真和后仿真,灵活运用了高速电路设计的理论并结合以往电路设计的经验,所以,系统在硬件调试时顺利通过。

该航天计算机性能满足设计指标要求,工作稳定可靠,并成功应用到航天项目中,达到了预期的目标。

[1] JOHNSON H, GRAHAM M. High-speed digital design: a handbook of black magic[M].北京:电子工业出版社, 2003.

[2] MPC8240 integrated processor user’s manual[Z]. Motorola Corporation, 1999.

[3] Hyper Lynx signal integrity analysis workbook[Z]. Mentor Graphics, 2012.

[4] 孙宇贞.高速电路的信号完整性分析[J].电子技术应用,2005, 31(3):73-76.

[5] 张志伟.基于时域有限差分法的IBIS模型修正[J].微型机与应用,2011, 30(9):93-95.

[6] 谢金明,著.谭博,改编.高速数字电路设计与噪声控制技术[M].北京:电子工业出版社,2003.

High-speed circuit simulation for the aerospace computer research

Li Yang

(AcconSys Technology Co., Ltd., Beijing 100045, China)

This paper mainly discussed the high-speed circuit simulation used in the aerospace computer research. It introduced the technique and flow of the signal integrity simulation. Through the pre-simulation we get the guidance and through post-simulation we validate the design. The paper describes the flow of high-speed circuit simulation in detail and puts forward what should be paid attention to in the high speed signal design.

signal integrity; crosstalk; electro magnetic compatibility (EMC); pre-simulation; post-simulation; IBIS model

V446+.4

A

10.19358/j.issn.1674- 7720.2017.12.009

李扬.航天计算机研制中的高速电路仿真技术[J].微型机与应用,2017,36(12):29-32.

2016-11-29)

李扬(1975-)男,硕士,SiP/PCB技术专家,主要研究方向:SiP/PCB设计与仿真技术。