基于多核6678的雷达成像信号处理机设计

王鹏飞,樊 勇,经富贵

(1.电子科技大学,成都 611731; 2.中国空空导弹研究院,河南 洛阳 471009)

【光学工程与电子技术】

基于多核6678的雷达成像信号处理机设计

王鹏飞1,2,樊 勇1,经富贵2

(1.电子科技大学,成都 611731; 2.中国空空导弹研究院,河南 洛阳 471009)

为了满足雷达成像信号处理系统大数据处理、快速实时性和高集成度的需求,设计和实现了基于TMS320C6678芯片的雷达信号处理机;TMS320C6678内部集成了8个C66x内核,主频最高为1.25 GHz,能提供高达160GFLOPS的浮点运算性能;本系统采用了FPGA搭配DSP的实施方案,实现了基于一片Kintex7 FPGA和一片TMS320C6678高性能实时信号处理平台,可满足雷达成像系统的算法需求,具有较强的实用价值。

雷达成像;信号处理机;多核DSP;FPGA

由于合成孔径雷达所具有的全天时全天候以及远距离高分辨的特点,使雷达成像技术在军用和民用两个不同领域都发挥重要作用。雷达实时信号处理系统的发展呈现了非常好的态势,其系统功能架构如图1所示,主要包括下述3个模块:数据采集模块;信号处理模块;存储显示模块。

常见的信号处理系统包括基于PowerPC处理器芯片和VxWorks实时操作系统的硬件板卡以及基于DSP和FPGA的硬件板卡。一般来说,雷达信号处理系统选用基于DSP和FPGA的硬件架构,但单核DSP芯片的物理极限对其集成度、功耗和散热等带来的瓶颈问题都导致单核处理器性能不能进一步提高[1]。此时可以通过在一块信号处理板上集成多片DSP或者通过多块信号处理板并行处理来提高运算速度。但受到板卡面积、设计及调试难度、功耗和散热等限制,这样的系统又往往不能满足需求。多核DSP6678的出现改变了这一状况,使得系统功耗和设计难度降低。因此,多核DSP搭配FPGA的架构成为均衡处理性能和功耗等矛盾的有效方法[2]。

在本项目设计中,首次采用FPGA联合多核DSP的硬件架构实现信号处理系统的设计,最终实现具有标准可扩展通信接口、高速数据处理功能、数据传输和存储功能的成像系统。

图1 雷达成像信号处理系统功能

1 总体设计思路

基于雷达成像算法步骤多、复杂度高、计算量大的特点,往往受限于其处理速度和处理时间而难以满足平台实时性的要求。因此,本系统充分利用FPGA的流水性能和多核DSP的并行处理能力,将算法合理分配到不同的处理器中,总体成像算法流程如图2所示[3]。具体来说,处理系统接收从前端传来的雷达回波数据,通过AD对原始数据进行采样即模数转换,采样后的数据送至FPGA进行数字下变频和距离向脉冲压缩操作。脉压后的基带信号以脉冲重复频率通过SRIO接口实时将每个脉冲的回波数据发送至DSP进行剩余成像算法的处理。DSP处理完成后的图像数据可以进一步用来实现图像匹配和平台定位,满足平台精确制导的需求[4]。

为满足上述算法需求,本系统的信号处理模块采用FPGA 搭配 DSP的实施方案,FPGA采用了“一大一小”的设计思路,分别选取一片Spartan-3系列的FPGA和一片Kintex7(以下简称K7)系列的FPGA,其中Spartan-3系列的FPGA作用主要是低功耗、上电顺序和简单的逻辑控制,而K7系列的FPGA则主要负责数据的预处理、与DSP进行高速数据传输。DSP主要完成复杂实时成像处理算法的实现。

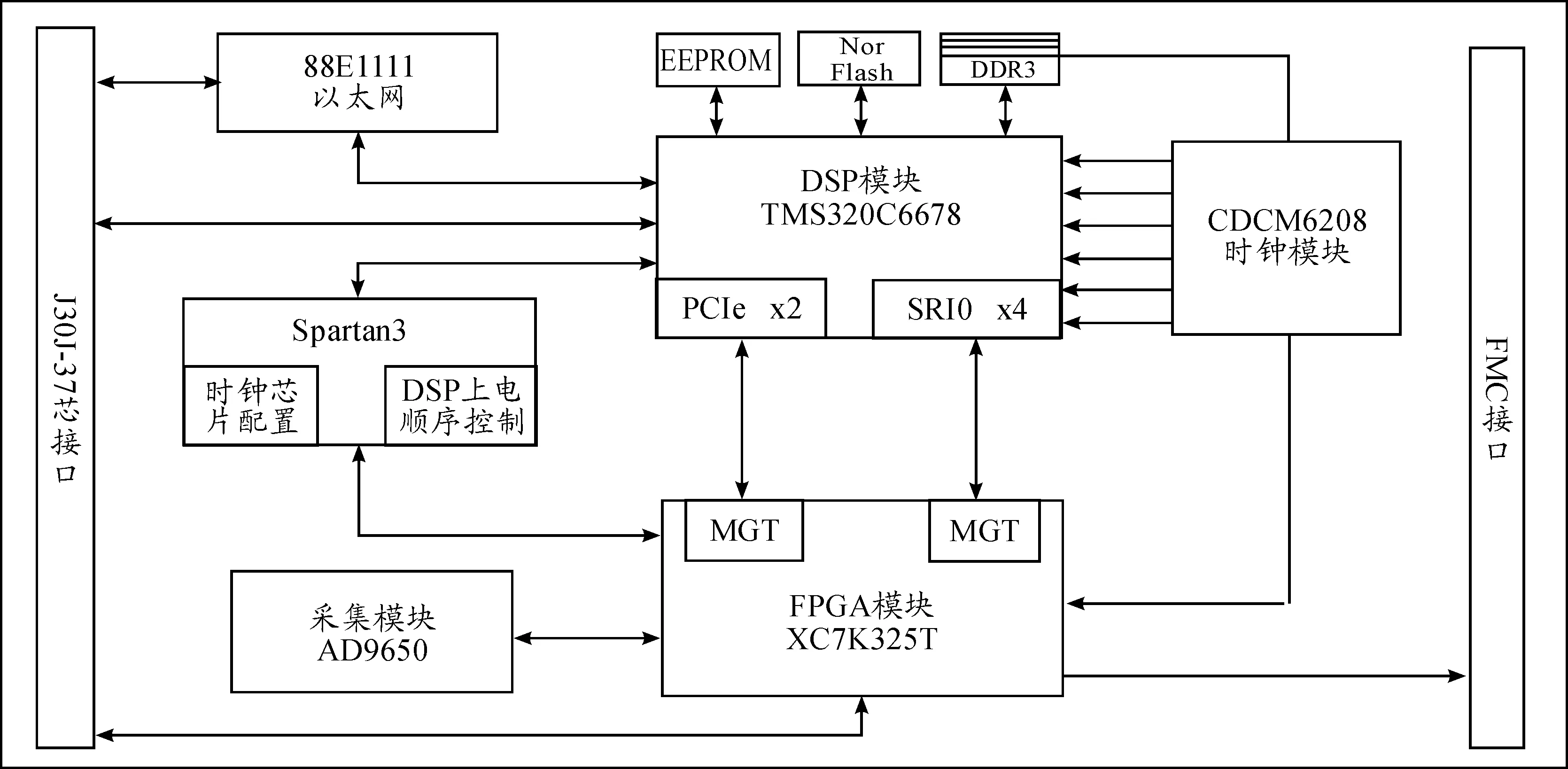

信号处理系统硬件框图如图3所示。其中A/D芯片与FPGA通过16对LVDS相连; FPGA与DSP通过Serial Rapid IO接口进行高速数据传输,时钟芯片用于提供各种所需时钟,DSP通过千兆以太网与上位机通信,用来实时显示成像结果;FPGA与弹体之间惯导信息的传输则是通过RS422接口实现。

图2 雷达成像算法流程

图3 信号处理系统硬件框图

2 信号处理机设计

信号处理板卡由AD采集模块、DSP模块、FPGA模块、时钟模块和电源模块等组成[5],下面就各模块设计过程分别介绍。

2.1 AD采集模块设计

AD采集芯片选用ADI公司的AD9650,该芯片能提供双通道16位、最高105MSPS的数据采样,在工业、医疗、通信等方面应用广泛。

AD采集模块需要对模拟器传送过来的I、Q两路数据进行采样,为方便FPGA对数据进行抽样处理,通过SPI接口对AD9650进行配置,使其工作在交叉模式下。交叉模式下AD9650与FPGA的互联接口如图4所示。

图4 FPGA与AD的互联接口

AD9650的配置流程如下:当RESET无效,CSB为低即有效时,以SCLK为节拍,将对应的配置参数通过端口SDIO以串行方式输入到AD9650中,如此就完成了AD芯片的配置,而相关信号的时序关系是由FPGA完成。配置完成后I、Q两路模拟信号分别由端口A和端口B输出,随路时钟由端口DCOA和DCOB输出。

2.2 DSP模块设计

本系统所选用的DSP为TI公司在2011年推出的采用全新Keystone架构和全新C66x内核的高性能多核浮点型DSP处理器C6678。

C6678的供电比较特殊,需要依据一定的上电顺序,此顺序通过SP3-AN FPGA控制电源芯片实现。

C6678要求的时钟类型也比较多,除了核时钟以外,还需要DDR时钟,SRIO时钟,PCIE时钟,Hyperlink时钟等。

DSP在与DDR3在连接时,4片DDR3 SDRAM共用相同的地址线,64根地址线分成4组,每组16bit,分别连接到每片DDR3 SDRAM的数据线上。DDRDQM 0到DDRDQM 7和DQS0P(N)到DQS7P(N)也分成4组接到4片DDR3上,其余的控制线4片DDR3共用。

DSP的SGMII1发送差分对与以太网物理层芯片的S_IN+(-)连接,接收差分对与S_OUT+(-)连接,同时MDC和MDIO也与以太网芯片相应的MDC和MDIO连接。以太网芯片的MDI0/1/2/3P(N)连接HX5004NL收发器,HX5004NL再与37针接插件进行连接,通过该接插件就可以与上位机进行以太网通信了。

2.3 FPGA模块设计

本信号处理系统FPGA模块中使用的两款芯片分别是XC3S700AN-FGG484和K7系列中的XC7K325TFFG900。前者负责对DSP进行上电顺序的控制,时钟控制及对K7进行加载控制;后者则负责数据的输入输出控制以及和DSP的通信。

XC3S700AN的系统时钟利用3.3 V供电的50 MHz有源晶振提供。为了便于进行程序调试,XC3S700AN FPGA外部连接了两个复位按钮和两个3脚的插针,可以通过跳线帽同时结合程序来进行模式的选择,同时还连接了5个LED灯,方便了程序测试。

XC3S700AN的加载采用了芯片本身自带的flash,并没有外挂用于其加载的芯片。使用自身的flash加载时非常方便,在JTAG在线仿真模式下,利用ISE的IMPACT烧写软件即能很方便的对XC3S700AN进行擦除和烧写操作。

K7利用其高速GTX模块实现与DSP之间的SRIO和PCIe高速互联。K7的MGT BANK115与DSP的SRIO接口进行连接,MGT BANK117与DSP的PCIe接口进行连接。同时FPGA连接带隔离的RS422信号,用于和外部的通信。

2.4 时钟模块设计

板卡核心器件较多,功能复杂,因此提供稳定、正确的时钟是保证板卡正常工作的重要前提。系统板卡使用了一个DSP芯片和一个FPGA芯片,因此共需要至少7个时钟资源。为了精确产生这些时钟,就必须使用专门的可编程的时钟分发芯片,为了节省空间,该时钟分发芯片还应该具有多路输出。综合考虑以上因素,选择了TI公司的CDCM6208频率合成器。

使用一个SMA接口输入AD9650的100 MHz同步采样时钟;使用2个50 MHz的有源单端晶振,分别作为K7 FPGA和XC3S700AN FPGA的全局时钟;1个25 MHz无源差分晶振和1片CDCM6208满足DSP和K7 FPGA的其他时钟需求。25 MHz的晶振从SEC_REF输入充当第1片CDCM6208的时钟输入源。电路设计时外围滤波电路的设计非常重要,其相应的电容电阻值可以参考数据手册进行设定。

2.5 电源模块设计

对于嵌入式系统而言,良好的电源设计是整个系统正常稳定工作的前提条件,其关键是满足系统功耗要求,并提供功耗余量(图5)。现对本设计的板卡做出功耗估计和供电分配,说明如下:

信号处理板卡中的大功耗器件主要集中于:DSP芯片TMS320C6678 (每片功耗10 W左右,共1片);FPGA芯片XC7K325T (8 W左右);以太网交换芯片88E1111;DDR3 SDRAM存储器(每片功耗约0.2 W,共4片)。

设计中使用到的核心器件较多,并且处理器内核频率以及接口速度较高,因此该系统对供电的要求很高。

图5 系统电源设计

3 结论

本文以雷达成像系统信号处理机设计为应用背景,基于TI 6678高性能多核DSP,配合K7 FPGA的超强处理能力,从AD采集、DSP、FPGA、时钟和电源五大方面对本信号处理系统进行了设计,最终实现的信号处理机能够满足雷达实时成像系统的算法需求。

[1] 郭凯,徐红侠.基于TMS320C6678的雷达信号处理实现[J].山东工业技术,2016(7):209.

[2] VITYAZEV S,KHARIN A,SAVOSTYANOV V,et al.TMS320C66x multicore DSP efficiency in radar imaging applications[C]//2015 4th Mediterranean Conference on Embedded Computing (MECO),Budva,2015.

[3] 李艳红.FMCW微型SAR成像信号处理技术研究与硬件实现[D].西安:西安电子科技大学,2013:27-30.

[4] ZHANG N,YAO D,LI C,et al.A real-time processing system for airborne forward-squint SAR based on DSP[C]//IET International Radar Conference 2015,Hangzhou,2015.

[5] 原涛.弹载SAR实时成像信号处理机设计[D].西安:西安电子科技大学,2013:28-30.

[6] 孔舒亚,叶伟,班红艳,等.压缩感知合成孔径雷达射频干扰抑制方法[J].兵器装备工程学报,2016(2):119-122.

(责任编辑 杨继森)

Research of SAR Signal Processor Based on Multicore DSP 6678

WANG Peng-fei1, 2, FAN Yong1, JING Fu-gui2

(1.University of Electronic Science and Technology, Chengdu 611731, China; 2.China Airborne Missile Academy, Luoyang 471009, China)

To meet the needs of radar signal processor for real-time big data processing and high integration, this paper designed and realized the processor based on TMS320C6678. TMS320C6678 has integrated eight C66x kernels with the highest processor speed of 1.25 GHz and can perform 160 G floating-point operations per second. The high performance real-time signal processor has been realized based on the architect of one Kintex7 FPGA plus one TMS320C6678 DSP chip. In conclusion, the signal processor can perfectly satisfy the demands of algorithm for SAR system and has comparatively higher practical value.

SAR; signal processor; multicore DSP; FPGA

2016-12-27;

2017-01-25 作者简介:王鹏飞(1982—),男,硕士,高级工程师,主要从事雷达信号处理研究;樊勇(1977—),男,博士,教授,主要从事雷达信号处理研究;经富贵(1963—),男,硕士,研究员,主要从事雷达信号处理研究。

10.11809/scbgxb2017.05.035

format:WANG Peng-fei, FAN Yong,JING Fu-gui.Research of SAR Signal Processor Based on Multicore DSP 6678[J].Journal of Ordnance Equipment Engineering,2017(5):151-154.

TJ451

A

2096-2304(2017)05-0151-04

本文引用格式:王鹏飞,樊勇,经富贵.基于多核6678的雷达成像信号处理机设计[J].兵器装备工程学报,2017(5):151-154.

——信号处理