基于DSP和FPGA的被动声探测实时采集系统设计

孙昌君, 李立京, 郑 帅, 宋舒雯

(北京航空航天大学 仪器科学与光电工程学院,北京 100191)

基于DSP和FPGA的被动声探测实时采集系统设计

孙昌君, 李立京, 郑 帅, 宋舒雯

(北京航空航天大学 仪器科学与光电工程学院,北京 100191)

为了给被动声探测技术研究提供实验验证平台,设计了一种可以进行实时数据采集和处理的系统方案。整个系统以数字信号处理器(DSP)和现场可编程门阵列(FPGA)为基本架构,由FPGA控制模数转换器(ADC)采集数据,通过USB 2.0电路将数据传送给个人计算机(PC),用于初期的离线验证;FPGA将采集到的数据通过外部存储器接口(EMIF)传递给DSP,用于实时处理。实验证明:系统实现了被动声探测中的实时数据采集、离线数据存储。数据采集与数据处理分别由不同处理器执行,提高了系统的响应速度与处理性能,能够满足探测系统的实时性要求。

被动声探测; 数据采集; 数字信号处理器; 现场可编程门阵列

0 引 言

被动声探测技术是利用声传感器获取声音信息,以实现对目标识别和定位的技术。被动声探测技术具有独特的优势[1]:隐蔽性好,不易被发现和摧毁;不受光线和可见度限制;声波绕射能力强,没有雷达、红外等探测的工作盲区;系统结构简单,成本低。目前,在军事领域、工业领域、医疗领域、安全监控等领域均有着广泛的应用。特别在军事领域,我国在20世纪90年代开始进行研究,目前还未见成熟产品[2]。

小基阵被动声探测系统放布灵活、便携,即可独立测定目标方位,又可联合测定目标的坐标[2]。本文在研究4元小基阵声传感器被动声探测系统的基础上,设计了基于数字信号处理器(DSP)与现场可编辑门阵列(FPGA)的被动声探测实时数据采集系统。实现了实时数据采集与处理,同时,在系统执行过程中可以将采集的数据实时传送到上位机中进行数据处理与存储,离线存储的数据可用于Matlab算法验证与优化。不同于以往的单处理器同时进行数据采集与处理,系统的执行效率低,该系统充分发挥了FPGA高速信号采集与DSP高效信号处理能力,提高了效率。

1 系统方案设计

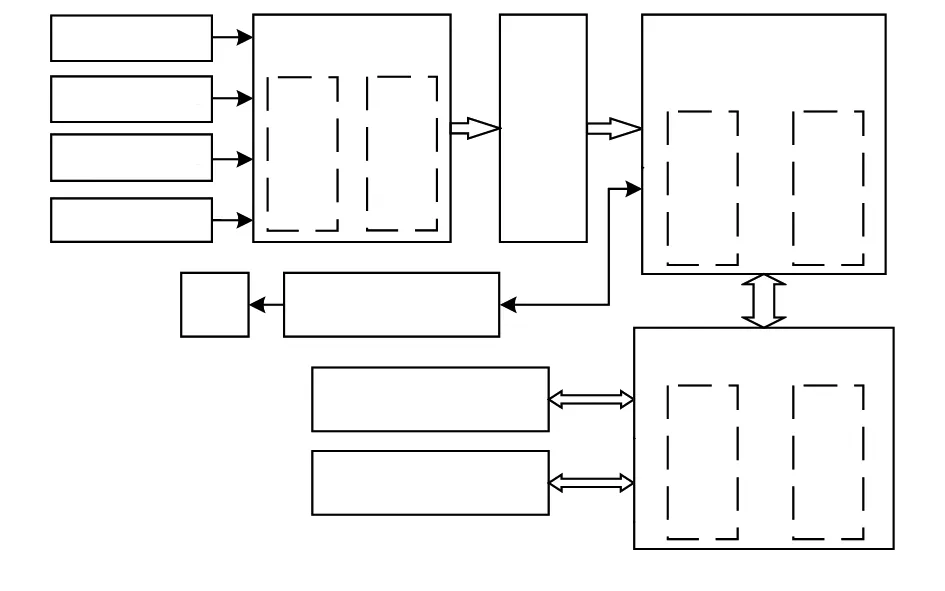

本文设计了基于光纤声传感器的被动声探测实时信号采集系统,系统框架设计如图1所示。

图1 系统框架图

4路声传感器输出的模拟信号,经过信号预处理后,由FPGA控制ADC采集信号,判断是否检测到声源目标,实现目标预警。在未检测到有效信号时, DSP处于休眠状态,以降低系统功耗。检测到有效信号后FPGA发送信号唤醒DSP,将采集的数据通过EMIF接口传送给DSP,由DSP进行数据处理。系统设计了USB接口用于实时离线数据采集,实现算法离线验证、优化。

2 系统硬件电路设计

2.1 信号预处理电路与ADC采集电路

信号预处理电路将声传感器接收的信号进行无失真放大、噪声滤除。其硬件电路由前置放大电路、滤波电路、自动增益控制电路组成[3,4]。系统采用高精度仪表运算放大器INA128作为前置放大器,用于信号放大、阻抗匹配。滤波用于滤掉信号中的高频噪声和低频漂移,提高信噪比。系统采用MAXIM公司单片集成的连续时间有源滤波器MAX274构造带通滤波器[5]。当声源目标距离变化较大时,声传感器接收的信号强弱相差很大。为使信号平稳,放大器选用数控增益[6,7]。系统采用AD公司的程控增益放大器AD526进行增益控制。增益控制器选用内部集成ADC的MSP430F5529低功耗单片机。

系统采集的目标主要为低频声音信号,频率低于1 kHz,时延估计精度随采样频率的提高而提高,综合考虑系统运算量,选用AD公司的四通道采样频率为200 kSPS的16位同步采样ADC—AD7606,能够满足系统需求。AD7606内部基准电压源存在一定漂移,因此,采用2.5 V低噪声低漂移电源芯片ADR421AR作为参考源。

2.2 USB2.0通信电路

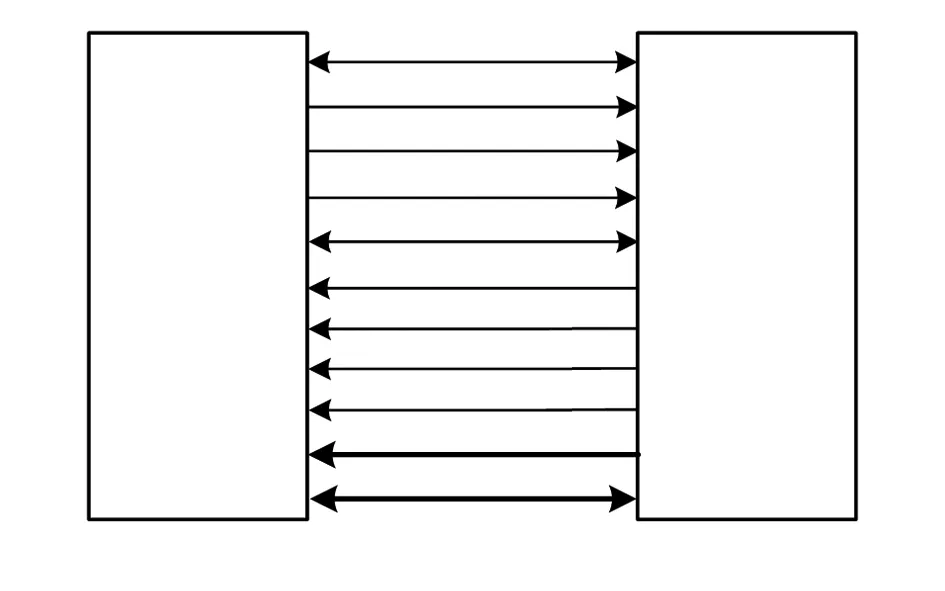

USB2.0通信模块将ADC采集的数据实时保存到PC中,用于离线数据处理及算法优化。系统采用CYPRESS公司的USB2.0芯片CY7C68013A,由于芯片内部没有存储器,外部连接一片E2PROM存储USB驱动程序。数据端口采用8位数据线,以节约I/O开销。USB的时序由FPGA控制,两者之间的通信连接图如图2所示。

图2 USB通信连接图

2.3 DSP模块电路

系统需要实现算法的实时处理,目前C6000系列的DSP芯片浮点数据处理能力较强,适合进行算法实时处理。系统采用TI公司的低功耗浮点型处理器TMS320C6748,其内核为C674x,最高主频可达456 MHz,运算能力可达3 648/2 746 MIPS/MFLOPS。

2.3.1 DSP外围接口

EMIF控制器是DSP中的储存器控制器,为CPU提供一种和外部多种存储器连接的方法[8]。C6748具有一个EMIF接口EMIFA,其时钟频率可达100 MHz。系统通过EMIFA接口连接FLASH和FPGA。FLASH采用Spansion公司的NAND FLASH S34ML01G200TFI00。EMIF与FPGA通信中将FPGA作为异步存储器进行操作。

C6748具有DDR2专用接口,DDR2功耗低、速度快,能够以4倍外部总线的速度读写数据,能够降低数据读写带来的延迟。系统采用Micon公司的DDR2 SDRAM MT47H64M16HR—25,时钟信号采用差分时钟,最高频率达150 MHz。

2.3.2 DSP与FPGA通信接口电路

FPGA采用Xilinx公司的Spartan—6系列,型号为XC6SLX16—3CSG324C。系统采用的配置模式为主串模式,存储器选用Xilinx公司的XCF04S—VO20C。

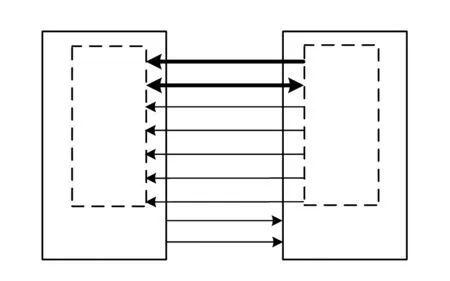

在DSP与FPGA的通信中,FPGA利用内部的RAM构建存储器,FPGA设计为DSP的一个外部存储器,FPGA将采集的数据存放到构建的存储器中,存储完成后发出中断信号,DSP通过EMIFA接口读取数据,从而实现DSP与FPGA的并行通信[8]。文中在FPGA内部构建真实的双口RAM。FPGA中双口RAM的实现采用Xilinx CORE GeneratorTM工具中的IP核Block Memory Generator。DSP作为从设备,由FPGA控制其复位,通信连接图如图3所示。

图3 DSP与FPGA通信连接图

3 系统软件设计

设计主要包括FPGA端和DSP端。FPGA端包括:ADC控制、USB控制、EMIFA通信。DSP端主要包括EDMA数据传输和算法处理。

3.1 FPGA端软件设计

3.1.1 ADC控制

ADC由FPGA进行逻辑控制,能够实现高效、精准的控制[9]。首先进行ADC初始化:复位芯片、设置采样模式;启动ADC转换器;FPGA循环检测忙信号,判断是否完成转换,当转换完成便关闭转换信号,进行4通道信号读取;读取数据时依次读取各通道数据,由拉低读信号控制时序,读信号连续拉低4次完成数据的读取;读取完成后由FPGA将数据存储到内部的RAM中,之后向DSP发送中断信号,同时开启ADC转换信号,进行下一次转换。

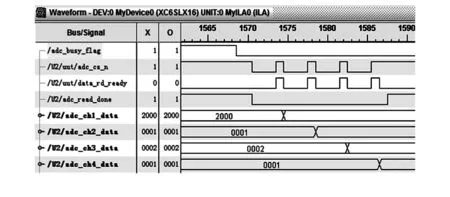

连接硬件系统,将AD通道1连接2.5 V电压,对应数字量2 000,其它通道接地。利用逻辑分析仪ChipScope对AD采集硬件在线仿真的时序图如图4所示。

图4 ADC控制在线仿真时序图

3.1.2 USB通信

USB通信由FPGA控制,用于将ADC采集的数据传输到PC机中。系统写数据为主,采用同步Slave FIFO的块传输模式。写时序主要由5个状态。空闲状态:ADC一次转换完成时触发写事件,进入状态1;状态1:根据FIFOADR指向的地址选择端点号后进入状态2;状态2:根据所选择端点的FIFO状态标志位,确定是否将数据写入,若FIFO为满状态,则在该状态等待,直至满状态无效时进入状态3;状态3:保持写信号SLWR有效,将待写入数据送入数据线上,持续一个IFCLK时钟后进入状态4;状态4:若继续写入数据则进入状态2,否则写入完成并进入空闲状态。

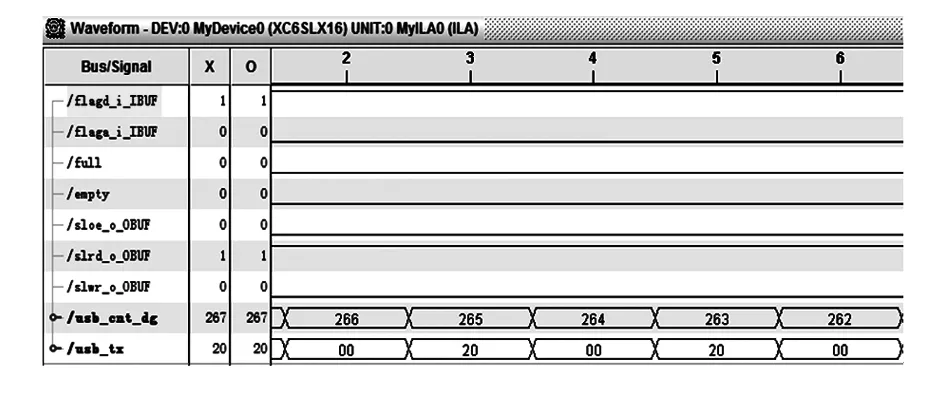

将ADC采集数据CH1通道数据写入USB中,利用ChipScope对USB2.0通信在线仿真的时序图如图5所示。

图5 USB2.0通信在线仿真时序图

3.1.3 EMIFA通信

FPGA端将传递的数据准备好后,通过I/O端口向C6748发出中断请求,通知C6748读取数据。C6748在中断服务函数中读取数据,当C6748读数据时,拉低片选EMA_CS2、读使能EMA_OE,拉高写使能EMA_WE;信号在操作地址时由DSP内部逻辑自动完成。FPGA通过检测片选、读使能、写使能三个信号判断DSP的读请求,检测到读请求时,将相应地址的数据送至数据总线[6]。

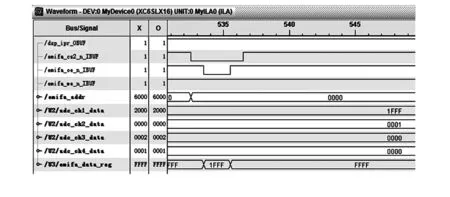

将C6748程序下载到FLASH中,保证DSP正常工作,利用ChipScope对FPGA与C6748通信过程在线仿真的时序图如图6所示。

图6 EMIFA通信在线仿真时序图

3.2 DSP端软件设计

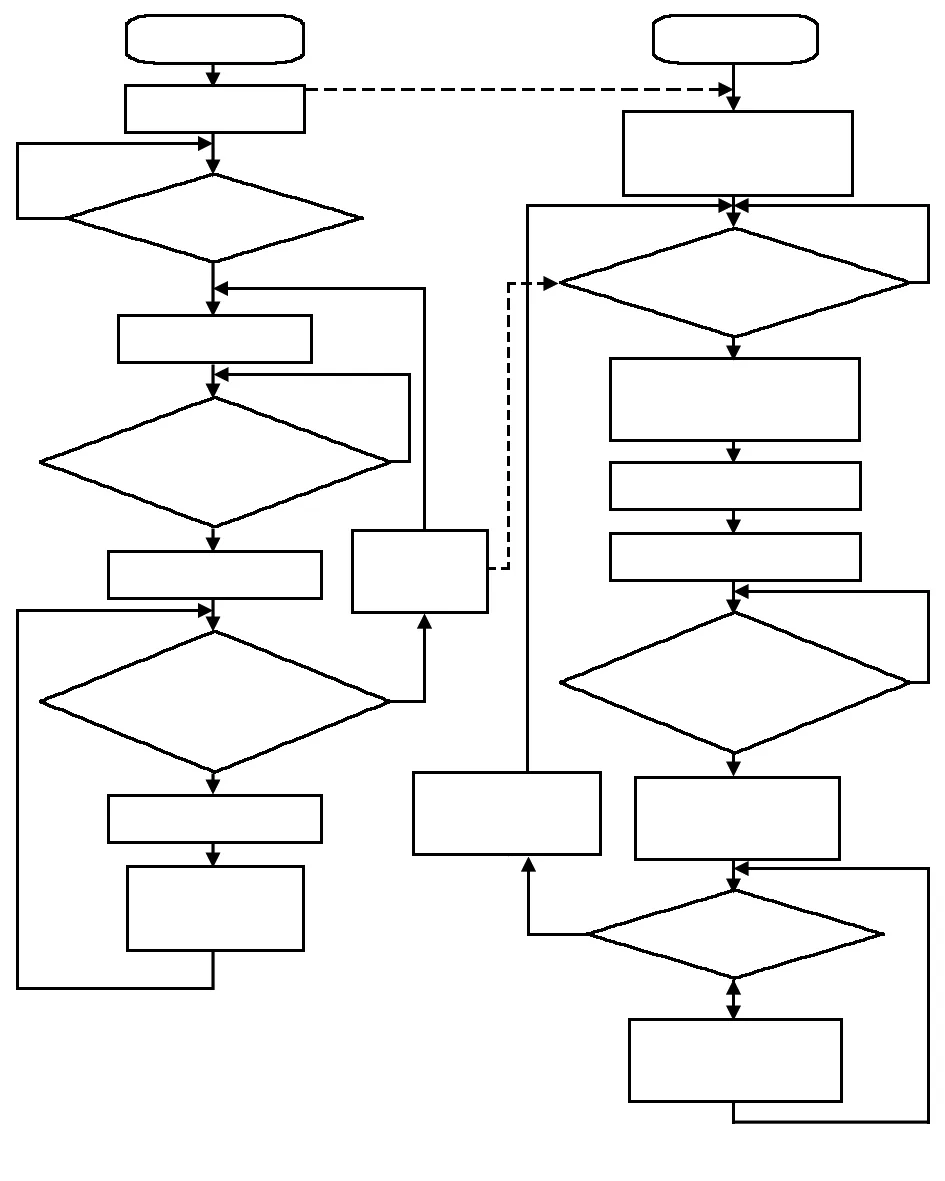

C6748上电后,由FPGA控制其复位,之后进行系统初始化。DSP初始化主要包括:PLL初始化,DDR2初始化,FLASH初始化,I/O初始化,EMIFA初始化,中断初始化,PSC模块管理初始化。当FPGA准备好一次传输的数据时发出一个脉冲信号,C6748的I/O0[14]管脚中断设置为上升沿触发。当检测到上升沿时触发I/O中断,C6748内部的EDMA3控制器检测到GPIO中断事件,触发EDMA3传输中断,将数据快速转移到C6748的DDR2存储器中。在传输过程中,设置一个计数器,在每次存储数据时累加,将存储深度设为1 024,当存储的数据量达到系统预设长度时,关闭I/O外部中断、停止数据存储,由CPU进行数据处理,完成时延估计与定位解算,系统的程序流程如图7所示。

图7 系统软件流程

4 系统测试

为了验证系统的准确性,进行了实际采集测试,系统声传感器采用全方位、副相一致性好的光纤声传感器MKM—1150。声传感器频率响应范围为10~14 kHz,灵敏度为100 mV/Pa。阵列为间距1m的4元十字阵,将传感器置于十字臂前端。信息采集的对象为人的声音,硬件系统采样率设置为100 kHz,在离线数据采集中通过USB将数据传送至PC保存,利用Matlab截取1 024个采样点进行绘制得到采集的4路声音信号如图8所示。

图8 4路声音信号波形图

5 结 论

本文完成了基于DSP与FPGA硬件架构的被动声探测实时数据采集系统的设计,实现了实时数据采集、离线数据存储。数据采集与数据处理分别由不同处理器执行,提高了系统的响应速度与处理性能,能够满足探测系统的实时性要求。系统结构紧凑、低功耗、实时性强。经过测试ADC采样率为100 kSPS情况下,USB2.0离线数据采集速率测试达31.14 MB/s,满足需求;EMIFA接口通信中速率可达46.96 MB/s。系统为被动声探测技术的研究和算法验证提供了良好的实验平台方案,具有很高的实际应用价值。

[1] 靳 莹,杨润泽.声测定位技术的研究现状[J].电声基础,2007,31(2):4-8.

[2] 马弛州,滕鹏晓,杨亦春,等. 分布式实时被动声定位系统研究[J].探测与控制学报,2007,29(1):18-22.

[3] 王燕妮.被动声探测定位技术研究[D].太原:中北大学,2006.

[4] 曹一江,孙志斌,刘 晓,等.为驻极体声传感器信号采集系统研究[J].传感器与微系统,2006,25(10):19-21.

[5] 王 辉.声红外复合末敏弹的声探测技术研究[D].南京:南京理工大学,2007.

[6] 许占伟.基于DSP的被动声定位技术研究[D].南京:南京理工大学,2002.

[7] 蔡克荣,陈 铭.基于五元立体声阵的被动定位系统设计[J].传感器与微系统,2016,35(4):67-72.

[8] 李 凯.基于TMS320C6748高速DSP信号处理模块设计[D].哈尔滨:哈尔滨工程大学,2013.

[9] 綦 磊,张 涛,梅 玮,等.基于FPGA的高速信号采集平台设计[J].传感器与微系统,2011,30(9):79-81.

Design of real-time data acquisition system for passive acoustic detection based on DSP and FPGA

SUN Chang-jun, LI Li-jing, ZHENG Shuai, SONG Shu-wen

(School of Instrument Science and Opto-electronics Engineering,Beihang University,Beijing 100191,China)

In order to provide experimental verification platform for passive acoustic detection technology research,a system scheme for real-time data acquisition and processing is designed.The system is based on digital signal processor(DSP)and field programmable gate array(FPGA).FPGA controls the anolog digital converter(ADC)collecting data and transferring data to PC through USB 2.0 circuit for early off-line verification; FPGA transfers the collected data to DSP though external memory interface(EMIF)for real-time processing.Experiment shows that the system realizes the real-time data acquisition,off-line data storage in the passive acoustic detection system.The data acquisition and data processing are carried out by different processors which can improve response speed and processing performance of the system and satisfy the real-time requirement of the system.

passive acoustic detection; data acquisition; digital signal processor(DSP); field programmable gate array(FPGA)

2016—06—24

10.13873/J.1000—9787(2017)06—0105—03

TN 912.11

A

1000—9787(2017)06—0105—03

孙昌君(1990-),男,硕士研究生,研究方向为探测制导与控制,E-mail:changjun_sun@163.com。