硬件加速对处理器性能提高的探索

■ 刘 超 刘召庆 雒 俊 赵 博 张丹惠

军方园地

硬件加速对处理器性能提高的探索

■ 刘 超 刘召庆 雒 俊 赵 博 张丹惠

FIR(有限冲激响应)、IIR(无限冲激响应)和FFT(快速傅里叶变换)三种信号处理技术被广泛应用于硬件加速器的实现上。硬件加速器能减轻CPU的负担,潜在的提升处理器的计算吞吐率,一般认为其效能至少不低于CPU效能的2倍。本文以某型DSP处理器处理模拟量输入系统为例,说明硬件加速器在这方面的应用。

1.前言

简单地说,硬件加速器技术的出现源于CPU处理能力的不足,或是已达到其处理能力的上限,需要通过某种预先处理技术进行先期任务的分担,或优化任务结构,使之整体任务的处理能力得到提高,而CPU还是原来的CPU。目前广泛应用的技术有:

● FIR滤波器:有限冲激响应序列变换处理;

● IIR滤波器:无限冲激响应序列变换处理;

● FFT操作:快速傅里叶变换,倒位序交换蝶式计算;

这些方法的应用背景均基于数字信号处理技术。

1.1 硬件加速器的应用背景

FIR滤波器、IIR滤波器和FFT操作在数字信号处理中的应用十分普遍,且具有规则的结构,因此可以用硬件直接实现,特别是用硬件加速器。硬件加速器是专用的定点功能外设,适用于单个任务的重复计算。它减轻了主处理器的负担,而主处理器主要做一些在结构上几乎没有什么规律的通用任务。

由于系统既拥有通用处理器的普遍适用性,同时又具有专用硬件计算的高效性,因此为提高处理器总的计算能力,硬件加速器的使用成为了一种性价比较高的方法。

1.2 硬件加速器的飞控模拟量概念

硬件加速器在满足日益复杂系统需求的众多应用领域方面具有重要价值。其应用之一是其通道数不断上升的模拟量数字化输入处理系统。当飞行器控制系统的模拟量数字化输入处理特征状态数从5.1通道发展到6.1通道、7.1通道,以至于更复杂飞行器控制系统一般使用的12个或者更多的模拟量数字化输入处理,飞机自动控制则处于更加平稳和安全的状态。

此外,模拟量数字化输入现在采用时序串编码格式,其相关的编码器扩展了系统资源。时序串编码算法还以更高的采样率处理数据。以往数据的峰值采样率很少超过48kHz,随着时序串编码算法的采用,现在采样率通常为96kHz,甚至达到了192kHz。

2.模拟量数字化处理原理

为了更好的理解计算需求是如何增加的,考虑一般飞机的自动控制系统,它集成了复杂的飞行均衡算法,用以补偿振动响应和位置长度差异时延所引起的偏差。算法首先利用麦克斯威尔噪声分析飞行环境,并测量实时传递函数。对飞机多个不同位置进行测量再进行组合分析,然后为每个模拟量输入设计一个补偿滤波器。

更精确的飞行模拟量均衡算法则使用FIR滤波器来校正整个频率范围的响应函数,滤波器长度与采样率直接成比例。低频控制越精确,需要的滤波器长度越长。采样率为48kHz时,通常滤波器的长度为256点,为了达到同样的频率分辨率,在96kHz时则需要滤波器的长度为512点。采样率和滤波器长度均加倍则导致所需的总计算量增加了4倍。

2.1硬件加速器结构

ADI公司近期推出的SHARC ADSP-2146x处理器是典型的DSP加速处理器,通过该型芯片的实现可掌握硬件加速的基本原理和思路,其加速器的基本结构逻辑清晰,处理器具有更高的时钟速率(450MHz),片上存储器(5Mb)也得到了扩展。

此外,该处理器还具有一系列硬件加速器,可用于实现通用信号处理运算:FIR滤波器、IIR滤波器和FFT。而这些运算通常是通信系统、医疗设备、消费产品、工业测量和控制应用中的基本运算。这些加速器是SHARC ADSP-2136x系列处理器片内采样率转换器的有益补充,而采样率转换器也可以看作硬件加速器。

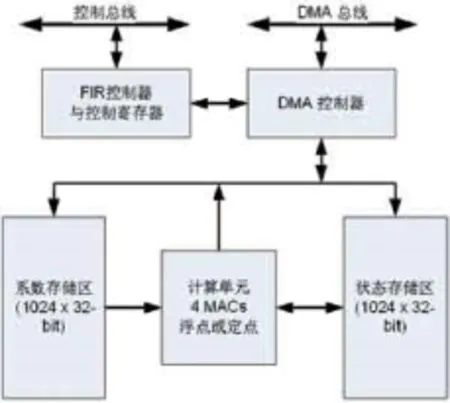

图1 FIR加速器的结构

SHARC ADSP-2146x处理器的三个加速器设计相同,图1所示的FIR加速器能很好的说明硬件加速器的结构。

FIR加速器有以下功能模块:

● 系列控制寄存器——配置加速器的操作。

● DMA控制器——在主存储器与加速器的本地存储器之间传输数据,也可用于配置控制寄存器。

● 两个本地存储器块——保存系数和状态变量(或者延迟存储器),并降低主存储器的带宽。

● 计算单元——包括适合加速器的算术操作,FIR的计算单元有4个并行的MAC。

2.2 硬件加速器操作的基本步骤

一般使用链式DMA,加速器的操作可以自动完成,FIR加速器的操作步骤具有典型性,IIR滤波器和FFT操作均可以此为例。

其典型操作分为以下几步。

(1)将本通道的系数数据由内部存储器载入本地加速器系数存储区。

(2)将本通道的状态变量从内部存储器载入本地加速器系数存储区,包括第一个输入样本。

(3)利用四个MAC单元计算输出样本。

(4)保存结果。

(5)如果还有需要处理的样本,则读取下一个输入样本,并写入状态变量存储器。

(6)重复步骤(3)~(5),直到通道中的所有输出样本计算完成。

(7)重复步骤(1)~(6),计算所有输入通道。

3.加速器的实际应用

应用软件的设计应当尽可能考虑从硬件加速器获取更多的好处,应牢记加速器必须配置成与主CPU并行操作的规律,如果主CPU处于空闲状态等待加速器完成操作,这将不会产生更高的效率。

加速器是实时环境中运行的大信号链的典型部分,加速器接口需要双缓存的输入和输出数据,系统设计人员应该牢记加速器会带来一部分延时。

设想一个带有7.1通道的飞控模拟量数字化输入系统,采样率为96kHz,数据块的大小为32个采样点,假定飞机内均衡应用8个FIR滤波器,每个滤波器的长度为512点,如果采用多核CPU执行滤波操作,则至少需要:

96kHz/s×8×512=393MMAC(个操作.每秒)

或者为工作在450MHz的SHARC处理器运算量的44%。该FIR处理占据了整个计算量很大的一部分,但如果使用了硬件加速器,这些运算量都可转交加速器来处理。FIR滤波器的输入和输出均采用双缓冲,这就可以让加速器与音频信号处理链的最后环节并行处理。当然,双缓冲器会引入32个采样点的处理延迟,96kHz时延迟为333ms,这种情况是可以接受的。

利用上面的计算公式,加速器需要50056个外设时钟周期才能完成操作,如果外设时钟是225MHz,则需要223ms,小于333ms的可用块处理时间。

4.结束语

飞行控制模拟量数字化处理技术的进一步发展对任务处理器DSP/ CPU提出了更高的要求,集成硬件加速器为处理器整体处理性能的提升提供了重要的推动力,将通用的信号处理操作——FIR滤波、IIR滤波和FFT操作——从内核处理器中释放出来,使内核可以专注于其它任务,这种方法性价比高,可使处理器的计算吞吐量提高两倍以上。本文主要讨论了模拟量的数字化应用,然而处理器和加速器是通用的,也适用于各种信号的处理任务,如离散量的输出。

(作者单位:刘超、雒俊、张丹惠,陆军航空兵军代局驻西安地区军代室;刘召庆、赵博,西安应用光学研究所)