基于GaAs HBT工艺的动态分频器的研究与设计

梁方建,闫广涛,卢 震

(1.国网商丘供电公司 河南 商丘476000;2.天津大学 天津300072)

基于GaAs HBT工艺的动态分频器的研究与设计

梁方建1,闫广涛1,卢 震2

(1.国网商丘供电公司 河南 商丘476000;2.天津大学 天津300072)

针对静态分频器工作频率越高功耗越大的问题,本文采用GaAs HBT工艺研究设计了高性能动态分频器。通过对动态分频器结构进行研究,采用有源负载代替传统的电阻负载,提高了分频器工作的频率。同时对动态分频器进行电路设计,并对其进行仿真,得出其分频范围为9~15 GHz,具有良好的输入灵活度,功耗仅为130.26mW,满足设计要求。

分频器;GaAs HBT;锁相环;直流功耗

随着各类无线通信技术蓬勃发展,人们对毫米波频段的研究逐步深入,传统的基于CMOS工艺的集成电路已满足不了当前的需求,基于GaAs工艺的集成电路已经发展成射频和微波领域电路设计的首选[1-4]。在无线系统中,分频器不仅作为频率合成器的反馈环的重要模块,同时也是锁相环电路中重要的模块,工作频率最高,也是功耗最大的的模块之一,其性能直接影响锁相环及无线系统的整体性能[5-7],因此对高性能的动态分频器进行研究具有重要的现实意义和实用价值。本文阐释了分频器的结构原理,研究并设计了基于GaAs HBT工艺的动态分频器,该动态分频器具有良好的性能,工作频率高,功耗低,满足设计要求,具有一定的使用意义。

1 动态分频器结构及其相关理论

1.1 动态分频器结构

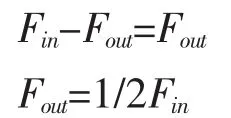

动态分频器又称为米勒分频器,结构如图1所示,是基于反馈系统的电路结构,包含低通滤波器和放大器。在混频器的两端分别连接输入信号和输出信号,输入信号和输出信号在混频器的内部进行混频,产生的谐波分量为Fin+Fout、Fin-Fout,谐波中Fin-Fout可以通过低通滤波[8-10],系统稳定之后,由以下公式计算

从而实现分频。

动态分频器的自身特点为可以工作在高频率下,但是工作的频率范围较小,因此需要采用适合动态分频器的器件工艺及电路结构,来增加动态分频器的工作范围,降低直流功耗,这是研究动态分频器的重点所在。

图1 动态分频器结构

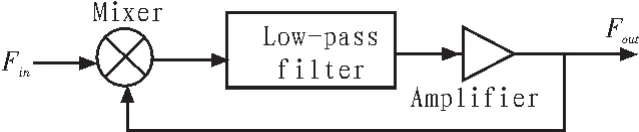

1.2 Gilbert混频单元

Gilbert混频单元是一种双平衡的电路设计[11],结构图如图2所示。采用这种结构设计具有很高的隔离度,混频器的输入信号都为平衡信号,直流偏置为零,输出信号通过差分电路,抵消了本振信号的泄露,这样可以增大本振的幅度。由于双平衡混频器采用Q3、Q4、Q5、Q6 4个晶体管组成双平衡电路结构,输出的电流信号同差分放大器RF端差分输入信号的电流差成正比,这样就能抵消跨导级电路转换电压信号时产生的偶数阶失真造成的影响[12-15]。 在Gilbert混频电路中,本振信号的幅值会影响跨导级电路Q1、Q2产生的噪声,并且跨导级电路的输入跨导会对混频器的线性度产生较大影响。

图2 Gilber混频单元

2 基于GaAsHBT工艺的动态分频器电路设计及仿真

2.1 动态分频器的电路设计

根据图1动态分频器结构图及图2 Gilbert混频单元结构图,对动态分频器进行电路的建模与分析,建模示意图如图 3所示。电路结构上包括 input buffer(输入缓冲电路)、Frequency Divider core(分频器核心电路)、output buffer(输出缓冲电路),电路建模示意图显示了模块电路的连接顺序。下面对各部分电路进行详细分析。

图3 动态分频器电路建模示意图

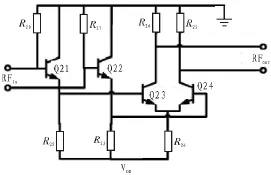

1)输入缓冲电路设计

输入缓冲电路的结构如图4所示。通过在信号源和电路之间添加电容来实现电路隔离,R1、R2主要是匹配输入阻抗,保证输入阻抗为50欧姆;单端转差分电路由晶体管Q1-Q4和电阻R3~R7组成,将输入缓冲电路的输入信号转换成核心分频电路所需的差分输入信号;放大器由Q3、Q4构成提高模块的驱动能力,Q5、Q6与电阻R8和R9组成了射级跟随器,用于实现电平的转换和信号的输出。

图4 输入缓冲电路结构

2)输出缓冲电路设计

文中设计的输出缓冲电路如图5所示,结构上包括射级跟随器和差分放大器,差分放大器带有50欧姆的电阻负载,匹配输出阻抗,射级跟随器主要满足电平的转换并为放大器提供驱动能力。整个结构同输入缓冲电路相似。

图5 输处缓冲电路结构

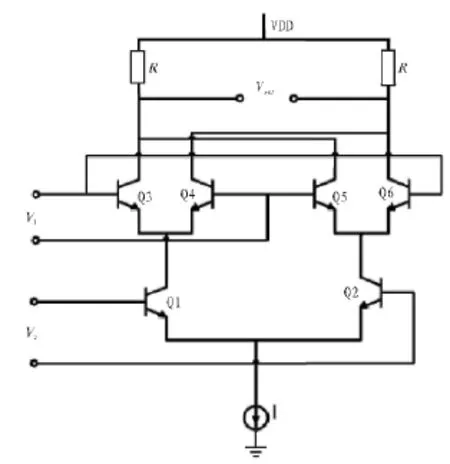

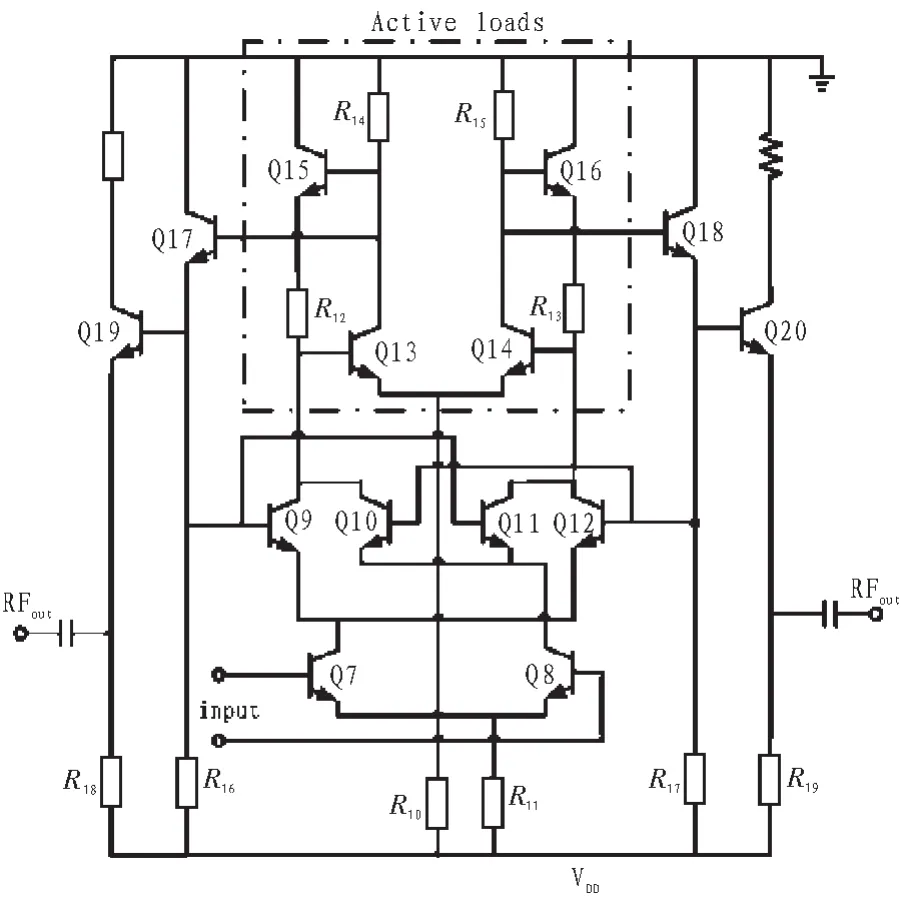

3)分频电路设计

分频电路为动态分频器的核心电路,本文依据动态分频器的原理和图2的Gilbert混频单元电路结构,设计分频电路如图6所示。从结构上划分分频电路可以划分为双平衡混频器、有源负载电路、反馈电路、射随输出电路。

图6 分频器核心电路结构

在双平衡混频器中,晶体管Q7-Q12组成双平衡混频电路。其中Q7、Q8跨导级电路,主要对输入的电压信号进行调制,输出电流信号。晶体管Q9-Q12组成开关级电路,包含两个=组开关差分对,由Q9与Q10、Q11与Q12组成。通过反馈的差分信号对经跨导级电路的电流信号进行控制和疏导,得到想要的频率分量,过滤掉谐波分量。

在有源负载电路中,Q13-Q16同R12~R15共同构成了有源负载电路。HBT为有源器件,当出现较小信号时,HBT会产生很高的阻抗,并且不需要直流偏置电压,这使得晶体管等效为阻值较大的电阻。通过采用有源负载可以提高混频器的转换增益,同时用可以降低功耗,扩大分频器的工作频率。

在反馈电路中由Q17、R16和Q18、R17两组射级跟随器组成,并将输出反馈到混频器的输入。为了得到更好的输入灵敏度和更好的输出功率,本次设计的分频器反馈采用反馈到开关机,同时还可以调整直流的电位。

射随输出电路由Q19、R18和Q20、R19组成,同时在电路后端添加电容用于输出隔离,过滤掉不需要的直流分量。

2.2 动态分频器的电路仿真

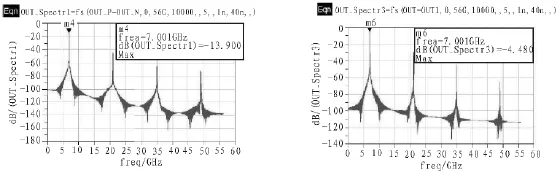

文中对动态分频器的仿真选择ADS软件平台进行,仿真主要是做瞬态仿真,此次仿真为对整体分频器进行瞬态仿真,并检测其工作的频率范围。首先,选择14 GHz,功率为0 dBm,输入阻抗为50欧姆的输入信号进行整体的瞬态仿真,仿真时间为100 ns,最大间隔为0.01 ns,电路的偏置电压为-6 V,得仿真效果如图7所示。

图7 频谱图

有图可得在输入频率为14 GHz时,可实现2分频,且输出的频谱很好,通过改变输入信号的功率和信号频率,最终确定了工作范围为9~15 GHz。将瞬态仿真器更换为直流仿真器,输入同样的信号可换算出总电流,并进一步计算出分频器的功耗为130.26 mW。

3 结 论

动态分频器可以在较高的频率下正常工作,本文通过选用GaAs HBT工艺,采用有源负载技术来设计动态分频电路,克服动态分频器工作范围窄的特点,并通过仿真测试,得出此次设计的动态分频器工作频率为9~15 GHz,满足设计要求,符合实际的应用。

[1]宋佳敏.毫米波上变频混频器芯片设计[D].成都:电子科技大学2015.

[2]鞠英,文光俊,杨拥军.应用于频率合成器的宽分频比CMOS可编程分频器设计[J].现代电子技术. 2011(4):131-135.

[3]张为,张旭,刘洋.2 GHz CMOS高速多模分频器的设计[J].华中科技大学学报:自然科学版.2011(5): 8-18.

[4]王菲菲,吴秀龙,徐太龙,等.一种超低功耗5.8 GHz双模前置分频器设计 [J].电子技术,2010(1): 27-36.

[5]葛洪利,徐太龙,孟坚,等.1.2V 6GHz 1.19mW 32/33前置分频器的设计[J].电子技术,2010(3):69-73.

[6]苏燕,冯军,施欢东.0.8V低功耗高速1∶2分频器[J].东南大学学报:自然科学版,2010(6):157-160.

[7]袁泉,杨海钢,董方源,等.锁相环型频率综合器中的高速分频器[J].中国科学院研究生院学报,2008(4):215-219.

[8]刘帮安.基于注入锁定的高频倍频器设计[D].合肥:中国科学技术大学,2014.

[9]宋佳敏.毫米波上变频混频器芯片设计[D].成都:电子科技大学,2015.

[10]陈楠.低功耗频率合成器的关键技术研究[D].合肥:中国科学技术大学,2013.

[11]刘颖.锁相环中鉴相器和环路滤波器的设计[D].西安:西安电子科技大学,2013.

[12]宋金凤.认知无线电频谱探测接收机中混频器的研究与设计[D].西安:西北大学,2010.

[13]程和远.超高速二分频器电路的设计及其γ辐射研究[D].西安:西安电子科技大学,2011.

[14]张旭.2/3双模宽锁定范围注入锁定分频器研究[D].天津:天津大学,2012.

[15]黄兆磊.频率综合器中分频器的研究与设计[D].上海:复旦大学,2011.

Research and design of dynamic frequency divider based on HBT GaAs technology

LIANG Fang-jian1,YAN Guang-tao1,LU Zhen2

(1.Shangqiu Electric Power Supply Company,Shangqiu 476000,China;2.Tianjin Universi,Tianjin 300072,China)

Aiming at the problems of static frequency divider frequency higher the greater the power.In this paper,the GaAs HBT process of high performance dynamic frequency divider is designed.Through the study on the dynamic frequency divider structure,with active load instead of traditional resistive load,improve the frequency divider work.Also on dynamic frequency divider for circuit design,and carries on the simulation,it is concluded that the frequency range with good flexibility of input 9~15GHz,power only for 130.26mW and meet the design requirements.

frequency divider;HBT GaAs;phase locked loop;DC power consumption

TN915

A

1674-6236(2017)09-0125-03

2016-06-19稿件编号:201606129

国家自然科学基金(51190103)

梁方建(1972—),男,河南商丘人,高级工程师。研究方向:电网设备应用故障诊断及检修。