基于FPGA和线阵CCD的麦粒检测系统研究

胡继云 赫刘勤 郑 维

基于FPGA和线阵CCD的麦粒检测系统研究

胡继云 赫刘勤 郑 维

(河南工业大学电气工程学院,郑州 450001)

为满足粮食安全性和麦粒等级划分的需求,本文提出了一种基于FPGA和线阵CCD的麦粒快速检测系统的设计方案。选用线阵CCD作为图像传感器采集麦粒图像信号,FPGA产生与控制整个系统时序,通过A/D对采集信号进行处理,并通过串口传输到上位机。结果表明,该设计能够实现对麦粒图像信息的采集、存储、处理及显示。本系统在麦粒图像数据的高速实时采集和处理上具有采集信号质量好、可靠性高、传输速率高等优点,并且具备良好的稳定性与抗噪性,在粮食监测中具有广泛的应用价值。

线阵CCD;麦粒;FPGA

我国是世界上最大的小麦生产国和消费国,粮食问题关系国计民生。麦粒中的杂质、霉变、病 变[1-2]以及虫害等都会严重影响麦粒品质,麦粒品质的优劣在小麦育种、栽培、深加工和粮食存储等方面存在安全隐患,严重影响着我国粮食和食品安全。在麦粒检测中,人工检测易受主观因素影响、大批量分拣困难逐渐被淘汰,而图像检测法[3]成为近几年来麦粒检测与识别领域的研究热点。因此,本设计着眼于麦粒图像检测法的基础研究,寻找出一种效率和准确率高的麦粒检测方法,提高小麦及其制品的质量安全性。

目前,光电检测技术已经在粮食行业进行推广应用,核心控制器大多采用FPGA(现场可编程逻辑阵列)、单片机、DSP(数字信号处理器)等多种嵌入式芯片[4]。权衡各种控制器应用在本系统中的利弊,FPGA作为麦粒分拣系统的核心控制器,控制CCD数据采集芯片、ADC(数模转换器)以及数据存储器等各大模块,具有高速、可靠性高、开发周期短以及具有完善的开发工具等优势。市面上现有的色选机系统主要采集麦粒的反射光信号,本系统则采集麦粒透射光信号进行检测,有效提高了检测精度。

1 系统方案及原理

1.1 系统设计原理

麦粒检测系统是利用光电检测技术,对溜槽中麦粒进行动态扫描、提取并处理数据,来实现麦粒快速检测。检测系统首先将麦粒送到溜槽依次下落,进入CCD传感器的感应区,光学系统感应到成像区麦粒透射光光强变化并进行动态扫描。利用线阵CCD传感器将变化的光强信号转换成相应强度的模拟信号并输出到A/D转换器,经A/D转换后输出的数字信号送回主控单元FPGA进行数据处理,设定合适的灰度阀值,将最终的判决信号送到串口显示。

为保证光源模块的强光输出、光照均匀性和稳定性,同时避免因光源的照射频率要小于CCD扫描的频率,使麦粒表面的图像亮度(,)在CCD曝光时间内积分值变动很大,而采集到明暗相间的条纹图像[5],故选用半导体发光二极管组成的点阵背光光源进行照射。光路结构如图1所示,已知正常麦粒长轴约为6.5mm,短轴约为3.5mm,为保证CCD检测麦粒动态时形态一致性,设计直径为5mm的弧形滑槽,并在滑槽底部开启一个直径为1mm的圆形检测视窗,经过光路中多个反射镜使得CCD接收到所需像元个数。

图1 光路结构图

1.2 麦粒检测系统的设计方案

本系统设计为麦粒在溜槽中速度稳定在1.5m/s左右时进行CCD数据采集,每个麦粒采样16次,则CCD采样一次所需时间应小于0.27ms,即CCD工作频率达到10MHz以上才能满足设计需求。TOSHIBA公司的TCD1209D共有2088个像元,最大工作频率为20MHz[6],它的高速、低功耗、高灵敏度的响应特点,能够满足麦粒在溜槽中的速度变化、系统检测精度及稳定性需求。

FPGA主要实现产生CCD和ADC(模数转换)所需的时钟信号、采集数据存储、对模数转换得到的数据进行处理并通过串口发送到上位机,如图2所示。ALTERA公司的第一代产品EP4CE10E22C8N作为中央处理器满足快速、稳定的设计需求,它拥有10320个逻辑单元,645个可配置逻辑模块,片上RAM共计414KBits,最大运行频率402MHz,板上提供了大容量的SDRAM和FlashROM等存储单元。FPGA内部丰富的乘法器结构和锁相环(PLL)模块,能精确实现系统所需要的时钟频率。

图2 系统整体结构框图

2 硬件设计

2.1 电源电路设计

电源模块设计将15V直流电源滤波处理后经过稳压器件得到所需电压。如图3(a)所示,系统采用两片AOZ1284PI(可调范围为0.8~30V)通过选择电阻9、11和2、6的阻值分别实现15V到12V和15V到5V的电压转换,用来提供CCD供电电压和工作电压。降压转换器TLV62565通过选择17为10kW得到3.3V稳定电压。

为了满足FPGA2.5V工作电压的需求,系统选用低压差线性稳压器SPX3819输出1.5V和2.5V两个固定电压,避免传统的线性稳压器(LDO)重输出电压要比输入电压低的弊端。如图3(b)所示,由3.3V电压经两片稳压器SPX3819得到FPGA所需电压1.5V和2.5V。在电源电路中15V输入电压经过稳压器AOZ1284PI、TLV62565和SPX3819转化后,得到稳定直流电压12V、5V、3.3V、2.5V和1.2V,为FPGA、CCD1209D、AD9945等模块芯片提供电源。

(a)12V电源电路

(b)2.5V电源电路

图3 电源电路图

2.2 CCD驱动电路设计

TCD1209D典型供电电压12V,典型工作电压为5V。如图4所示,FPGA提供六路驱动脉冲,由于FPGA的常规I/O口3.3V电压与TCD1209D工作电压5V不匹配,若直接使用FPGA输出信号引脚无法直接驱动线阵CCD,因此本系统使用SN74LVCC3245型逻辑芯片提高FPGA输出信号的驱动能力和负载能力。

SN74LVCC3245高达40MHz的频率可以满足CCD驱动频率10MHz需求。它的两个独立供电电源轨中,其中被用来跟踪VCCB电压的B口可以直接接受的电压范围为3~5.5V;用来跟踪VCCA电压的A口可以直接接受的电压范围为1.65V到3.6V。这种结构能实现由供电电压为3.3V的FPGA的系统环境转换到供电电压为5V的CCD的工作环境,从而驱动TCD1209D进行工作。

图4 CCD驱动电路

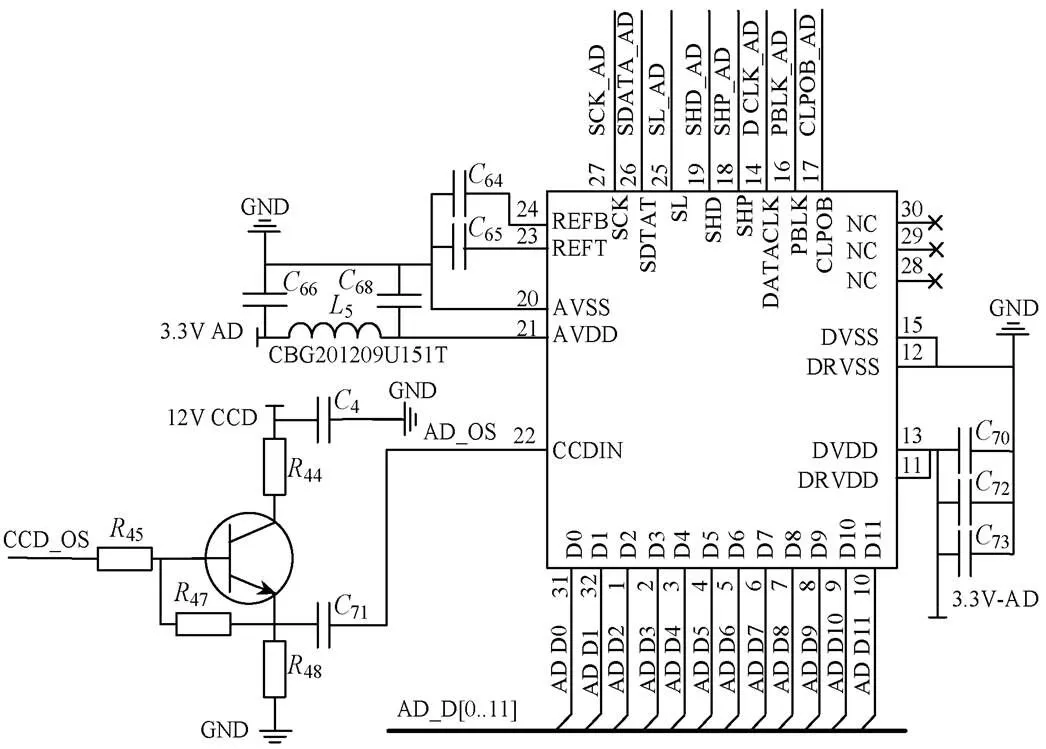

2.3 A/D转换电路设计

线阵CCD采集的麦粒图像信号需要进行A/D转换才能进行数据分析处理。1209D输出信号OS包含饱和输出电的压值约为5V麦粒图像信息的信号电压和5.5V左右的直流分量。AD9945之所以能以高达40MHz的速度对CCD输出信号进行12bit精确采样是因为它的较强的兼容性,且对输入信号要求很低。如图5所示,CCD输出信号OS经放大后通过外接一支0.1PF隔直电容滤除直流分量即可送至AD9945的信号输入端进行后续处理,其中放大电路用来增强CCD输出信号的强度和带负载 能力。

TCD1209D输出的模拟信号通过输入端CCDIN进入AD9945,经过相关双采样(correlated double sampler, CDS)、模数转换(12bitADC)等步骤处理后输出麦粒图像信息的数字信号。滤出直流分量后的有用信号电压值约为1.5V,通过电压调整之后,CCD信号进入CDS过程进行信号采样。相关双采样输出两次采样的差值,有效抑制低频噪声,得到更好的信号,相较于单次采样,信号更精确。

图5 A/D转换电路

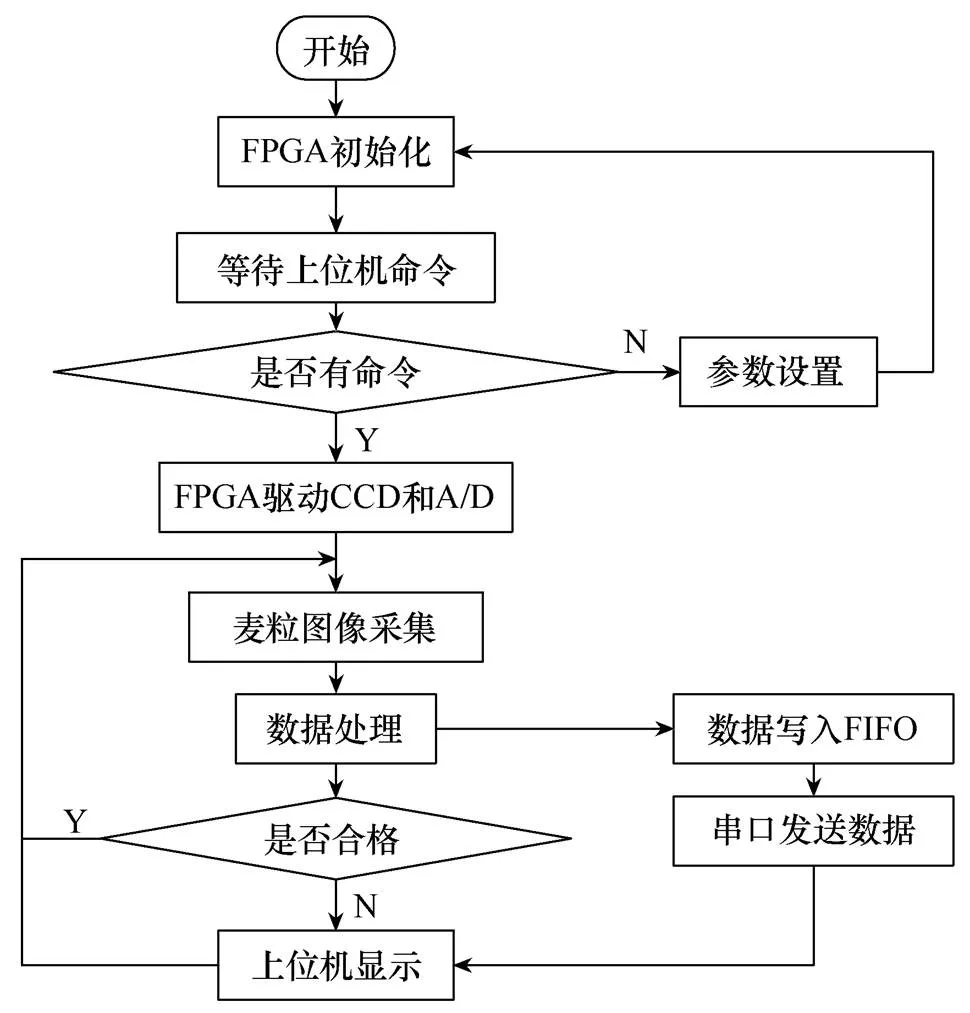

3 软件设计

系统上电后,首先进行FPGA初始化、异步FIFO复位,然后等待命令。当串口接收到读取数据的命令后,FPGA开始驱动CCD和AD进行工作,ADC陆续将转换后的12位数据传送到输出口。FPGA对采集到的麦粒图像数据进行处理后,一方面把判断结果显示在上位机,另一方面把处理后的数据存入FIFO存储器。FIFO中存储的数据由并转串模块读取出来通过串口发送到上位机并显示,这样就完成了一次麦粒检测过程,如图6所示。

图6 软件系统流程图

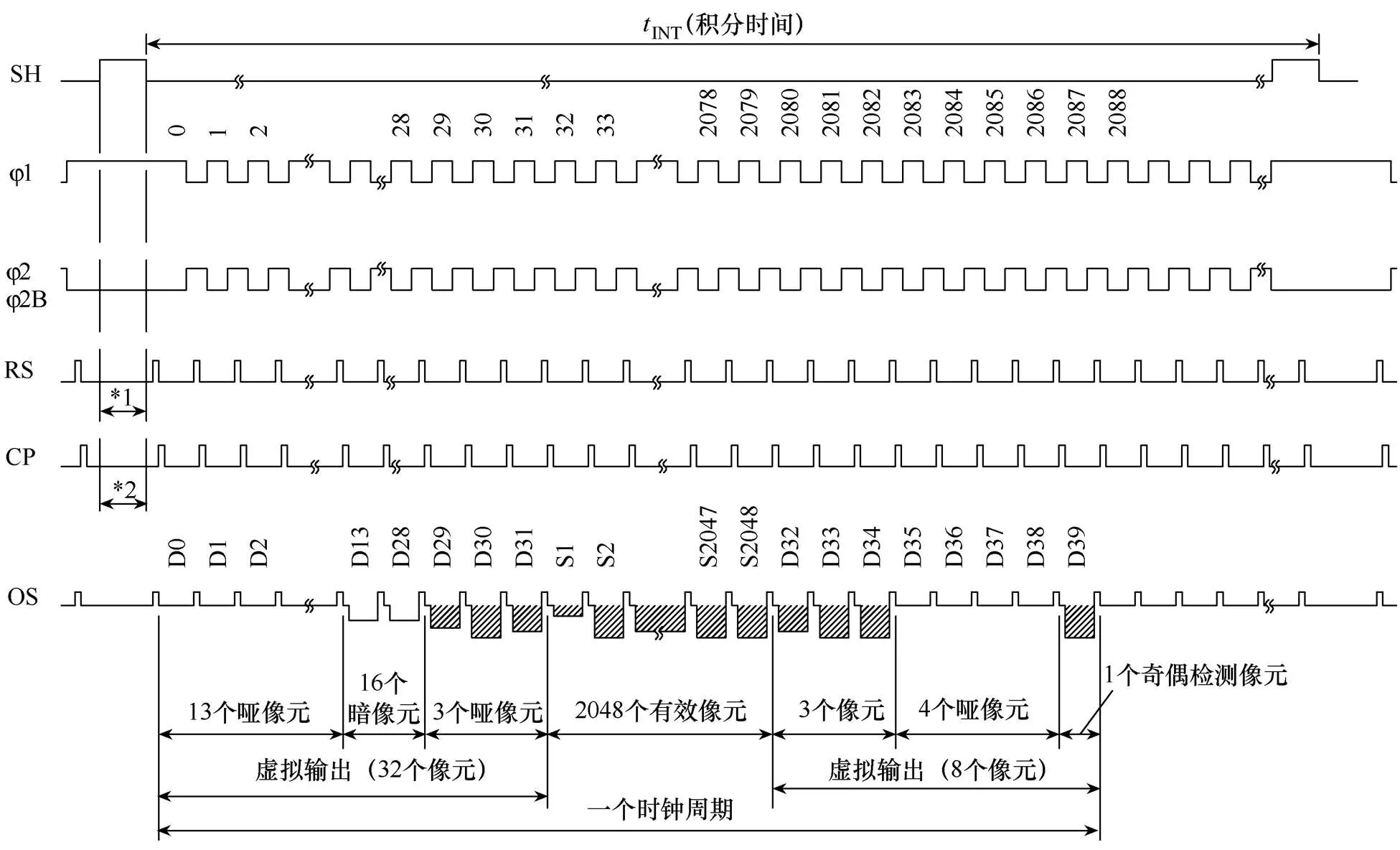

3.1 线阵CCD驱动时序设计

由时序图7可知,TCD1209D需要两个相位相反的时钟脉冲j1和j2、转移脉冲SH、复位脉冲RS和钳位脉冲CP六路驱动信号[8]。CCD工作需要频率为10MHz,则j1和j2为10MHz,RS和CP与其一致。CCD1209D的工作周期包括光积分阶段和电荷转移阶段。在当前像元信号输出后到下一个像元信号到来之前,RS和CP两个脉冲清除像元中的残余信号,减小相邻像元之间的相关信号[7]。

图7 线阵CCD1209D时序图

本设计的外部晶振为20MHz,使用FPGA内部自带的PLL倍频到40MHz频率,再分频计数得到10MHz的时钟。设置时钟脉冲j1、j2的占空比为1∶1;设置钳位脉冲CP和复位脉冲RS占空比为1∶4,脉冲宽度为20ns;转移脉冲宽度为1500ns,j1与SH为高电平之间空闲脉宽,选择脉宽为500ns,CP脉冲高电平比RS脉冲高电平延时输出。根据以上分析,通过设置计数器对外部晶振倍频、分频的方式实现各驱动脉冲波形[9-10],通过编译仿真之后所得波形图如图8所示。

图8 CCD1209D驱动时序仿真波形图

3.2 AD9945驱动时序设计

上电后,AD9945芯片自动执行内部校准程序以及初始化内部寄存器。在此期间,串行数字接口写的任何数据都不被接收。初始化之后由数据线SDATA、时钟线SCK、从器件使能信号线SL三线串行数字接口对AD9945芯片内寄存器进行配置以确定相应功能的参数大小。如图时序图9所示,SCK上升沿时,写入SDATA的数据,SL处在低电平,随后更新寄存器中的值,时钟信号频率设为10MHz,可以利用CCD脉冲设计中的时钟分频模块,设置占空比为1∶1。规定了AD的工作方式后,CCD工作频率为10MHz,采样时钟SHP、SHD和DATACLK的信号频率也设为10MHz,SHP和SHD占空比为3∶1,DATACLK占空比为1∶1。调试时可通过修改具体参数,同时观察示波器中CCD输出信号,以保证锁存时钟DATACLK必须与TCD1209D像素输出严格同步。设计ID=12ns,S1=1/4,S2=1/2。CLPOB和PBLK主要用于消除CCD输出信号中无效像元的影响,CLPOB的脉冲宽度应与TCD1209D中暗电平输出区域一致,即为D13—D28信号输出,以保证输出真正的有效数据。由于CCD输出信号中无空白像素,控制AD9945数字输出的(DOUT)PBLK一直置高即可。

图9 AD9945时序图

本设计通过FPGA内部的PLL将系统20MHz倍频、分频得到10MHz,采用两位计数器对输出时钟取反,为AD9945提供驱动脉冲。串行写操作的时钟设置与SCK一致,均为10MHz,故SCK直接被赋值为该时钟。SL高电平复位,分别在第4个和56个时钟上升沿赋值为0和1,即SL有52个时钟脉冲处于低电平,在此期间配置4个寄存器,寄存器的值由SDATA设置,初始值设为{4'h0,12'h0,12'h0,12'h040,12'h0}。仿真结果如图10所示。

图10 AD9945时序仿真波形图

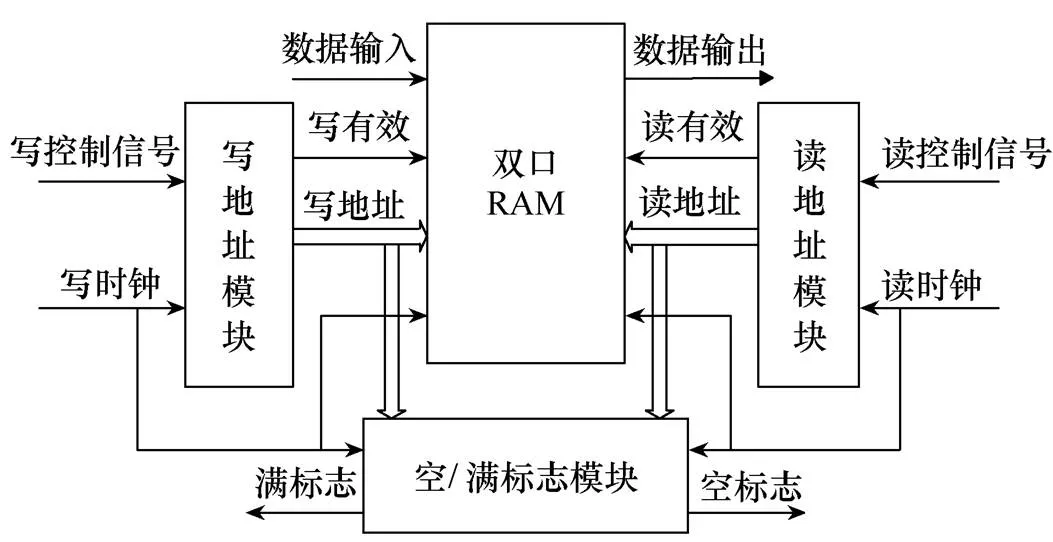

3.3 建立存储器FIFO

本系统数据缓冲器设置为先进先出型(First In First Out)存储器FIFO。为保持FIFO宽度与AD9945的并行数据输出位数一致,系统在FPGA设置一个12×2048bit的异步FIFO。程序设置FIFO的深度设为2K,以满足可以缓存TCD1209的整帧的数据,保证FPGA中FIFO留有部分裕量。由于CCD工作频率为10MHz,所以设置写时钟频率与CCD工作频率一致。设置串口传输速率9600bit/s,读出的数据通过串口传输到上位机,则FIFO读时钟频率为 9600/12Hz,进而设置写时钟频率与读时钟频率一致,故本系统采用的是异步FIFO存储器[8]。系统FIFO的结构示意图如图11所示,FIFO分为读时钟域和写时钟域,读操作和写操作可以同时进行,通过双口RAM[11]进行数据存储。FIFO内部的逻辑电路分配读、写地址,而FIFO若能正常工作还需要外部电路给出读、写控制信号。

图11 异步FIFO结构示意图

3.4 并行数据转串行数据的设计

从FIFO读取出来的12位并行数据,需要串口传输至上位机,故需要并转串模块设置才能传输数据到上位机中。系统设置串口传输速率为9600bit/s(即为9.6MHz),从FIFO读取数据频率为0.8MHz,如此便把串口传输速率设置为并行传输数据频率的12倍。数据移位寄存器放置从FIFO中读取的并行数据,而移位控制寄存器控制并行数据进行移位操作[12]。

4 实验结果分析

根据以上研究,搭建基于FPGA和线阵CCD的麦粒分拣系统硬件实验平台,分别将优质麦粒样本和劣质麦粒样本进行实验,并在示波器上观察CCD采集的麦粒图像信息,结果如图12所示,优质麦粒和劣质麦粒有明显差别。

(a)劣质麦粒 (b)优质麦粒

采集数据对比结果显示优质麦粒和劣质麦粒采集处理后的数据有明显区分:正常麦粒采集到的数据均在35000以上,而不良麦粒的采集数据的结果显示在35000以下,设置有效阀值进行判断,结果见表1。

表1 实验结果分析

实验实测数据表明,该系统能够稳定地识别、判断劣质麦粒和优质麦粒,并显示判断结果,为快速筛选优质小麦奠定了基础。

5 结论

本文基于高速线阵CCD对麦粒进行非接触式检测、采用FPGA实现高速图像实时处理。图像处理系统经算法分析后,输出检测判定方案,实现麦粒优劣品质的检测。该硬件平台设计已在实际的麦粒检测中得到验证,能够实现了病变麦粒的快速、稳定、高精度检测。文中建立的线阵CCD快速检测系统的硬件实时图像处理平台为后期麦粒分拣处理提供可靠的样本数据,同时也能拓展应用于其他粮食行业的品质检测、检测过程中。

[1] 崔贵金. 赤霉病麦粒光电检测技术研究[D]. 郑州: 河南工业大学, 2013.

[2] GB 1351—2008. 小麦[S] .

[3] 郭敏, 秦昕, 马苗. 基于图像处理的谷物检测与识别方法研究进展[J]. 中国粮油学报, 2012, 27(4): 123-128.

[4] 刘玉. CCD数据采集系统的FPGA实现[D]. 合肥: 安徽大学, 2014.

[5] 张洪涛. 钢板表面缺陷在线视觉检测系统关键技术研究[D]. 天津: 天津大学, 2008.

[6] T0SHIBA CCD LINERA IMAGE SENSOR CCD. Charge coupled device[Z]. 2001.

[7] 高尚. 基于FPGA的线阵CCD图像测量系统研究[D]. 合肥: 安徽大学, 2011.

[8] 夏真珍. 基于FPGA的线阵CCD光强分布测量系统研究[D]. 重庆: 重庆大学, 2014.

[9] Xu Tiexi, Xiong Xianming, Li Mingjin. Design of FPGA based on Linear Array CCD Driver Circuit[C]// ICEMI'2009, 2009: 276-768.

[10] 张林, 胡学友, 李秀娟, 等. 基于CPLD的线阵CCD驱动时序发生器的设计[J]. 电测与仪表, 2006, 43(8): 23-27.

[11] Yu Guangping, Xie Yangen. Research of automobile speed measuring system based on linear CCD[C]// IITA International Conference on Control, Automation and Systems Engineering. 2009: 148-151.

[12] 刘敏, 陈金鹰, 唐伟, 等. 基于FPGA的并行数据转SPI接口设计[J]. 电视技术, 2012, 36(5): 31-32, 60.

Grain Detection System of based FPGA and Linear CCD

Hu Jiyun He Liuqin Zheng Wei

(School of Electrical Engineering, He’nan University of Technology, Zhengzhou 450001)

To meet the food safety and grain grading requirements, this paper presents a field program able gate array (FPGA) and linear CCD grain rapid detection system design. Selection of linear CCD as the image sensor to collect grain image signal, FPGA timing generation and control the entire system, the A/D signal acquisition processing, and transmission via the serial port to the PC. The results show that the design can achieve grain image information collection, storage, processing and display. The system has a good quality signal acquisition, high reliability, transmission speed advantages, and have good stability and noise immunity, has a wide range of food monitoring applications in high-speed real-time acquisition and processing of grain image data.

linear CCD; grains; FPGA

国家公益性行业(粮食)专项(201313005-04)