嵌入式系统设计实验的Qt MIPS仿真软件开发

姚英彪, 曾宪彬

(杭州电子科技大学 通信工程学院,杭州 310018)

嵌入式系统设计实验的Qt MIPS仿真软件开发

姚英彪, 曾宪彬

(杭州电子科技大学 通信工程学院,杭州 310018)

针对嵌入式系统设计的实验教学,采用Qt C++应用程序开发框架,开发了一款嵌入式软硬件仿真平台软件Qt MIPS。Qt MIPS主要特点如下:集汇编代码编辑、汇编、仿真和调试于一体,并具有友好的人机交互界面;支持周期准确的MIPS32指令仿真和分层存储系统的参数化配置;提供多种性能统计工具,对学生开放仿真器源码。Qt MIPS使用实践表明,它能够加深学生对嵌入式系统设计相关理论知识的理解,能够培养学生的嵌入式系统编程能力和系统性能分析能力,有效提升嵌入式系统设计的实验教学效果。

嵌入式系统; 仿真软件; 实验

0 引 言

近几年来,随着嵌入式系统在各行各业的应用,嵌入式系统设计已经成为高等院校电子信息类专业的一门重要基础课程。在其理论和实践教学过程中,如何让学生更直观的理解嵌入式系统组成和嵌入式处理器指令集,以及部件级(如CPU、内存)和系统级的性能评价与优化方法,一直是一个难点问题[1-2]。利用仿真技术,可以在没有硬件实验平台的条件下(如各种开发板),通过软件抽象建模嵌入式硬件系统的“软”平台,然后模拟指令序列在目标处理器上的执行[3-5]。这种方法因为可以更好的观察指令执行过程,分析系统的部件和整体的性能,因此在嵌入式系统设计实践教学过程中被广泛采用。

目前,常见的嵌入式仿真软件有ARM ADS1.2[6]、MIPS SPIM[7]、CCS[8]等。这些仿真软件都是CPU厂家提供的商业软件,主要面向嵌入式系统开发,存在源码不开放、参数固定等诸多缺点,不适合应用于嵌入式系统设计课程的实践教学。SimpleScalar[9]作为一款开源的仿真软件,支持多种类型的处理器,但它没有提供图形用户界面,需要在Linux系统中利用命令行进行相关参数配置,操作极其麻烦,因而也不适合嵌入式系统设计课程的实验教学。MARS[10]虽然是面向教学开发的仿真软件,但同样存在源码不开放,功能少等缺点。因此,专门面向嵌入式系统设计实验教学的仿真软件还是比较缺乏。

针对上述问题,本文设计了一款面向嵌入式系统设计课程实践教学的仿真软件Qt MIPS。Qt MIPS采用Qt C++应用程序开发框架开发,可以跨平台运行[11];面向MIPS指令集[12-13],可以实现MIPS32指令集的周期准确仿真;支持参数化的存储系统配置,可以进行存储系统设计探索[14];支持处理器内部寄存器、存储器的实时查看和修改,以及各种性能统计;为基于MIPS的嵌入式系统设计实验提供了一个集汇编程序编辑、汇编、配置、调试、运行于一体的集成实验环境。

1 整体结构

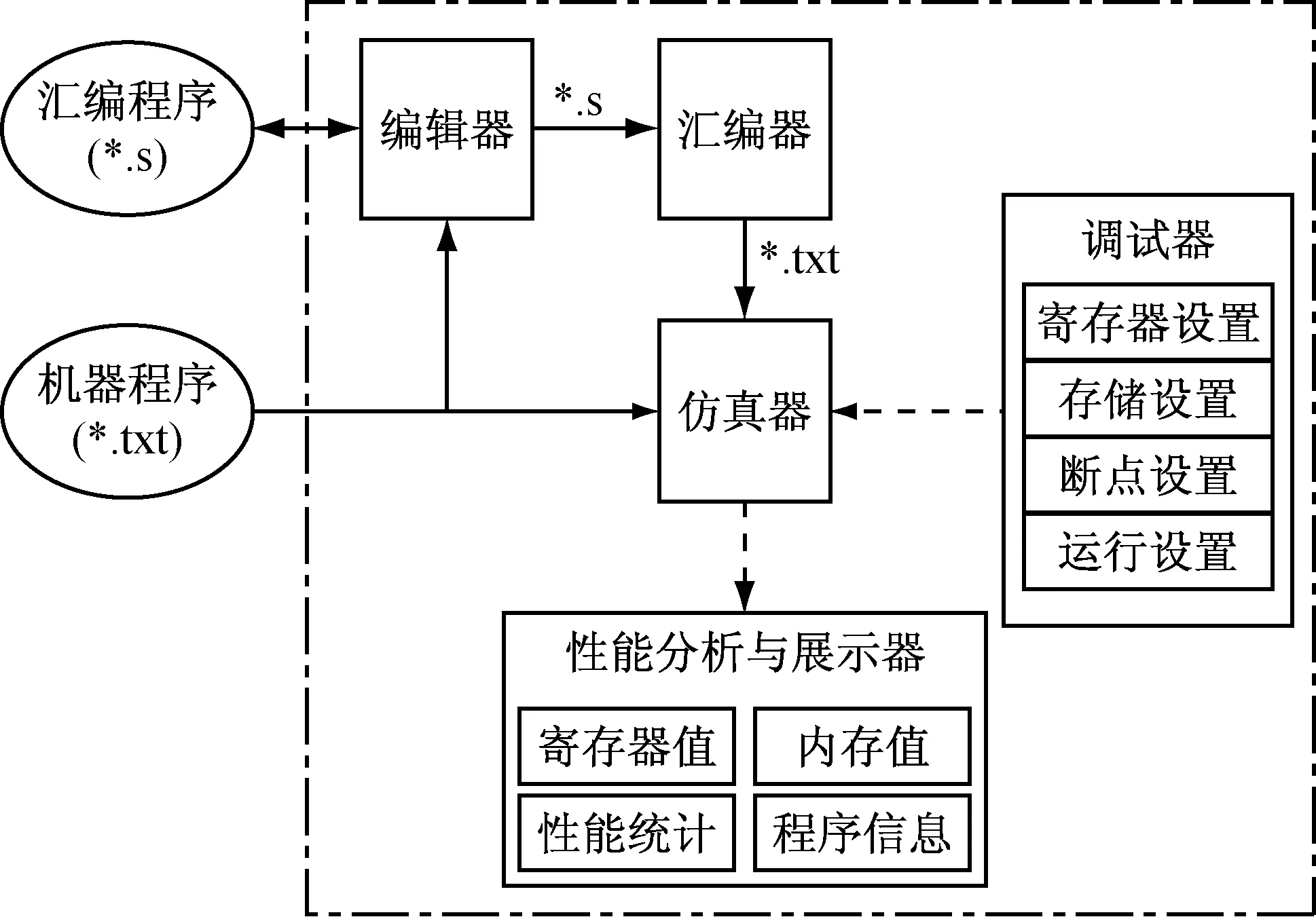

Qt MIPS采用模块化的设计方法和C++语言开发完成。它可以分为5个模块,分别为编辑器(Editor)、汇编器(Assembler)、仿真器(Simulator)、调试器(Debugger)、性能分析与展示器(Profiler),如图1所示。图中实线表示仿真流程,虚线表示控制流程。

图1 Qt MIPS总体结构

Qt MIPS核心是仿真器,它由CPU流水线、片上内存和片外内存三部分组成,如图2所示。CPU流水线采用经典5级流水线建模[12-13],分为取指(IF)、译码(ID)、执行(EXE)、访存(MEM)和回写(WB)。片上内存采用Scratch-Pad RAM(SPM)和高速缓存(Cache)建模[14]。

图2 Qt MIPS的仿真器总体结构

Qt MIPS作为一款集编辑器、汇编器、仿真器、调试器于一体的面向“嵌入式系统设计”课程实验教学的仿真平台软件,其基本功能包括:

(1) 编辑功能。Editor实现指令高亮显示,字符查找等功能,方便进行汇编代码编辑。

(2) 汇编功能。Editor里的汇编代码,可以通过Assembler进行汇编,然后仿真执行。

(3) 仿真功能。Simulator支持周期准确的MIPS32指令集仿真,并且支持仿真时单步/多步执行时指令跳转高亮动态跟踪功能。

(4) 调试功能。Debugger支持快捷的仿真执行控制功能,如断点,执行次数,多步执行的步数设置,寄存器与内存内容查看等。

此外,为方便“嵌入式系统设计”课程实验教学,还具有如下特色功能:

(1) 跨平台特性。采用Qt编程实现,可以运行于Windows、Linux等多种操作系统下,实现了仿真软件的跨平台性。

(2) 参数化设计。CPU的时钟、片上/片外内存的大小、性能,以及Cache的组织方式都是参数化设计。在实验过程中,通过设置这些参数,就能改变嵌入式系统的性能,这样学生更容易理解嵌入式系统性能的影响因素。

(3) 详尽的性能统计工具。仿真器在仿真时,实时统计程序执行时钟周期数,片上内存命中次数,片外内存访问次数等各种统计数据,便于学生深入理解嵌入式系统的部件级和系统级的性能评价。

(4) Simulator源码开放。对嵌入式系统设计特别感兴趣的同学,可以查看Simulator源码,深入理解嵌入式系统组成、软件执行过程、现代CPU的原理等内容,甚至在提供的Simulator源码基础上还可以进行二次开发。

2 模块功能

2.1 编辑器

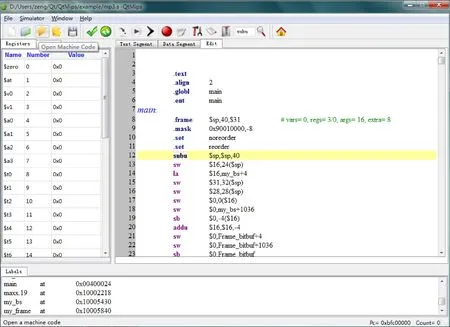

Editor实现汇编程序新建、打开、保存、编辑等功能。Qt MIPS支持的汇编程序为*.s结尾的文本文件,打开效果如图3所示。可以看到,Editor支持不同类型关键字用不同颜色表示,所在行代码高亮显示。此外,Editor也可以打开机器码文件(工具栏第3个按钮)。最后,Editor也实现了常用的文本编辑器所具有的字符查找、剪切、复杂等功能,方便学生编辑和调试MIPS汇编代码。

图3 Editor打开*.s汇编文件

2.2 调试器

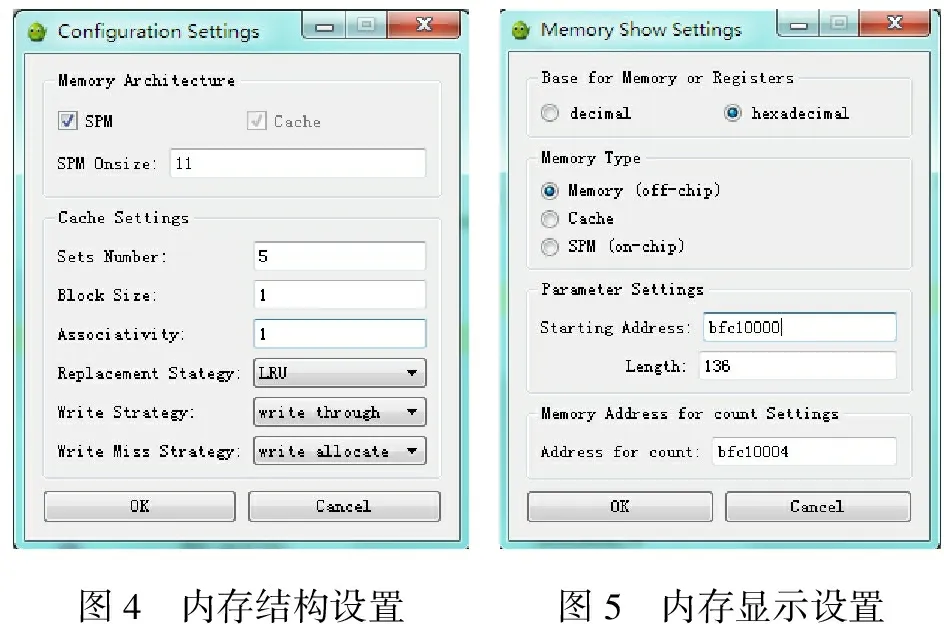

调试器主要实现寄存器设置、存储设置、断点设置、运行设置(单步、多步、执行次数等)等。其中,存储设置是Qt MIPS的一个亮点,它包括内存结构设置和内存显示控制设置,分别如图4和图5所示。从图4中可以看到,Qt MIPS可以实现SPM添加及其大小配置,Cache的大小及组织方式设置,具体包括Cache的组数、块大小、相联映射方式、替换策略、写策略、写缺失策略等。由图5可见,Qt MIPS内存显示设置包括显示数据类型、内存类型、起始地址及长度设置、访问次数统计地址设置等。

图4 内存结构设置图5 内存显示设置

2.3 性能分析与展示器

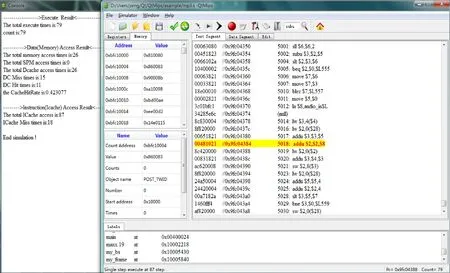

在指令仿真运行期间,Qt MIPS重载汇编代码的机器码,在Profiler展示,如图6所示。Text Segment窗口实现了单步/多步执行时指令跳转高亮动态跟踪,最左边的是机器码,中间是指令的存储地址,右边是对应的汇编代码。Console窗口实时显示程序指令执行条数t1,数据内存总访问次数t2,SPM的访问次数t3,以及数据Cache的访问次数t4,命中次数t5,以及指令Cache的访问次数t6,命中次数t7等实时仿真统计结果。Registers和Memory窗口实时显示寄存器或内存的值。Labels窗口显示汇编代码中的标号情况(数据对象和函数对象的首地址)。

根据图6Console窗口输出的性能统计结果,可粗略评价嵌入式系统的处理性能,即程序执行时间T可以近似为:

T=[t1+t3(Nspm-1) +(t5+t7)(Nhit-1)+ (t4+t6-t5-t7)Nmiss]·CCT

式中:CCT是处理器的时钟周期(假设指令都为单周期指令);Nspm是SPM访问时钟周期;Nhit是Cache访问命中时的时钟周期;Nmiss是Cache访问缺失时访问外存的时钟周期。

3 汇编器与仿真器设计

3.1 汇编器

Qt MIPS的汇编器是利用Flex和Bison这两个开源工具实现[15]。Flex是一款词法分析器生成工具,利用Flex可以快速地生成词法分析器,识别文本中的词素。Bison则是一款语法分析器生成工具,可以根据用户设定好的语法,快速生成相应的语法识别程序。因为它们生成的汇编器是串行汇编,分支、跳转、子程序调用及存取指令若在符号地址定义之前出现的话,就会出现汇编错误。

图6 Profiler结构

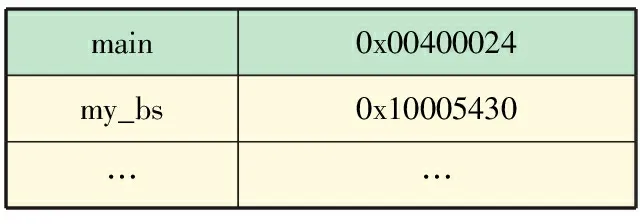

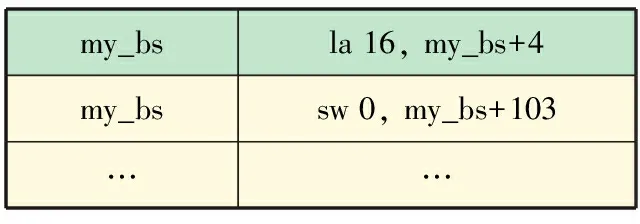

图3中Edit窗口第14行“la$16, my_bs+4”与第18行“sw 0, my_bs+1036”这两条汇编指令,由于my_bs符号在18行之前未定义,在没有进行任何处理的情况下,汇编器会串行汇编将my_bs的值设定为0,然而在图3 Labels窗口中可见,my_bs的地址是0x10005430,所以汇编器会发生串行汇编错误。为解决这个问题,本文提出了SR(保存恢复)算法,它用到两种映射容器类Map和Multimap。Map容器是一对一映射容器,Multimap是一对多映射容器,如图7所示。其中,infoLine是一个用户定义的结构体,用来保存含符号的指令行信息。

main0x00400024my_bs0x10005430……

Map

Multimap

图7 Map与Multimap容器类

SR算法是根据符号label出现位置分别处理。①label出现在定义处:此时先将label保存到Map中,然后判断label是否出现在Multimap中;如果出现,说明在label定义之前已经有指令用到该label,需要恢复Multimap中的使用该label的指令;如果没出现,不需要做任何处理。②label出现在指令中:此时需要判断label是否出现在Map中,如果出现,说明label已经在之前定义好,可以直接使用Map中该label的值汇编该指令;否则,说明label还未定义,需要将该label保存到Multimap容器,等到该label定义后再恢复。

3.2 仿真器

3.2.1 CPU流水线仿真

Qt MIPS的仿真器采用经典的5级流水线,分别为IF、ID、EXE、MEM和WB,每级流水线的功能为:

IF——访问指令内存,得到32 bit的指令。

ID——对指令进行译码,根据译码结果读取CPU寄存器的内容。

EXE——完成指令执行。

MEM——Load/Store指令完成数据内存访问。

WB——指令执行结果保存到寄存器文件中。

为便于学生理解CPU硬件结构,这5级流水线分别编写相应函数。在程序实现时,碰到的一个难点问题是MIPS体系结构的延迟槽指令的程序流程控制,它反映在IF和EXE流水级。为此,在Qt MIPS的仿真器设计中,使用了两个指针PC和Delay_PC,以及一个分支跳转指令状态标志BJ_Flag来实现指令执行顺序的控制。程序执行流程控制的伪代码为:

(1) IF阶段的流水线控制

1. if (BJ_Flag=0)

2. Access(PC); Delay_PC=PC+4;

3. else if (BJ_Flag==1)

4. Access(Delay_PC); Delay_PC=PC; BJ_Flag=2;

5. else

6. Access(Delay_PC); PC=Delay_PC; Delay_PC=PC+4; BJ_Flag=0;

IF阶段:①BJ_Flag=0,代表EXE级的指令不是跳转指令,下一条指令地址在PC处,因而通过Access(PC)取指,并设置延迟槽指令地址Delay_PC为PC+4。②BJ_Flag=1,代表EXE级的指令是跳转指令,下一条指令需要取延迟槽里面的指令,即在Delay_PC处,因而通过Access(Delay_PC)到延迟槽中取指,然后设置Delay_PC为上一条跳转指令真正的目标地址PC,最后设置BJ_Flag=2进入跳转状态。③BJ_Flag=2,代表需要执行跳转指令真正目标地址处的指令,因而通Access(Delay_PC)取指,最后将PC、Delay_PC和BJ_Flag恢复为正常指令执行状态。

(2) EXE阶段的流水线控制

1. if跳转指令

2. BJ_Flag=1;

3. if跳转成功

4. PC=目标地址;

5. else

6. PC+=8;

7. else

8. BJ_Flag=0; PC+=4;

EXE阶段:需要对指令类型进行判断,①如果该指令不是跳转指令,设置BJ_Flag=0,PC=PC+4,表示流水线处于正常状态;②如果该指令是跳转指令,设置BJ_Flag=1,表示流水线即将进入延迟状态;然后判断跳转指令跳转是否成功,如果成功,设置PC为新的目标地址,否则设置PC=PC+8(由于存在延长槽)。

3.2.2 存储系统仿真

Qt MIPS的存储系统支持片上SPM大小,Cache块数、块大小、地址映射策略、替换策略、写策略等的参数化配置。其中,Cache地址映射策略包括直接映射、组相联映射策略;替换策略包括最近最少使用(LRU)策略和先入先出(FIFO)策略;写策略包括写透(Write Through)和写回(Write Back)策略[16]。Qt MIPS存储系统建模的难点在于Cache的建模,其模型如图8所示。图中,FIFO/LRU替换策略的主要差别在于:

(1) 在访问Cache命中时,采用FIFO策略,不需要更新FIFO队列顺序;采用LRU策略,需要将命中项调整到LRU队列的最近访问位置。这一点体现在图9中的第4和第6请求,此时FIFO队列顺序不变,而LRU队列顺序发生变化。

(2) 在Cache未命中需要选择剔除项时,虽然形式上都是选择队尾的项进行剔除,但是物理意义不一样。FIFO队尾项代表该项是最先进入队列,而LRU队尾项代表该项是最近最少使用。这一点体现在图9中的第5请求,此时FIFO策略选择剔除“0”,LRU策略选择剔除“1”。

由于这两点的不同,故FIFO/LRU替换策略的性能不一样。例如,在图9示例中,当处理第4请求“0”时,队列顺序已经不一样;当处理第5请求“3”时,队列内容已经不一样;当处理第7请求“0”时,命中情况已经不一样,即性能不一样。

图8 Qt MIPS的Cache读写模型

图9 FIFO/LRU替换策略举例(假设Cache的容量为3,初始为空)

4 结 语

针对嵌入式系统设计的实验教学,采用Qt跨平台C++应用程序开发框架,开发了一款支持MIPS32指令集的嵌入式软硬件仿真软件Qt MIPS。它集MIPS32汇编代码编辑、汇编、仿真和调试于一体,并且其仿真器的源码开放。学生在学习嵌入式系统设计相关理论知识的同时,通过使用Qt MIPS仿真和学习其源码,可以更直观地理解嵌入式系统的组成、嵌入式CPU的指令集和流水线,以及部件级(如CPU、存储)和系统级的性能评价与优化方法等。Qt MIPS在我校的“嵌入式系统设计”实验教学中使用结果表明,它能明显加深学生对嵌入式系统设计相关理论知识的理解和融会贯通,同时对增强学生的嵌入式系统设计兴趣也起到意外的效果。

[1] 仲伟波, 包亚萍, 付跃文, 等. 关于嵌入式系统教学的几点思考[J]. 实验室研究与探索, 2006, 25(12),1565-1568.

[2] 左冬红, 罗 杰, 张 林, 等. 计算机原理与接口技术实践教学改革[J]. 实验室研究与探索, 2015, 34(10), 187-190.

[3] 龚 军, 罗 杰, 汪小燕. 基于仿真的嵌入式系统教学实验方法[J]. 实验室研究与探索, 2009, 28(5), 53-56.

[4] 付琳 , 胡 锦, 梁利平. 指令集仿真器的关键技术[J]. 计算机应用, 2015, 35(5): 1421-1425.

[5] 王盛朋, Vania Joloboff, 邓仰东. 一种基于近似计时模型的嵌入式CPU仿真器[J]. 计算机仿真, 2014, 31(5): 238-242.

[6] 李哲英, 骆 丽, 刘元盛. ARM 核嵌入式系统的开发平台ADS[J]. 半导体技术, 2002, 27(2): 13-16.

[7] Larus. J. SPIM: A MIPS32 simulator[EB/OL]. http://pages.cs.wisc.edu/~larus/spim.html.

[8] 阳 华, 刘海涛. 新一代TI集成开发环境Code Composer Studio[J]. 微处理机, 2001(2): 24-26.

[9] SimpleScalar[EB/OL]. http://www.simplescalar.com/.

[10] K. Vollmar and P. Sanderson. MARS: an education-oriented MIPS assembly language simulator[J]. ACM SIGCSE Bulletin, 2006, 38 (1): 239-243.

[11] Qt参考文档[EB/OL]. http://www.qtopia.org.cn/doc/qiliang.net/qt/index.html.

[12] 左冬红. 计算机原理与接口技术——基于MIPS架构[M]. 北京: 清华大学出版社, 2014.

[13] 赵俊良, 张福新, 陶 品. MIPS处理器设计透视[M]. 北京:北京航天航空大学出版社, 2005.

[14] Kumar T.S. Rajesh, Ravikumar C.P, Govindarajan R. Memory Architecture Exploration Framework for Cache Based Embedded SOC[C]. 21st International Conference on VLSI Design, 2008: 553-559.

[15] 曾宪彬. MIPS仿真器设计与应用[D]. 浙江: 杭州电子科技大学, 2013.

[16] J. L. Hennessy and D. A. Patterson, Computer Architecture: A Quantitative Approach[M]. San Francisco: Morgan Kaufmann Publishers Inc, 2002.

Development of Qt MIPS Software for Embedded System Design Experiments

YAOYing-biao,ZENGXian-bin

(College of Communication Engineering, Hangzhou Dianzi University, Hangzhou 310018, China)

Focusing on the experimental teaching of embedded system design, we developed a simulation platform for an embedded software and hardware, briefly called as Qt MIPS. The platform is based on Qt C++ application development framework. The features of Qt MIPS include that it has integrated the editor, assembler, simulator and debugger together, and has friendly man-machine interface; it supports cycle-accurate MIPS32 instruction simulation and parameterizes hierarchical memory system; it provides several performance statistics tools and source codes of its simulator are open for students. The usage practice of Qt MIPS shows that it can help students to have a better understanding the relevant theoretical knowledge and train students programming capability and performance analytical ability of embedded system design. Therefore, it can greatly improve the experimental teaching effect of embedded system design.

embedded systems; simulation software; experiments

2016-03-01

杭州电子科技大学《单片机与嵌入式系统》教学模式改革项目;高教重点改革项目(SYZD1108)

姚英彪(1976-),男,湖北松滋人,博士,副教授,硕士生导师,研究方向为嵌入式系统设计。E-mail:yaoyb@hdu.edu.cn

TP 391.9

A

1006-7167(2017)01-0098-06