超薄埋氧层厚度对FDSOI器件短沟道效应影响

谭思昊, 李昱东, 徐烨峰, 闫 江

( 1. 中国科学院 微电子研究所,北京 100029; 2. 微电子器件与集成技术重点实验室,北京 100029 )

超薄埋氧层厚度对FDSOI器件短沟道效应影响

谭思昊1,2, 李昱东1,2, 徐烨峰1,2, 闫 江1,2

( 1. 中国科学院 微电子研究所,北京 100029; 2. 微电子器件与集成技术重点实验室,北京 100029 )

随着CMOS技术发展到22 nm技术节点以下,体硅平面器件达到等比例缩小的极限。全耗尽超薄绝缘体上硅CMOS (FDSOI)技术具有优秀的短沟道效应控制能力,利用TCAD软件,对不同埋氧层厚度的FDSOI器件短沟道效应进行数值仿真,研究减薄BOX厚度及器件背栅偏压对器件性能和短沟道效应的影响。仿真结果表明,减薄BOX厚度使FDSOI器件的性能和短沟道效应大幅提升,薄BOX衬底背栅偏压对FDSOI器件具有明显的阈值电压调制作用,6.00 V的背栅偏压变化产生0.73 V的阈值电压调制。在适当的背栅偏压下,FDSOI器件的短沟道特性(包括DIBL性能等)得到优化。实验结果表明,25 nm厚BOX的FDSOI器件比145 nm厚BOX的FDSOI器件关断电流减小近50%,DIBL减小近20%。

FDSOI; 超薄埋氧层; 仿真研究; 短沟道效应; 背栅偏压

0 引言

随着CMOS(Complementary Metal Oxide Semiconductor)器件的特征尺寸缩小到22 nm技术节点,受短沟道效应和波动问题的影响,半导体生产制造业传统的器件结构达到尺寸等比例缩小的极限。如果通过提高沟道掺杂浓度控制短沟道效应,则导致结漏电增加和随机掺杂波动增大;同时,传统的体硅CMOS器件在栅长较短时几乎无法关断。全耗尽绝缘体上硅CMOS(FDSOI,Fully Depleted Silicon-on-Insulator)器件不需要通过沟道掺杂控制短沟道效应,使CMOS器件的特征尺寸可以持续缩小[1]。FDSOI能够较好地控制短沟道效应(SCE,Short-channel-effect),避免随机掺杂浓度波动(RDF,Random Doping Fluctuation),与传统体硅CMOS工艺流程兼容良好[2]。此外,在器件背面施加背栅偏压,不仅可以有效控制器件的SCE,也可以调节器件的阈值电压,以实现功耗管理目标[3]。

FDSOI器件成为主流CMOS技术的最大障碍在于,FDSOI器件性能取决于绝缘体上硅(SOI,Silicon-on-Insulator)厚度,同时获得均匀度很高的SOI衬底非常困难。Ito M等[4]使用ELTRAN技术制备50 nm厚埋氧层(BOX,Buried-Oxide)的SOI衬底。Delprat D等[5]大幅提升制备SOI衬底的工艺,获得SOI衬底的表层硅厚度在整个硅片上的波动小于1 nm。控制FDSOI器件短沟道效应的方法包括减薄沟道厚度[6]和施加背栅偏压[7]。Feng Shuai等[8]通过加强栅极对沟道载流子的控制能力,减弱源漏对沟道载流子的控制能力,提高器件的短沟道效应。实际上,减薄FDSOI器件的BOX厚度也可以起到相同的作用。Fenouillet-Beranger C等[9]使用超薄BOX(UTB,Ultra-thin BOX)结构实现多阈值电压器件的设计和制备。Liu Q等[10]研究超薄埋氧层(BOX厚度为25 nm)的FDSOI器件的性能和短沟道效应特性,制备的FDSOI器件具有出色的短沟道效应控制能力和电学特性。Liu Q等[11]研究更薄BOX(厚度为15 nm)的FDSOI器件,结果表明NFET和PFET器件的漏致势垒降低(DIBL,Drain Induced Barrier Lowering)性能得到优化。Doris B等[12]认为,在10 nm及其以下技术节点,减薄BOX厚度使器件的性能得到优化。Tang Z Y等[13]制备较厚的BOX(厚度为145 nm)的FDSOI器件,并研究器件性能和背栅偏压对器件的影响。受限于UTB SOI衬底的制备技术发展水平,我国在UTB FDSOI器件性能方面研究较少,也未见通过减薄BOX厚度优化FDSOI器件短沟道效应文献;在制备FDSOI器件时,由于仿真参数设定和制备工艺流程不明确,国外的研究成果难以参考。

笔者采用TCAD软件进行数值模拟,研究超薄BOX厚度及施加背栅偏压对FDSOI器件短沟道效应的影响,并制备FDSOI器件进行测试,分析减薄BOX厚度对器件性能和短沟道效应控制能力的影响,为UTB FDSOI器件的制备、BOX厚度对FDSOI器件的性能和短沟道效应的影响提供指导。

1 工艺流程仿真

采用TCAD软件,分别使用其中的SPROCESS和SDEVICE模块,对具有不同BOX厚度的FDSOI器件进行工艺结构和电学特性仿真(见图1)。首先,将衬底表层硅减薄至8.0 nm,热氧化后用氢氟酸刻蚀去除氧化层(见图1(a)),在形成假栅(见图1(b))和侧墙(见图1(c))后,用外延方法生长抬升源漏(RSD,Raised-SD)(见图1(d)),用离子注入并将源漏掺杂硼(B)。然后,在源漏掺杂后进行快速退火工艺,实现杂质的激活、推阱,以形成拓展区;完成两层侧墙的淀积和刻蚀(见图1(e))后,去除假栅,形成HK(High-K)和MG(Metal-Gate)结构(分别使用材料HfO2和TiN),进而形成硅化物(见图1(f))。最后,形成接触孔,结束金属化工艺,完成FDSOI器件的制备。

图1 UTB FDSOI器件工艺流程数值仿真Fig.1 Process flow simulation of UTB FDSOI devices

主要的FDSOI器件仿真参数:表层硅厚度为25.0 nm;第一层侧墙厚度为10.0 nm;第二层侧墙厚度为50.0 nm;RSD高度为35.0 nm;栅氧层厚度为0.5 nm;HK介质HfO2厚度为2.0 nm。BOX厚度分别为145.0、50.0、30.0、25.0、20.0、15.0和10.0 nm。为了说明沟道长度(即栅长)对器件性能的影响,对栅长25 nm的短沟器件和125 nm的长沟器件进行仿真,分析沟道长度对器件性能的影响。

2 仿真结果讨论

2.1 电学特性

2.1.1 电压

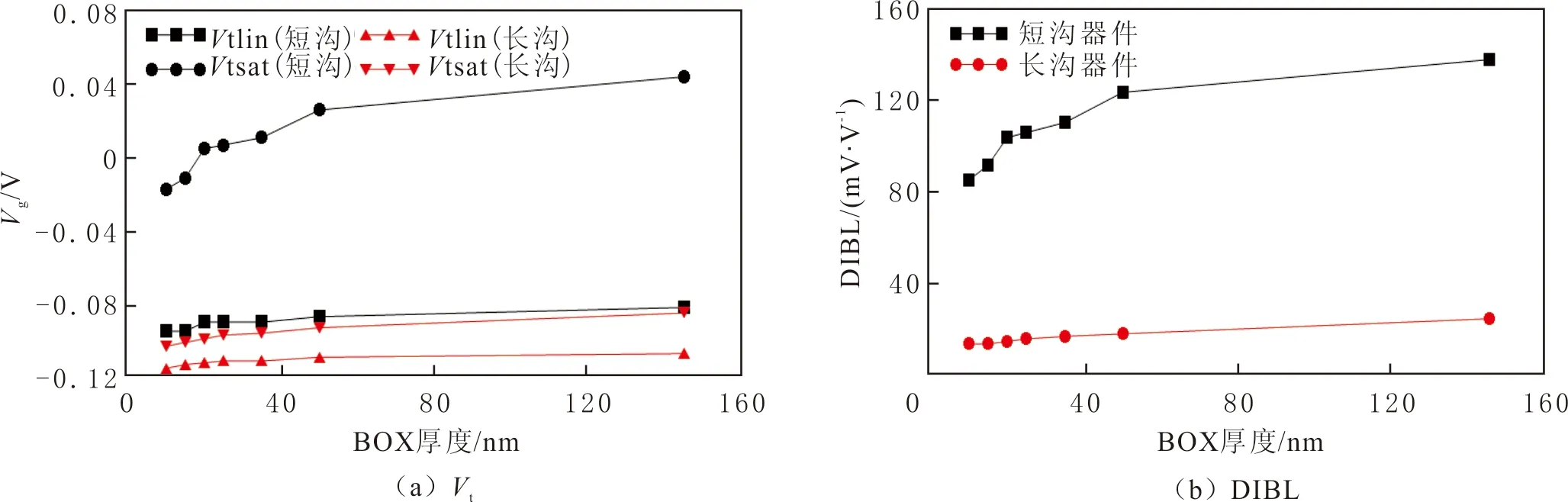

FDSOI器件漏端电流Id和栅极电压Vg的关系曲线即为转移特性曲线,表示器件输出电流与栅极施加电压的关系,是衡量器件性能的重要曲线。不同BOX厚度的FDSOI器件Id与Vg关系曲线见图2,其中线性区的源漏间电压VDS=-0.05 V,饱和区的VDS=-0.90 V;线性区漏端电流Idlin与Vg关系曲线用黑色表示;饱和区漏端电流Idsat与Vg关系曲线用红色表示。由图2可见,BOX厚度变化对线性区Idlin-Vg关系曲线几乎没有影响,而对饱和区Idsat-Vg关系曲线影响明显。这是因为工作于线性区的器件沟道区域几乎没有源漏电场耦合,BOX厚度变化对沟道载流子的电场影响比较小;工作于饱和区的器件沟道区域受源漏电场耦合作用影响,BOX厚度变化的影响更明显。根据图2可以获得FDSOI器件的阈值电压Vt,在Id=1×10-7A时,由Idlin-Vg曲线提取不同BOX厚度器件的线性区阈值电压Vtlin;由Idsat-Vg曲线提取不同BOX厚度器件的饱和区阈值电压Vtsat,并计算DIBL(DIBL=Vtsat-Vtlin)。长沟(LG=125 nm)和短沟(LG=25 nm)FDSOI器件的Vt、DIBL与BOX厚度关系曲线见图3。由图3(a)可见,长沟和短沟器件的线性区阈值电压Vtlin变化比较小,其饱和区阈值电压变化更为明显,因此根据其差值绘制的曲线形状与两者的饱和区阈值电压Vtsat曲线形状相似(见图3(b))。

图2 不同BOX厚度FDSOI器件的Id-Vg曲线Fig.2 Id-Vg curves of FDSOI devices with different BOX thickness

图3 长沟和短沟FDSOI器件的Vt、DIBL与BOX厚度变化关系曲线Fig.3 Vt and DIBL curves of short-channel and long-channel FDSOI devices with different BOX thickness

由图3(a)可见,受短沟道效应的影响,当FDSOI器件的沟道长度变小时,阈值电压绝对值约降低50%。这是因为源漏间的电场耦合作用对器件产生影响,而UTB结构能够减小耦合作用,更薄厚度的BOX层使从源漏出发的电场线更多地终止于衬底,加强栅极对沟道载流子的控制能力,进而使阈值电压绝对值降低程度减小。当BOX厚度变化时,长沟器件的阈值电压绝对值基本不变,短沟器件的饱和区阈值电压绝对值约增加0.06 V。因此,BOX厚度对短沟器件饱和区阈值电压的影响远大于线性区的,随着BOX厚度的减小,器件的DIBL得到优化(减小60 mV/V)。

2.1.2 电流

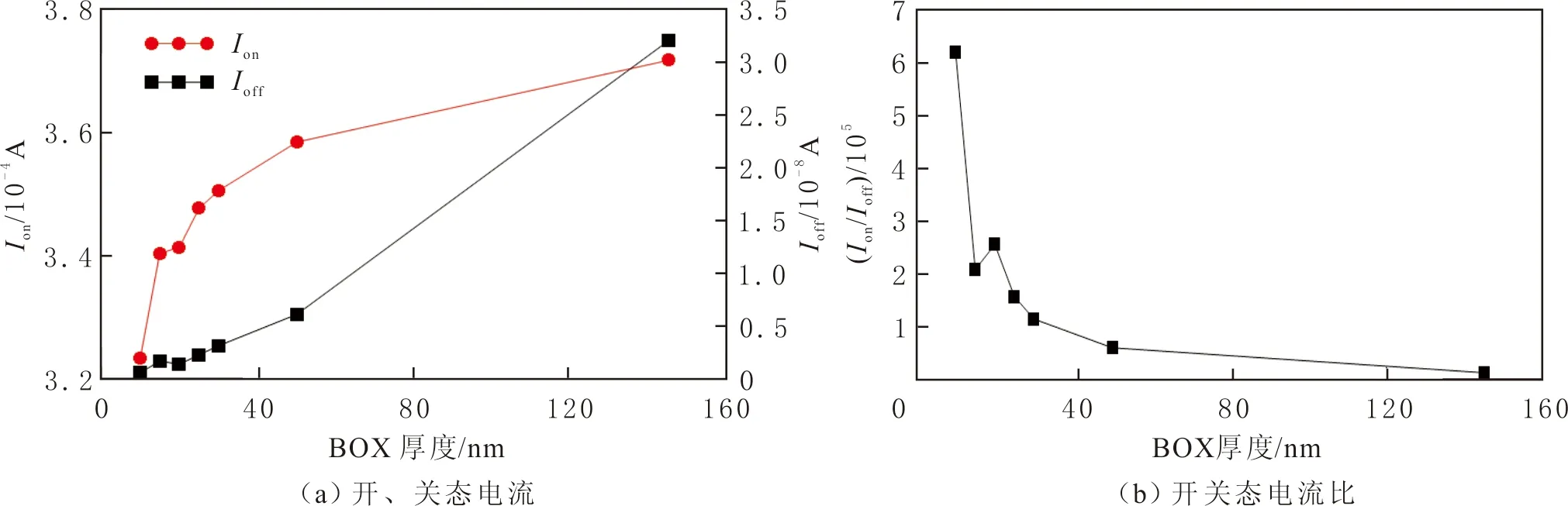

FDSOI器件阈值电压和沟道势垒的变化影响电流性能,对BOX厚度变化对器件电流性能的影响进行仿真。国际半导体技术蓝图(ITRS,International Technology Roadmap for Semiconductors)[14]指出,基准器件的阈值电压为-0.19 V,开态电流Ion在开态电压Von=-0.90 V处取得,关态电流Ioff在关态电压Voff=0.01 V处取得。由于FDSOI器件的阈值电压不同,为了比较电流性能,开态电流Ion在-0.90 V~(-0.19 V-Vtsat) 处提取,关态电流Ioff在0.01 V~(-0.19 V-Vtlin)处提取,计算开关态电流比Ion/Ioff,绘制不同BOX厚度FDSOI器件的开态、关态电流及开关态电流比曲线(见图4)。在仿真过程中,为了减少变量、更好地研究不同BOX厚度对器件性能的影响,没有进行功函数的调制。

由图4(a)可见,在BOX厚度从145 nm减薄到10 nm时,FDSOI器件的Ion减小4.85×10-5A,减小13.0%。这是因为随BOX厚度的降低,栅极电场在沟道中的场强增加,影响沟道载流子的迁移率。

当漏端施加高电压时,在漏端电场影响下,沟道源端附近的势垒降低,即漏致势垒降低(DIBL),增加从源端注入沟道的载流子数量,并在Vg没有达到阈值电压时允许载流子在源漏之间流通,产生关态电流Ioff,进而影响器件的关断性能。因此,优化DIBL性能可以有效降低器件的关态电流Ioff(见图4(a))。由图4(a)可见,在BOX厚度从145.0 nm减薄到10.0 nm时,FDSOI器件的Ioff减小98.4%,关态电流性能明显提升。

图4 不同BOX厚度FDSOI器件的开、关态电流及开关态电流比曲线Fig.4 Ion, Ioff and Ion/Ioff curves of FDSOI devices with different BOX thickness

由图4(b)可见,在BOX厚度从145.0 nm减薄到10.0 nm时,FDSOI器件的开关态电流比(Ion/Ioff)增加53.3倍,FDSOI器件的电学性能明显提升。其中BOX厚度为20.0 nm时,开关态电流比显示异常,原因是仿真网格划分导致该处计算结果不收敛,重新划分网格后对该点进行仿真计算,产生数据异常。

2.2 背栅偏压

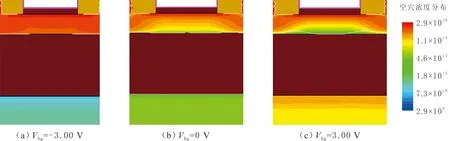

在背栅偏压(Vbg)为-3.00~3.00 V时,25.0 nm BOX厚度、25.0 nm栅长、8.0 nm表层硅厚度的PMOSFET空穴浓度的分布见图5。由图5可见,在背栅偏压为-3.00 V时,沟道高浓度空穴宽度最宽,空穴占据整个沟道,衬底空穴浓度较低,因此电子浓度较高,衬底处于积累状态(见图5(a))。在无背栅偏压(0 V)时,沟道高浓度空穴宽度比负偏压时的窄,衬底空穴浓度略高,因此电子浓度降低,衬底处于耗尽状态(见图5(b))。当背栅偏压为3.00 V时,沟道高浓度空穴宽度最窄,衬底空穴浓度较高,因此电子浓度更低,衬底处于反型状态(见图5(c))。

图5 UTB FDSOI器件在不同背栅偏压下空穴浓度分布Fig.5 Distribution of holes in UTB FDSOI device under different Vbg

沿垂直沟道方向进行加权平均,计算空穴浓度的平均沟道位置[15]。当背栅偏压Vbg为-3.00 V时,平均沟道位置远离前栅。在Vbg为正时,平均沟道位置向前栅移动,并且偏压越大,两者越接近。在衬底偏压由正变负过程中,平均沟道位置由前栅表面向衬底与BOX界面靠近,导致前栅正下方的耗尽宽度向BOX延伸,最终衬底耗尽甚至反向积累。在施加背栅偏压时,由反背栅偏压到正背栅偏压过程中,衬底耗尽区向埋层氧化物延伸,使耗尽区宽度增加,DIBL变大,FDSOI器件的短沟道效应增强[16]。因此,在衬底施加反背栅偏压时,FDSOI器件平均沟道位置逐渐靠近前栅,DIBL减小,可以更好地控制FDSOI器件的沟道效应。

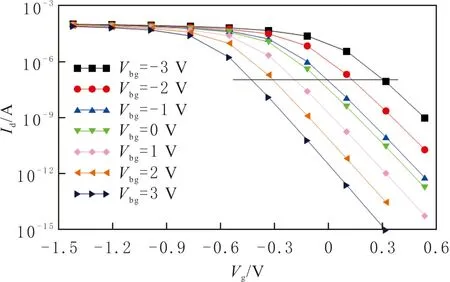

在背栅偏压为-3.00~3.00 V时,UTB FDSOI器件的Idlin-Vg曲线见图6,其中横线表示Id=1×10-7A的位置。由图6可见,在背栅偏压从-3.00 V变化到3.00 V时,25.0 nm BOX厚度的UTB FDSOI器件得到0.73 V阈值电压的调制。对于145.0 nm BOX厚度的FDSOI器件的背栅偏压对阈值电压的调制[13],在背栅偏压从-20.00 V变化到20.00 V时才能得到0.73 V的阈值电压调制。因此,25.0 nm BOX厚度的UTB FDSOI器件对背栅偏压的灵敏度比145.0 nm BOX厚度的高。

图6 背栅偏压对UTB FDSOI器件Idlin-Vg调制曲线

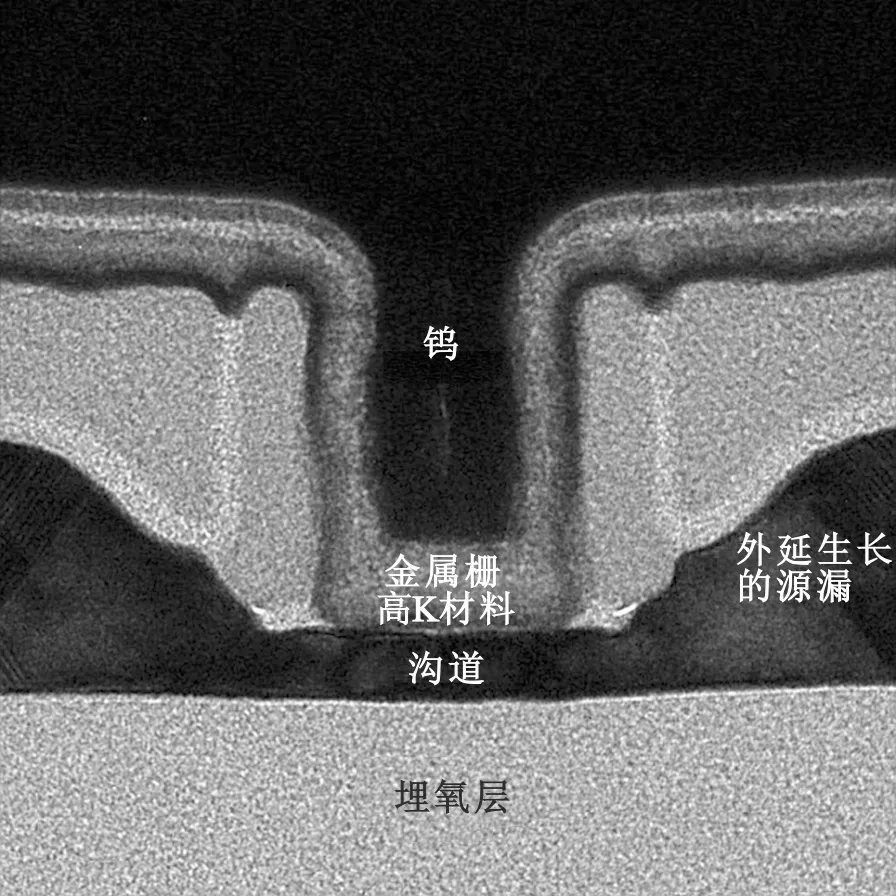

图7 25.0 nm BOX厚度UTB FDSOI器件结构剖面Fig.7 Cross-section view of UTB FDSOI device(BOX thickness 25.0 nm)

3 实验验证

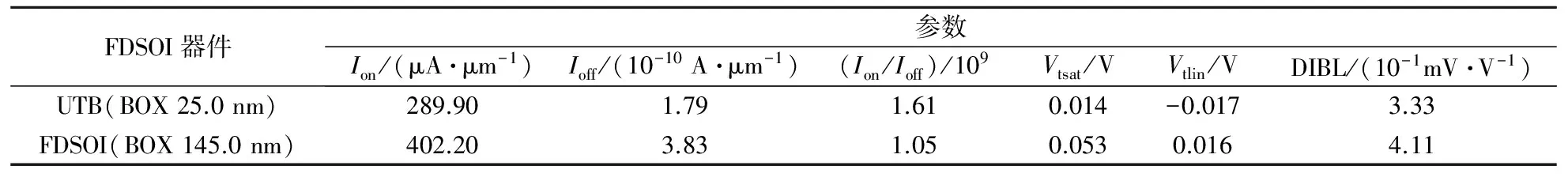

制备25.0 nm BOX厚度和145.0 nm BOX厚度的FDSOI器件,器件参数与仿真参数相同。25.0 nm BOX厚度的FDSOI器件剖面见图7。两种器件性能测试参数见表1,参数经过归一化处理。

由表1可见,25.0 nm BOX厚度 UTB FDSOI器件和145.0 nm BOX厚度FDSOI器件的线性区阈值电压Vtlin分别为-0.017、0.016 V, 25.0 nm BOX厚度UTB FDSOI器件的线性区阈值电压更接近基准器件的(-0.19 V),并且器件的DIBL由41.1 mV/V减小到33.3 mV/V,Ioff降低53.26%,Ion降低27.90%,Ion/Ioff提升53.33%,与仿真结果的参数变化趋势相同,表明减小BOX厚度可以提升FDSOI器件性能。另外,开态电流Ion与开关态电流比Ion/Ioff的变化幅度与仿真结果存在一定差距,说明制备的FDSOI器件性能还可以优化。

表1 25.0、145.0 nm厚度BOX FDSOI器件的电学特性

4 结论

(1)仿真结果显示,BOX厚度降低可以优化FDSOI器件的阈值电压和DIBL性能。当BOX厚度从145.0 nm变为25.0 nm时,FDSOI器件的DIBL减小21%。

(2)仿真结果显示,当BOX厚度从145.0 nm减小到25.0 nm时,FDSOI器件的电流性能得到提升,关态电流减小93.1%,器件的关断特性大幅提升;开态电流减小6.4%,器件的开关态电流比提升13.5倍。

(3)仿真结果显示,对于25.0 nm BOX厚度 FDSOI器件,背栅偏压从-3.00 V变化到3.00 V时,阈值电压调制幅度达到0.73 V,比145.0 nm BOX厚度 FDSOI器件对背栅偏压的敏感度高,调节背栅偏压可以优化UTB FDSOI器件的短沟道性能。

(4)制备25.0 nm BOX厚度UTB FDSOI器件与145.0 nm BOX厚度 FDSOI器件。25.0 nm BOX厚度器件比145.0 nm BOX厚度器件的DIBL减小19.0%,关态电流减小53.26%,开态电流减小27.90%,开关态电流比提升53.33%。减薄BOX厚度对FDSOI器件性能有明显提升。

[1] Cheng K, Khakifirooz A, Kulkarni P, et al. Extremely thin soi (ETSOI) technology: Past, present, and future [C]//Proceedings of the 2010 IEEE International SOI Conference. San Diego, CA: IEEE, 2010:1-4.

[2] Faynot O, Andrieu F, Weber O, et al. Planar fully depleted SOI technology: A powerful architecture for the 20nm node and beyond [C]//Proceedings of the Electron Devices Meeting (IEDM) 2010 IEEE International. San Fransisco, CA: IEEE, 2010:3.2.1-3.2.4.

[3] Brozek T. Micro-and nanoelectronics: Emerging device challenges and solutions [M]. CRC Press, 2014:218-221.

[4] Ito M, Yamagata K, Miyabayashi H, et al. Scalability potential in Eltran (R) SOI-epi wafer [C]//Proceedings of the 2000 IEEE International SOI Conference. Wakefield, MA: IEEE, 2000:10-11.

[5] Delprat D, Boedt F, David C, et al. SOI substrate readiness for 22/20 nm and for fully depleted planar device architectures [C]//Proceedings of the 2009 IEEE International SOI Conference. Foster city, CA: IEEE, 2009:1-4.

[6] Majumdar A, Wang X, Kumar A, et al. Gate length and performance scaling of undoped-body extremely thin SOI mosfets [J]. Electron Device Letters, IEEE, 2009,30(4):413-415.

[7] Khakifirooz A, Cheng K, Reznicek A, et al. Scalability of extremely thin soi (ETSOI) MOSFETs to sub-20 nm gate length [J]. Electron Device Letters, IEEE, 2012,33(2):149-151.

[8] Feng Shuai, Zhao Lichuan, Zhang Qingzhu, et al. A simulation analysis of performance of both implanted doping and in situ doping ETSOI pMOSFETs [J]. Journal of Semiconductors, 2015,(4):184-188.

[9] Fenouillet-Beranger C, Perreau P, Pham-Nguyen L, et al. Hybrid FDSOI/bulk high-K/metal gate platform for low power (lp) multimedia technology [C]//Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM). Baltimore, MD: IEEE, 2009:1-4.

[10] Liu Q, Yagishita A, Loubet N, et al. Ultra-thin-body and box(UTBB) fully depleted(FD) device integration for 22nm node and beyond [C]//Proceedings of the 2010 Symposium on VLSI Technology (VLSIT). Honolulu: IEEE, 2010:61-62.

[11] Liu Q, DeSalvo B, Morin P, et al. FDSOI CMOS devices featuring dual strained channel and thin box extendable to the 10 nm node [C]//Proceedings of the 2014 IEEE International Electron Devices Meeting (IEDM). San Fransisco, CA: IEEE, 2014:9.1.1-9.1.4.

[12] Doris B, DeSalvo B, Cheng K, et al. Planar fully-depleted-silicon-on-insulator technologies: Toward the 28 nm node and beyond [J]. Solid-State Electronics, 2016,117:37-59.

[13] Tang Z Y, Tang B, Zhao L C, et al. Impacts of back gate bias stressing on device characteristics for extremely thin SOI (ETSOI) MOSFETs [J]. Electron Device Letters, IEEE, 2014,35(3):303-305.

[14] Paolo G. International Technology Roadmap for Semiconductors 2014[DB/OL]. http://www.itrs2.net/,2016.

[15] 冯帅.14/16 nm ETSOI器件仿真与研制[D].贵州:贵州大学,2015. Feng Shuai. Simulation and fabrication of 14/16 nm ETSOI devices [D]. Guizhou: Guizhou University, 2015.

[16] Colinge J P. FinFETs and other multi-gate transistors [M]. USA: Springer, 2008:102-106.

2016-08-01;编辑:张兆虹

国家科技重大专项(2013ZX02303-001-001)

谭思昊(1990-),男,硕士研究生,主要从事SOI器件结构与工艺方面的研究。

TN386.1

A

2095-4107(2017)01-0117-06

DOI 10.3969/j.issn.2095-4107.2017.01.012