新型高性能超宽带低噪声放大器设计

李相敏,康 壮

(长江大学文理学院,湖北 434020)

新型高性能超宽带低噪声放大器设计

李相敏,康 壮

(长江大学文理学院,湖北 434020)

基于0.18 μm CMOS工艺,设计了一款工作于4.2~11.9 GHz的低噪声超宽带低噪声放大器(LNA)。该LNA采用一种增强π型匹配输入网络实现超宽带输入阻抗匹配以及平坦的高增益。为了取得较低且平坦的噪声系数,将二阶噪声系数频率响应的极点频率和极点品质因数优化到最大平坦状态。流片实现的芯片测试结果表明:该LNA消耗了10.1 mW的功耗,在低于13.3 GHz的频率下S11均低于-10 dB,在频率2~12.2 GHz间,取得了12.6±1.5 dB的高增益,表明该LNA的3 dB带宽为10.2 GHz。而且,该LNA在8 GHz下取得了2.4 dB的最小噪声系数,在4.2~11.9 GHz频率间,噪声系数为2.6±0.2 dB。在8 GHz频率下,测试得到的输入三阶交调截止点IIP3为-0.5 dBm。

高性能;低噪声放大器;超宽带;低功耗

0 引 言

近年来,性能优良的超宽带CMOS低噪声放大器(LNA)在文献中多有报道[1]。例如,文献[2]报道了一种超低功耗的超宽带LNA,该LNA在0.5 V电压供电下,消耗了0.75 mW的功耗,取得了12.6 dB的增益,但是噪声系数性能较差,高达5.5 dB;文献[3]所报道的基于65 nm CMOS设计完成的LNA,增益为13 dB,噪声系数取得了2.1~3.5 dB的良好性能,但是由于电路中的有源器件过多,导致了功耗过大,功耗高至20.8 mW;文献[4]报道了一款基于90 nm CMOS工艺设计完成的两级LNA,虽然取得了7.2 mW的较低功耗, 11±1.5 dB的较平坦增益S21,但是噪声系数性能较差;文献[5]采用宽带双级RLC分支输入匹配网络实现两级CMOS LNA的超宽带工作,但是该结构需要嵌入五个电感,占用了过大的芯片面积,不利于成本的降低;为了进一步降低文献[5]中LNA的功耗,文献[6]引入了衬底正向偏置技术,但是退化了电路的噪声,并且仍需要在电路中嵌入五个电感;本文为了同时实现小芯片面积、合理的功耗、较高且平坦的增益、和较低且平坦的噪声系数,提出并设计了一种嵌有三个电感的超宽带两级LNA。

1 电路设计

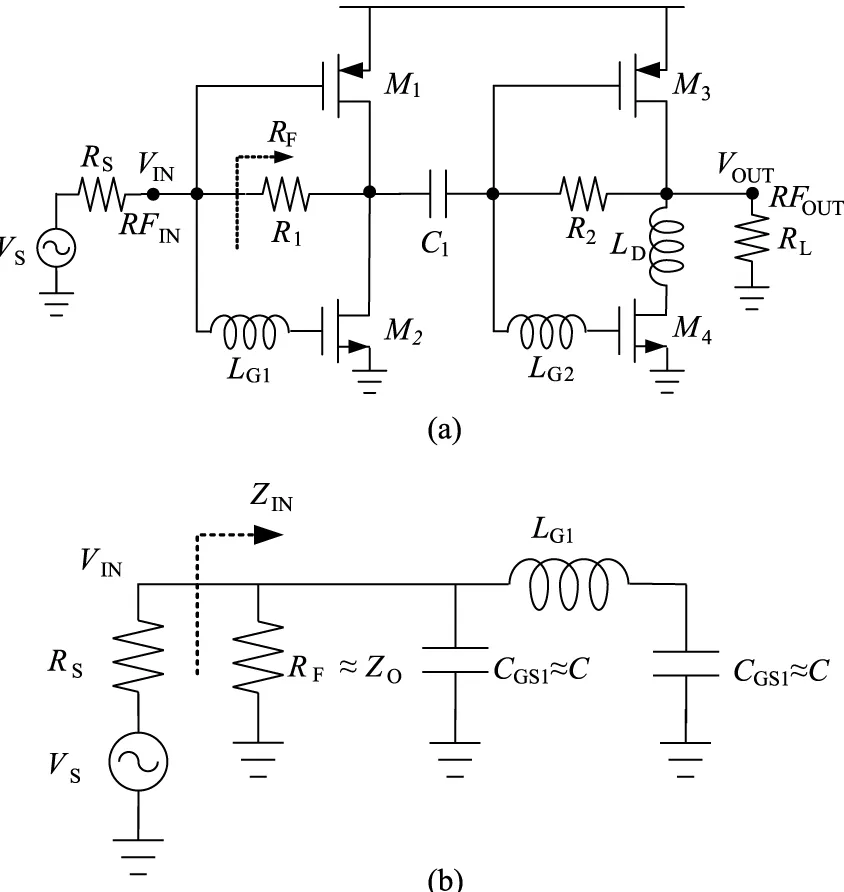

本文所提出的基于反相器形式的两级LNA电路图如图1(a)所示,电路中晶体管M2和M4分别利用晶体管M1和M3的偏置电流,不需增加额外的驱动电流,降低了电路整体功耗。

图1 提出的CMOS LNA (a) 电路图 (b) 输入等效电路

图1(b)所示为用于计算LNA输入阻抗ZIN的小信号输入等效电路,经分析,可得ZIN的表达式如下所示:

(1)

其中,RF为从并联-并联反馈电阻R1左端看进去的等效电阻,CGS1和CGS2分别为晶体管M1和M2的栅源间电容。由晶体管M3的栅源间电容CGS3、LG2和晶体管M4的栅源间电容CGS4组成的π型网络的输入阻抗Zπ,在大约15 GHz频率处无穷大,因此可以假设在电路工作的整个频带内忽略掉Zπ的影响,进而可得RF可近似表达为:

(2)

为了取得较宽的阻抗匹配,要使RF≈ZO=ZIN(ZO为特性阻抗,50 Ω),进而利用RF≈ZIN关系式,推得在以下两个频率ω01、ω02处可以获得完美的输入匹配状态[7]。

(3)

(4)

在电路设计中,选取合适的参数,使得CGS1≈CGS2=C,式(4)可简化为:

(5)

图2(a)给出了一种传统的LNA电路,以用于与本文所提出的电路相比较,无源器件CIN退化了电路的噪声性能。图2(b)所示为此传统LNA的小信号输入等效电路。根据实际情况,假设CIN≈C,并且CGS1+CGS2≈C,可得到该传统LNA在以下两个频率ω01、ω02处可以获得良好的输入匹配状态。

(6)

(7)

图2 传统LNA (a) 电路图 (b)输入等效电路

ω02越大,电路的输入匹配带宽越宽,由式(5)和式(7)比较可见,本文所提出的LNA表现出了更宽的带宽,可以实现更宽的阻抗匹配。

表征本文所提出的LNA增益的S21参数为[7]:

(8)

(9)

式(8)中,第一项和第三项的幅度随着频率的增加而增加,第二项和第四项的幅度随着频率的增加而降低,最终结果使得放大器可以在较宽的频带内实现平坦的高增益。

由于第一级电路具有较高的增益,因此可忽略第二级电路噪声对整体LNA的影响,因此该LNA的噪声系数可表示为[7-8]:

(10)

其中:

(11)

(12)

(13)

(14)

由式(10)中的第三项可以看出CGS1可以减弱源阻抗RS热噪声的影响,尤其在高频下,此效果更加显著。而且,由式子中的第五项可得,为了进一步降低RS对电路噪声系数的影响,本文选取较大的R1电阻值,因而可得LNA的噪声系数主要由第四项所决定,也就是说由晶体管M1和M2的漏极噪声所决定,本设计中将Qdn和ω0,dn调整到最大平坦变化状态,因此可得到较低的且平坦的噪声系数。

2 测试结果与讨论

基于SMIC 0.18 μm CMOS工艺,对本文的LNA进行设计并流片实现,图3给出了本文所设计实现的LNA芯片照片,面积大小为0.91×0.56 mm2。此电路在1.8 V的工作电压下,消耗了10.1 mW的功耗。图4所示为输入反射系数S11的测试结果,此LNA在频率4.2~11.9 GHz间,S11为-11.5~-12.8 dB,并且在低于13.3 GHz的频率下S11均低于-10 dB。

图3 超宽带CMOS LNA芯片照片

图4 LNA的S11测试结果

图5给出了LNA的噪声系数NF的测试结果,该LNA在8 GHz下取得了2.4 dB的最小噪声系数,在4.2~11.9 GHz频率间,噪声系数为2.6±0.2 dB。图6给出了增益S21前仿真、后仿真和实际测试对比结果,可见测试结果表明在频率2~12.2 GHz间,取得了12.6±1.5 dB的高增益,表明该LNA的3 dB带宽为10.2 GHz,而且,前仿真、后仿真以及测试结果三者之间的误差在正常的测试误差范围内。图7 给出了输入三阶交调截止点IIP3在8 GHz频率下的测试结果,IIP3为-0.5 dBm,取得了良好的线性度。

图5 噪声系数NF测试结果

表1给出了该LNA与以往文献中所报道的超宽带LNA的对比结果,其中品质因素FOM指标采用式(7)计算得到,由表1可见,本文所提出的LNA具有较小的芯片面积,较低的噪声系数,较平坦的高增益,以及最高的FOM指标。

图6 增益S21电路仿真、版图后仿真以及测试结果

图7 输入三阶交调截止点IIP3测试结果

(7)

其中,BW为电路的频带宽度,PD为电路的功耗。

表1 超宽带CMOS LNA比较结果

3 结 语

本文在理论分析的基础上,针对以往文献中所报道的超宽带LNA的不足,提出并流片实现了一种低功耗、低相位噪声以及高增益的超宽带CMOS LNA。芯片实测结果表明,该LNA在4.2~11.9 GHz超宽工作频率下,实现了较好的性能,表明本文所提出的LNA电路结构以及设计方法非常适合于超宽带通信系统中。

[1] 黄阳镇, 耿军平, 金荣洪, 等. C波段下变频器的设计与实现 [J]. 中国电子科学研究院学报, 2014, 9(6): 643-647.

[2] PARVIZI M, ALLIDINA K, GAMAL M N. A sub-mW, ultra-low-voltage, wideband low-noise amplifier design technique [J]. IEEE Transactions on Very Large Scale Integration Systems, 2015, 23(6): 1111-1122.

[3] CHUNG T, LEE H, JEONG D, et al. A wideband CMOS noise-canceling low-noise amplifier with high linearity [J]. IEEE Microwave and Wireless Components Letters, 2015, 25(8): 547-549.

[4] SAPONE G, PALMISANO G. A3-10-GHz low-power CMOS low-noise amplifier for ultra-wideband communication [J]. IEEE Transactions on Microwave Theory and Technology, 2011, 59(3): 678-686.

[5] WU C H, LIN Y S, LEE J H, et al. A 2.87±0.19 dB NF 3.1~10.6 GHz ultra-wideband low-noise amplifier using 0.18 μm CMOS technology. (In): IEEE. IEEE Radio and Wireless Symposium (RWS) [C] //. CA Santa Clara: IEEE, 2012: 227-230.

[6] WU C H, LIN Y S, WANG C C. A 3.1~10.6 GHz current-reused CMOS ultra-wideband low-noise amplifier using self-forward body bias and forward combining techniques [J]. Microwave and Optical Technology Letters, 2013, 55(10): 2296-2302.

[7] LIN Y S, CHANG J F, LU S S. Analysis and design of CMOS distributed amplifier using inductively peaking cascaded gain cell for UWB systems [J]. IEEE Transactions

on Microwave Theory and Technology, 2011, 59(10): 2513-2524.

[8] CHIU H W, LU S S, LIN Y S. A 2.17-dB NF 5-GHz-band monolithic CMOS LNA with 10-mW DC power consumption [J]. IEEE Transactions on Microwave Theory and Technology, 2005, 53(3): 813-824.

[9] HU B, YU X P, LIM W M, et al. Analysis and design of ultra-wideband low-noise amplifier with input/output bandwidth optimization and single-ended/differential-input reconfigurability [J]. IEEE Transactions on Industrial Electronics, 2014, 61(10): 5672-5680.

[10]LEE H, Chung H, Seo H, et al. A wideband differential low-noise-amplifier with IM3 harmonics and noise canceling [J]. IEEE Microwave and Wireless Components Letters, 2015, 25(1): 46-48.

Design of a New High-Performance Ultra-Wideband Low-Noise Amplifier

LI Xiang-min, KANG Zhuang

(Yangtze University College of Arts and Sciences, Hubei 434020, China)

A low noise-figure (NF) and high power gain 4.2~11.9 GHz ultra-wideband low-noise amplifier (UWB LNA) using 0.18 CMOS technology is reported. An enhanced π-match input network is used to achieve wideband input impedance matching as well as high and flat gain. To achieve low and flat NF, the pole frequency and pole quality factor of the second-order NF frequency response are tuned to approximate the maximally flat condition. The LNA consumes 10.1 mW, achieving S11 lower than -10 dB for frequency lower than 13.3 GHz. Additionally, high and flat gain of 12.6±1.5 dB is achieved for frequencies 2~12.2 GHz, which means the corresponding 3-dB bandwidth is 10.2 GHz. Furthermore, the LNA achieves minimum NF of 2.4 dB at 8 GHz and NF of 2.6±0.2 dB for frequencies of 4.2~11.9 GHz. The measured input third-order intermodulation point (IIP3) is -0.5 dBm at 8 GHz.

High performance; low noise amplifier; ultra wideband; low power

10.3969/j.issn.1673-5692.2017.01.019

2016-09-17

2017-01-09

李相敏(1981—),男,湖北人,实验师,主要研究方向为超宽带低噪声放大器设计;

E-mail: limin_jinzhou@sina.com;

康 壮(1987—),男,湖北人,助教,主要研究方向为射频电路。

TN432

A

1673-5692(2017)01-106-05