常用逻辑门芯片测试装置研究与设计

刘 艳, 唐海贤, 景 昊, 张 斌, 高 茜

(河海大学 物联网工程学院, 江苏 常州 213022)

常用逻辑门芯片测试装置研究与设计

刘 艳, 唐海贤, 景 昊, 张 斌, 高 茜

(河海大学 物联网工程学院, 江苏 常州 213022)

结合数字电路相关课程的改革,针对数字电路中常用的74/54系列逻辑门芯片,研究并设计了一种基于单片机最小系统的常用逻辑门芯片测试装置。该装置为电子技术相关理论和实践教学提供了快速、直观、稳定的测试方式,提高了实验室芯片检测的效率与准确率,同时也提高了理论与实验课程的教学效果。

数字电路; 逻辑门; 芯片测试; 实践教学

在数字化、智能化的发展潮流中,数字电路以及数字电子技术所承担的信息采集、存储、处理与传输等功能,使得数字电路相关内容在工科教学中愈发重要。作为高等学校的一门专业基础课,“数字电子技术”课程兼具理论性与系统性、工程性与实践性等特点,在本科教学体系中更是起着不可缺少的作用[1]。

数字电子实验箱(或实验系统)作为数字电子技术实验的基础载体,得到了广泛使用,也在不断的改进中。民国时期出现的电化教具[2]在教学过程中的普遍使用是教育现代化的标志,体现了教具在提高教学质量方面的作用;早先严世胜等[3]针对电子技术的实验装置进行了改进;之后赵巧妮[4]因传统庞大的数字电路实验箱体积庞大、价格较贵等原因,设计了一款便携式的简易数字电路实验板;全晓丽等[5]针对某些高校存在的实验室设备陈旧、实验室规模小、实验室建设经费短缺等问题提出并设计了运用LabVIEW平台设计的数字电路教学虚拟实验系统。为解决数字电路故障诊断的测试要求,陈飞等[6]提出了基于电流信息的COMS SRAM存储单元故障测试方法;葛青等[7]根据边界扫描测试标准IEEE1149.1设计了数字电路测试主控系统。随着教具的研制与使用,教具对教学质量的提升逐渐被广大教员认可,教具的研制与检修也受到关注。随着单片机应用和教学的普及,如张江印[8]的研究,以单片机为主控制器的嵌入式设备也越加普及。

本课题组结合江苏高校品牌专业建设工程和国家“卓越计划”项目,开展了“以学生为本”的一系列教学改革[9]。结合翻转课堂教学模式,为激发学生对课程学习的兴趣,加深学生对理论知识的理解,培养学生动手的积极性,提高理论与实验课程的教学效果,简化实验室芯片的故障排查工作,本课题组基于数字电子技术教学常用的74/54系列逻辑门芯片设计了一种简单快捷、高效的14引脚DIP封装的逻辑门芯片检测装置。

1 检测装置的设计思路

74/54系列逻辑门种类繁多,有与、或、非、与非、或非、异或等逻辑,有一输入、二输入、三输入、四输入等不同输入数量,因此需要根据芯片的不同逻辑关系、不同输入量来设计检测装置。本装置针对14引脚DIP封装的逻辑门进行测试,每次检测时需要以按键形式手动输入芯片类型,自动检测出芯片功能是否正常。

检测装置由模式选择模块、主控芯片、待测芯片模块和结果显示模块组成。根据模式选择模块确定的逻辑门电路芯片类型,主控芯片控制待测芯片模块的继电器电路给待测芯片供电,并根据芯片的真值/功能表

判断芯片功能是否完好,最后将结果显示。图1为装置整体框图。

图1 装置整体框图

2 电路设计

待测芯片检测装置基于STC89C52单片机最小系统开发[10],电路见图2。

图2 芯片检测装置电路

模式选择模块由4×4矩阵键盘构成,如图2中所示。矩阵式键盘具有节约控制芯片I/O口的优点。本矩阵键盘在仅占用8个I/O口的情况下完成16个不同逻辑门芯片选择的目的。16个按键被可定义为16种模式,其中S1—S12依次代表12种芯片测试模式:2×四输入与门、2×四输入或门、2×四输入与非门、2×四输入或非门、4×二输入与门、4×二输入或门、4×二输入与非门、4×二输入或非门、4×二输入异或门、一非门、二非门、三非门,其余按键暂不使用。

主控芯片模块采用高性能的STC89C52单片机作为主控芯片。本装置充分利用该片MCU上的所有资源,利用其I/O口的输入、输出电平的变化完成矩阵键盘按键读取、待测芯片引脚电平测试、结果输出3个主要功能。待测芯片的逻辑功能及对应的真值表数据预存在MCU的Flash存储器中。每次检测均利用芯片的定时器实现时间间隔相同、对待测芯片更具真值表的每一种电平情况进行检测。

待测芯片(逻辑门芯片)模块包含一个DIP14芯片底座和继电器电路。待测芯片底座适合市面上常用逻辑门芯片的封装共性,采用DIP14的芯片底座作为芯片的插入底座,将引脚14接VCC,将引脚7作为GND,并采用继电器来控制引脚7与GND线的通断来控制待测芯片的上电与断电。考虑到单片机I/O口电流较小,为保护单片机不被继电器线圈产生的大电流损坏、提高单片机I/O口的驱动能力,使用NPN三极管来放大控制电流,并作为一个隔离器件,保护单片机免受大电流冲击。待测芯片的引脚号1—6和8—13分别接单片机P0.0-P0.7和P2.0-P2.3端口。

结果显示模块采用2个LED灯来表示芯片的完好与故障两种情况。LED灯直接与单片机的I/O口相连,并且为每个LED灯接一个限流电阻,来保证LED灯不被大电流烧坏、单片机不被大电流损坏。

3 软件设计

3.1 待测逻辑门芯片功能分析

3.1.1 与门

有2×四输入与门、4×二输入与门2种。2×四输入与门的逻辑表达式[11]为

L=A·B·C·D

对应模式S1,其对应芯片到的逻辑表达式为

4×二输入与门的逻辑表达式为

L=A·B

对应模式S5,其对应芯片到的逻辑表达式为

3.1.2 或门

有2×四输入或门、4×二输入或门2种。2×四输入或门的逻辑表达式为

对应模式S2,其对应芯片到的逻辑表达式为

4×二输入或门的逻辑表达式为

L=A+B

对应模式S6,其对应芯片到的逻辑表达式为

3.1.3 与非门

有2×四输入与非门、4×二输入与非门2种。2×四输入与非门的逻辑表达式为

对应模式S3,其对应芯片到的逻辑表达式为

4×二输入与非门的逻辑表达式为

对应模式S7,其对应芯片到的逻辑表达式为

3.1.4 或非门

有2×四输入或非门、4×二输入或非门2种。2×四输入或非门的逻辑表达式为

对应模式S4,其对应芯片到的逻辑表达式为:

4×二输入或非门的逻辑表达式为

对应模式S8,其对应芯片到的逻辑表达式为:

3.1.5 异或门

即4×二输入异或门,其逻辑表达式为

对应模式S9,其对应芯片到的逻辑表达式为

2.1.6 非门

有一非门、二非门、三非门3种,分别对应模式S10、S11、S12。非门的逻辑表达式为

S10对应芯片到的逻辑表达式为

S11对应芯片到的逻辑表达式为

S12对应芯片到的逻辑表达式为

3.2 测试流程

系统的整体检测流程图见图3。

图3 系统检测流程图

检测步骤如下:

第一步,把待测芯片插入底座,检测其VCC、GND引脚是否连通。采取在待测芯片的GND引脚接继电器的方案:对于14引脚DIP封装的74/54系列逻辑门芯片,引脚7为GND引脚,继电器的常闭端2号引脚分别与主控芯片的P2.4引脚和待检测芯片的7号引脚连接,其中单片机P2.4引脚接下拉电阻;VCC引脚始终与5V电源相连。装置开始工作时,首先检测单片机P2.4引脚的输入电平,若为高电平,则说明待测芯片的VCC引脚和GND引脚连通,说明该待测芯片损坏,此时单片机控制L2亮;若为低电平,则说明两引脚未连通,单片机P2.5引脚控制继电器工作使7号引脚与GND相连,进行下一步检测。

第二步,通过按键选择待测芯片类型,S1—S12分别代表2×4输入与门、2×4输入或门、2×4输入与非门、2×4输入或非门、2×4输入异或门、4×2输入与门、4×2输入或门、4×2输入与非门、4×2输入或非门、4×2输入异或门、1×1非门、2×1非门、3×1非门芯片,其余按键用于拓展。芯片的14号引脚接电源,1—6和8—13号引脚分别接单片机P0.0—P0.7和P2.0—P2.3引脚。

第三步,根据选好的待测芯片类型,设置好单片机对应的引脚输入输出状态,调用相应的逻辑功能表/真值表对待测芯片进行功能检测。

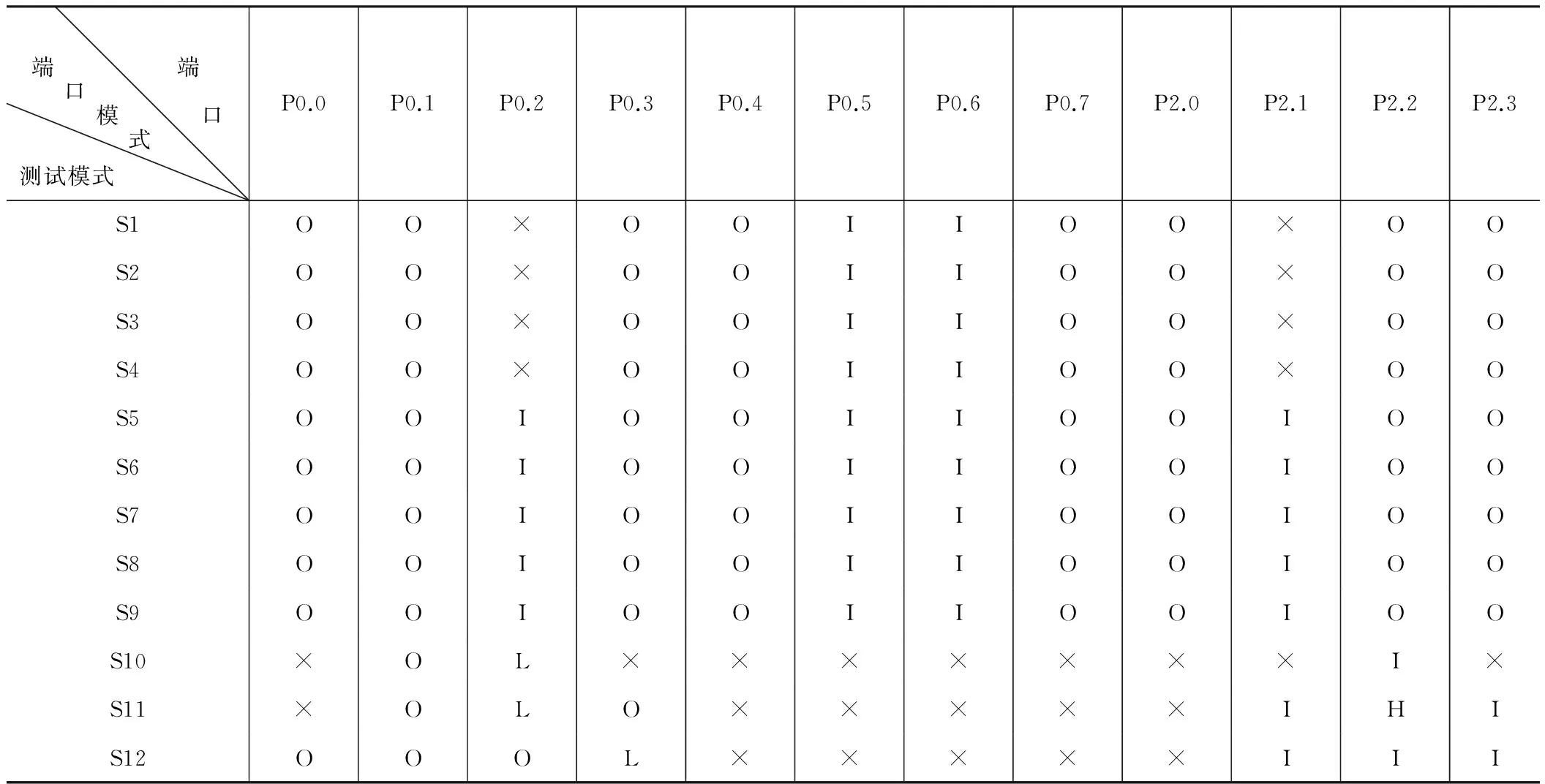

单片机的P0.0—P07、P2.0—P2.3对应与测试芯片模式之间的关系见表1。

表1 单片机P0.0—P0.7、P2.0—P2.3对应测试芯片测试模式的关系

表1中各种测试模式代表待测芯片的类型,根据前述的待测芯片功能分析,控制器(单片机)将逻辑门芯片输入端相连的IO口依次输出所有电平组合作为待测芯片的输入,每次输出电平组合变化前,延时1 ms并检测和逻辑门芯片输出端口相连的IO口的输入电平是否与芯片真值表对应。如果对应,则继续进行电平变化;否则说明待测芯片损坏,停止检测。结果显示部分显示芯片损坏,L2亮;直至遍历完成芯片的真值表且输出结果均与输入信号相匹配时,表明待测芯片没有损坏,结果显示待测部分显示待测芯片正常,L1亮。

4 结语

以常用逻辑门芯片完好性检测为目的的简易检测设备的设计,通过自动化的数字检测手段,极大地简化了实验室和实验过程中对于常用逻辑门芯片完好性检测的过程。针对高校实验室存在的零散门电路芯片多、芯片整理工作量大的问题,可提高实验指导教师、管理维护者对芯片分拣、检测的效率与准确率,以便将更多的精力投入到教学和教学研究中。同时,激发学生对课程学习的兴趣,加深对理论知识的理解,培养学生动手积极性,提高理论与实验课程的教学效果。

References)

[1] 刘艳,李源,江冰,等.数字电子技术课程教具的研究与设计[J]. 实验技术与管理,2016,33(6):210-212.

[2] 王毅.民国时期电化教具创新研究的启示[J].中国教育学刊,2015(增刊1):393-394.

[3] 严世胜,钟承尧,王列峰.新型模拟电子技术实验装置的研制[J].海南师范大学学报(自然科学版),2012,25(3):283-285.

[4] 赵巧妮.便携式简易数字电路实验板的设计[J].科技广场,2016(4):46-48.

[5] 全晓丽,周南权.基于虚拟仪器技术的数字电路实验系统研究[J].实验技术与管理,2014,31(4):96-98.

[6] 陈飞,王友仁,崔江.基于电流信息的CMOS SRAM存储单元故障测试[J].传感器与微系统,2008(6):100-103.

[7] 葛青,葛良全.数字电路测试实验系统设计探讨[J].中国电力教育,2014(14):166-167.

[8] 张江印.高校单片机教学模式的研究[J].实验室研究与探索,2011,30(9):103-106.

[9] 朱金秀,范新南,朱昌平,等.电气信息类人才实践创新能力培养体系[J].实验室研究与探索,2011,30(10):129-131.

[10] 郭天祥.新概念51单片机C语言教程[M].北京:电子工业出版社,2009.

[11] 康华光.电子技术基础数字部分[M].6版.北京:高等教育出版社,2013.

Research and design of testing device for common logic gate chip

Liu Yan, Tang Haixian, Jing Hao, Zhang Bin, Gao Qian

(College of Internet of Things Engineering, Hohai University, Changzhou 213022, China)

Combined with Jiangsu University brand-specialty construction engineering project, the reform in the Digital Circuit course is carried out. Aiming at the 74/54 series logic gate chip commonly used in the digital circuit, the testing device for a common logic gate chip based on the minimum system of the single-chip microcomputer is researched and designed. The device provides that this fast, direct and stable testing method for the related theory and practical teaching of electronic technology can improve the efficiency and accuracy of the laboratory chip testing, and at the same time enhances the teaching effect of the theory and experimental courses.

digital circuit; logic gate; chip testing; practical teaching

10.16791/j.cnki.sjg.2017.01.022

2016-07-17

江苏高校品牌专业建设工程一期项目(PPZY2015B141);河海大学高等教育科学研究2015年度立项课题“翻转课堂模式下的电类课程实践教学模式研究与实践”(20151212)

刘艳(1984—),女,重庆江津,硕士,实验师,研究方向为电子技术、信息获取与处理.

E-mail:liuyan_s@163.com

TP211.5; G642.0

A

1002-4956(2017)1-0094-04