高性能宽带中频信号处理方法研究

董 志,巴俊皓,黄芝平, 刘纯武

(国防科技大学 机电工程与自动化学院,长沙 410073)

高性能宽带中频信号处理方法研究

董 志,巴俊皓,黄芝平, 刘纯武

(国防科技大学 机电工程与自动化学院,长沙 410073)

高速模数转换器的采样速度达到了GSPS(每秒109次)量级,带宽和量化精度的提升对电路的工作条件提出了更高的要求;分析了高速采样中制约无杂散动态范围的因素,并从实践的角度提出了改善的方案,设计了一套双通道通用中频信号处理硬件平台;测试结果说明系统功能正常,达到了140 MHz或70 MHz中心频率信号输入时无杂散动态范围80 dB的性能指标。

高性能; 宽带; 中频信号

0 引言

通信技术中,中频(intermediate frequency, IF)信号是指外差式接收机经过混频器下变频得到的信号[1]。这种结构能够有效的降低处理电路的要求。广义的中频信号也可以指信号的频率范围,一般泛指通信系统中中频信号所用的频率范围。一般中频信号能够使用电路的集总参数进行分析,频率通常小于500 MHz。

测量带宽是仪器非常关键的一个指标。例如对于频谱仪来说,通过提高实时测量带宽,可以减少扫频点数并加快测量速度。提高实时带宽也能提高整体仪器的分析带宽,实现对宽带信号的测量。对于示波器来说,测量带宽反应了示波器对高速信号的检测能力。

目前国内对宽带中频结构的仪器研究还很有限,频谱仪的实时带宽在20 MHz以下[2]。对于宽带信号采集的研究仅限于VXI或者PXI模块,所能达到实时带宽和性能也比较有限[3]。这也是研究宽带中频信号处理平台的出发点。

1 系统结构设计

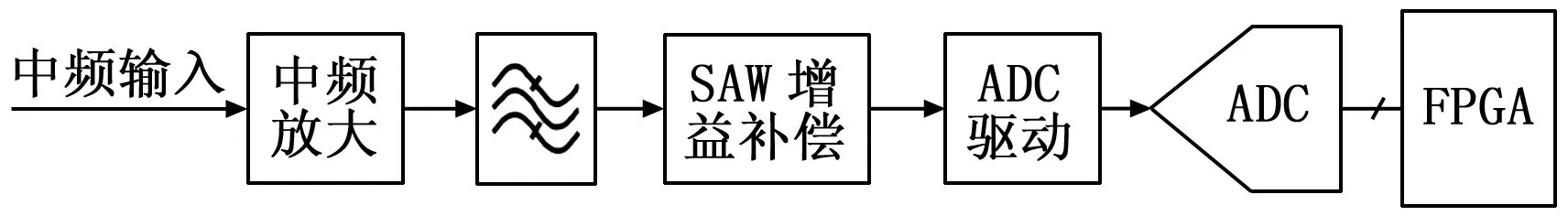

宽带的中频信号处理平台可以借鉴软件无线电的结构。软件无线电要求对天线接收到的信号进行直接采样,在数字域完成信号的滤波、分析。由于器件的限制,ADC器件目前还无法完成对射频信号进行直接的采样。目前软件无线电平台的通用方法是将天线接收到的微波信号进行混频之后,转换为中频信号后完成放大、滤波等信号调理环节再进行采样。最后经过数字信号处理芯片完成对数字信号处理,其基本结构如图1所示[4]。

图1 中频信号处理平台的结构图

高性能有两层含义:一方面是指的系统信号质量高,信号调理与采集部分性能指标高;第二方面指的系统的数字信号处理能力强。数字信号处理算法所能实现的性能指标与采样信号的质量直接相关,一旦在采样的过程中失真或者引入太多噪声,会给数字信号处理算法带来很大难度。因此提高采样信号的质量是提高实现高性能的关键所在[5]。

2 信号处理平台的动态范围

增益受控动态范围是指考虑仪器不同量程增益时的线性动态范围。通常对于不同量程,系统有不同放大倍数,为了保证仪器最佳地与信号进行匹配,通常使用增益控制技术对信号进行放大或衰减。增益控制包括自动增益控制、手动增益控制、数字增益控制等手段。但是注意到对于存在多种信号时候,大信号小信号的增益需求往往难以同时满足,面对这种情景,必须引入无杂散动态范围。

2.1 模拟调理电路的无杂散动态范围

模拟调理电路中,主要引起杂散信号的是放大器,考虑放大器的输入三阶交调分量:

(1)

其中:PIM,out表示输入端IM3分量的功率。带入输入输出关系:

(2)

考虑到理论噪声底限值为F=-174 dBm+NF+10 lgB,使得杂散分量消失的输入功率最大值为:

(3)

考虑到信号处理所需的最小信噪比SNRmin。

Pin,min=F+SNRmin

(4)

那么可以求得其无杂散动态范围:

(5)

2.2 ADC的无杂散动态范围

ADC的SFDR是指的输入模拟信号对其引起转换结果中杂散成分的差值。直接反应了ADC转换的线性度。ADC的噪声底限主要由时钟、输入信号带宽以及ADC自身的杂散信号能量确定。由于最小量化电压的确定,ADC通常在输入信号接近满量程时达到最大的无杂散动态范围。为了使总体的无杂散动态范围最大,必须将输入信号放大至接近ADC的满量程。

此时ADC本身的无杂散动态范围可以表示为:

SFDR≈SFDRADC-SNRmin

(6)

其中:SFDRADC为ADC手册中所确定的无杂散动态范围。

结合两者一起考虑,若信号的输入幅值超出ADC的量程,会导致输入截止,产生大量谐波,这种情况的具体SFDR不多做讨论。若输入信号小于等于ADC的最大输入范围。其SFDR可以表示为:

(7)

其中:ΔP为输入信号功率与ADC达到最大无杂散动态范围的输入功率的差值。

3 多级信号调理电路的动态范围与噪声分析

实际的系统由很多元件组成。如果得到了级联系统总的IP3和噪声系数,可以由式(7)得到系统的动态范围。假设每一级系统的三阶交调截点和噪声系数是已知的,下面分析系统的级联IP3和级联噪声系数。

3.1 系统的级联IP3

假设二级级联系统中,系统的两级是非线性的,这两级的输入—输出特性分别为:

y1(t)≈a1x(t)+a2x(t)2+a3x(t)3

y2(t)≈β1y1(t)+β2y1(t)2+β3y1(t)3

(8)

此时可以得到:

y2(t)=β1[α1x(t)+α2x2(t)+α3x3(t)]+

β2[α1x(t)+α2x2(t)+α3x3(t)]2+

β3[α1x(t)+α2x2(t)+α3x3(t)]3

(9)

若只考虑输出的一阶和三阶项,有:

y2(t)≈α1β1x(t) + (α3β1+ 2α1α2β2+ α13β3)x(t)3+ …

(10)

那么其级联IP3点可以写成:

(11)

将上式平方取倒数后可得:

(12)

其中:AIP3,1和AIP3,2分别表示第一级和第二级的三阶交调点。从上面的结果可知,随着α1的增加,总的IP3将减小,这点不难看出。如果第一级有较大增益,第二级产生的交调产物会更大。

在系统级联中,如果存在窄带器件,例如带通滤波器,那么单音信号的谐波将落于带外,系统的谐波将被极大地衰减,上式中第三项可以被忽略,因而:

(13)

假如第一级的增益大于1,那么级联系统的三阶交调点主要由第二级决定。如果每一级都有大于1的增益,那么后一级的线性度就越发重要。这个结论可以很容易的推广到三级或更多级的系统当中,得到:

(14)

3.2 系统的级联噪声系数

和IP3一样,总的噪声系数可以由每一级的噪声系数和增益得到。考虑如图2所示的两级级联系统,假设阻抗的电抗部分为0。第一级的输入噪声总功率[6]为:

(15)

图2 两级级联系统的噪声分析原理图

第二级的总输入噪声功率为:

(16)

因此总的噪声系数为:

(17)

带入第二级的输出噪声总功率,带入输入总噪声可得:

(18)

假如RS=Rin1=Rout1=Rin2,则可化简为:

(19)

当这个等式不满足时,假如定义功率增益AP为输出功率与源功率之比。

二级系统的源功率为:

(20)

此时的输出功率为:

(21)

所以功率增益为:

(22)

当第二级的源阻抗为Rout1时的噪声系数为:

(23)

系统的总噪声系数可以写作:

(24)

从上面的式子可以看出,在前一级增益增加时,后面各级贡献的噪声贡献的噪声减小了,在系统中,第一级放大器的噪声系数对系统影响最大。对于系统中的衰减元件,如果在其后使用低噪声放大器作适当增益补偿,可以避免其对噪声系数的影响。

4 高性能中频信号处理平台的总体设计

对于140MHz中心频率的信号,选取采样速率为200MSPS,信号落于第二奈奎斯特区;对于70MHz和15MHz中心频率的信号来说,信号落于第一奈奎斯特区。

4.1 带通滤波器

滤波在带通采样中是必不可少的环节。信号的中心频率和带宽决定滤波器的中心频率和带宽,对于不同的信号,需使用不同滤波器。为了达到足够的带外抑制以及矩型系数,通常使用表面声波滤波器(SurfaceAcousticWaveFilter,SAWFilter)进行带通滤波。SAW滤波器具有高矩形度、高带外抑制的特点。插入损耗是使用SAW滤波器必须考虑的一个问题,SAW滤波器的插入损耗通常达到10~20dB。由于SAW滤波器材料的非线性,在通带频率3倍的位置存在假通带的现象范围;同时由于寄生电容以及寄生电感参数的存在随着输入频率的增高其带阻性能逐渐下降,图3为一SAW滤波器的宽带频率响应。可以看出,在3倍通带频率的位置,其带外抑制性能会降为-20dB,对于更高的频率,其衰减性能会慢慢下降。[7]

图3 SAW滤波器的宽带频率响应

由于电调式滤波器的阻带抑制不如SAW滤波器,同时电调滤波器所能实现的带宽和中心频率均有限制。因此考虑使用SAW滤波器进行设计。采用模块化模拟前端的设计方案,这种方案的结构如图4所示,通过将整个模拟前端设计成模块的形式,能够针对通带信号优化调理电路,能够有较好的性能。由于将整个模拟前端独立出来了,减少了因为设计不当而进行迭代设计的成本。

图4 模块化模拟前端的系统框图

4.2 调理电路设计

对于输入的中频信号来说,其输入功率为-20dBm~-60dBm,输入阻抗为50Ω。假设输入信号是正弦波,其对应最大幅值的有效值可以由下式计算。

(25)

同样的方法可以得到最小幅值VRMS(min)=0.000 223 6V。对于AD9467器件来说,其输入范围一般为2.5V或2.0V。为了保证ADC的最大信噪比,输入的信号必须与ADC的输入范围相匹配。因此,必须引入放大电路。

ADC输入的峰峰值为2.5V,阻抗为530//3.5pF,对于输入信号的中心频率140MHz,其对应输入阻抗为:

144.7-236.1i

(26)

满量程对应的功率为:

0.011 2W= 10.5dBm

(27)

假设信号的输入功率为-20dBm,假如为了使其放大至满量程,其对应增益为30dB,考虑到SAW滤波器的插入损耗,使用放大器实现的增益至少为50dB。

由于中频信号频率的中心频率为70MHz或140MHz,运算放大器的放大倍数收带宽增益积限制,很难在此频率下保持高增益。使用专用RF/IF放大器能更简单的完成对中频信号的放大。[8]

为了提高系统的动态范围,调理电路需要引入数控增益放大器(digitalgain-controlamplifier,DGA)来调节整体增益,适应不同输入功率的信号,DGA的原理一般有两种:1)通过固定增益低噪声放大器与衰减器的串联,这种结构能够保持DGA在高增益下的噪声系数同时保持良好的OIP3特性;2)通过控制晶体管偏压调节增益,这种结构的DGA的噪声系数不如第一种优秀。

为了尽可能的提高系统总体的动态范围,尽可能地选择高OIP3指标和低噪声系数的DGA。ADL5201具有高IP3,低噪声系数的特点,因此选用3级ADL5201作为放大器,所能达到的总增益为60dB,如图5所示。

图5 优化后的调理电路结构

8562XX系列SAW滤波器是SAWTEK公司生产的一系列宽带中频信号滤波器,它的矩形系数几乎为1,阻带抑制为50dB,插入损耗达到了-20dB。

4.3 高速ADC的抗混叠滤波器设计

高速ADC的一个关键设计要点是抗混叠滤波器的设计,尤其是对于采样带宽与信号带宽相近时。信号的杂散分量会落入采样带宽内造成混叠,影响进一步的数字信号处理。对于高速ADC而言,其抗混叠滤波器还起到阻抗匹配的作用,其抗混叠滤波器的设计直接影响到最后的采样的动态性能。

系统选用AD公司的AD9467模数转换器,对于系统需要针对的中心频率140MHz带宽72MHz的中频信号而言,采用200MSPS采样频率进行采样。对于AD9467来说,其输入级采用缓冲结构,能够提供相对恒定的高输入阻抗。这也意味着对于宽带应用,最好考虑带缓冲结构的ADC。对于开关电容型ADC的实现简单,成本较低,但是开关电容ADC的采样保持器的阻抗连续变动的,很难在宽带应用中进行阻抗匹配。

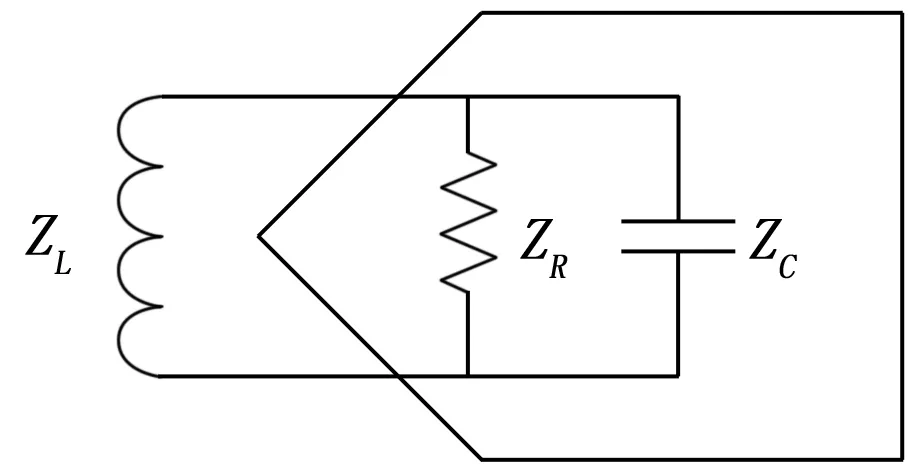

对于窄带应用,AD9467依然可以使用开关电容ADC常用的谐振匹配的方法进行抗混叠滤波器的设计,即通过在ADC输入口并联电感以消除ADC输入阻抗中的寄生电容成分。这种设计在带宽小于30MHz的情况下能实现较好的性能。谐振匹配的原理图如图6所示,感性负载ZL[9]的计算如式(28)。

图6 谐振匹配的原理图

(28)

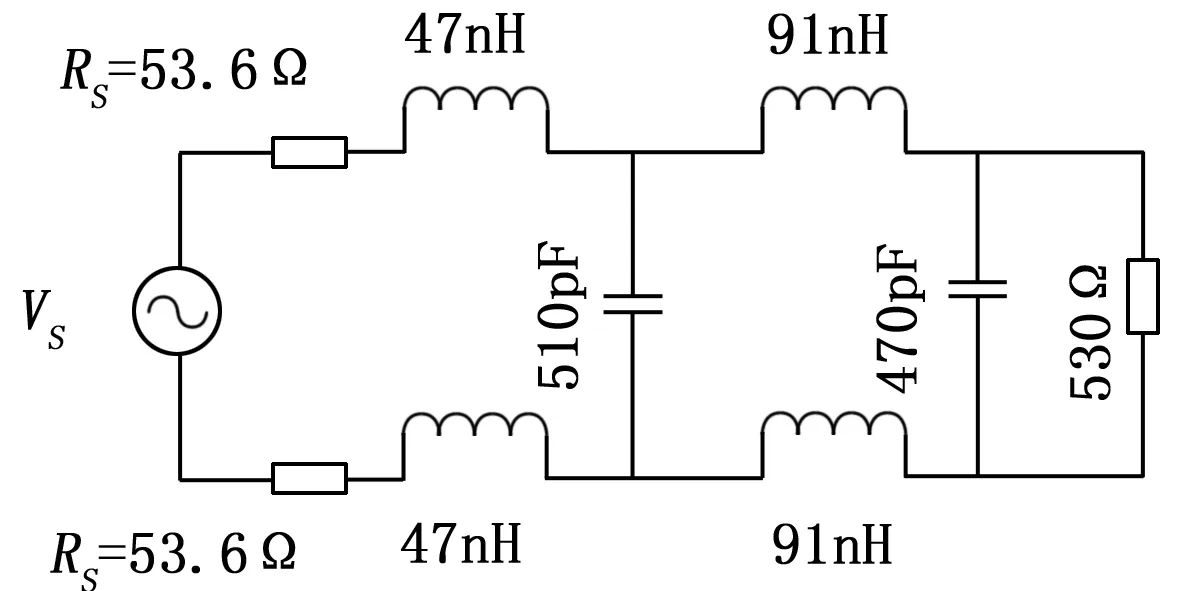

对于抗混叠滤波器而言,由于实际元件参数的限制以及印制电路板寄生参数的限制,很难保证高阶滤波器的通带纹波和阻带衰减,同时带来失真。一般采用4-6阶巴特沃兹滤波器进行设计。从设计手册上查找四阶归一化滤波器,如图7所示。该滤波器满足切比雪夫不等式,在负载阻抗比为5:1时,纹波小于0.5dB[10]。

图7 四阶归一化滤波器

首先将阻抗等效为530Ω,截止频率定为180MHz(140MHz+32MHz=172MHz)。那么有:

计算结果如图8所示,最后将单端滤波器网络改为差分网络,并带入标准值,最终的滤波器设计值如图9所示。

图8 修改参数后滤波器原理图

图9 修改为差分输入后的四阶滤波器

5 系统性能测试与结果分析

5.1 测试平台

整个系统测试方案由信号源、电源、中频信号处理平台以及计算机组成,如图10所示。

图10 中频信号处理平台的测试原理图

对于16Bit的ADC来说,其SFDR参数一般大于80dBFS[11],对信号源提出了较高的频谱纯净度指标需求。频谱纯净度中的非谐波失真参数表示信号源输出中除了信号以及其谐波之外的杂散信号。目前只有少数高端信号源能够满足需求,非谐波失真小于80Bc的产品,本方案选用R&S的SMHU射频信号发生器,此信号发生器具有极佳的频谱纯净度,当信号频率小于250MHz时,其非谐波失真达到-100dBc。

FPGA通过片内FIFO将数据封装成IP数据包,使用8kB巨型帧进行传输。计算机使用Wireshark进行抓包,缓存容量设为4GB,按固定包数进行抓取。使用频谱分析软件或者MATLAB数据进行分析,如图11所示。

图11 由Wireshark软件抓取的数据包

5.2 系统性能测试结果

5.2.1 单音测试结果

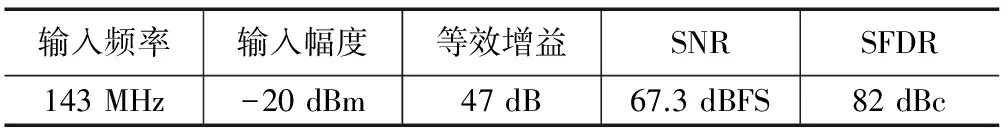

单音测试主要测试系统的信噪比以及无杂散动态范围。由于调理电路中滤波器的存在,输入的信号可以近似看做纯单音信号,无需额外添加滤波器。单音测试频率选择180MHz,输入频率选择76MHz(图12)和143MHz(图13),结果如表1和表2所示。

图12 76 MHz输入 180 MHz采样时钟的测试频谱

图13 143 MHz输入 180 MHz采样时钟的测试频谱

本条件下AD9467的标称信噪比为75.9dBFS,标称SFDR为98dBc,由于放大器的引入以及时钟对信噪比的限制,测得的SNR与SFDR参数有所下降,如表1所示。

表1 76 MHz输入 180 MHz采样时钟的测试结果

本条件下AD9467的标称信噪比为76dBFS,标称SFDR为98dBc,与标称值相差很大。SNR的差距主要来自于采样时钟抖动对整体SNR的恶化。另外,标称SFDR的采样频率为250MHz,从数据手册上可以看出AD9467在采样频率为180MHz输入91MHz的条件下无杂散动态范围的理论值为86dBc,如表2所示。与标称值相比主要差距为PipelineADC的校准频率不匹配导致。

表2 76 MHz输入 180 MHz采样时钟的测试结果

5.2.2 单音扫频测试结果

为了得到单音信号在整个带宽上的性能,可以采用扫频的方法进行测试。将SMHU信号源的工作方式设置为扫频,对采集的信号进行分段之后进行分析。

分别以70MHz和140MHz输入信号为例进行SFDR性能的测试。为了更好的控制扫频的频率,采取计算机通过仪器总线IEEE488进行频率的控制,整体的测试流程如图14所示。SFDR与频率曲线图测试结果如图15和图16所示。

图14 扫频测试的流程图

图15 70 MHz输入的SFDR扫频测试结果

图16 140 MHz输入的SFDR扫频测试结果

6 结论

通过测试结果可以发现Pipeline型ADC由于总带宽的限制导致SFDR指标并不完全稳定,尤其是与采样频率成整数倍数关系时,谐波分量的能量叠加导致SFDR指标下降,同时影响通带平坦度。中频信号处理平台的性能指标在140 MHz或70 MHz下能够达到无杂散动态范围大于80 dBc的性能指标,能够满足提出的性能指标。

[1] 杨小牛, 楼财义, 徐建良. 软件无线电技术与应用 [M]. 北京:北京理工大学出版社, 2010.

[2] 陈 丁, 王 放, 张 军, 等.基于 AWG 超宽带雷达信号测试系统的实现 [J]. 雷达科学与技术, 2015, 13(3): 279-83.

[3] Xuan Y L, Sheng S Y, Xiao G Q, et al. High-speed data acquisition system based on PXIe bus[J]. Journal of Mechanical & Electrical Engineering, 2015, 32(1).

[4] Li D, Yang Y T, Shi Z C, et al. A low-distortion multi-bit sigma-delta AD C with mismatch-shaping DACs for WLAN applications [J]. Microelectronics Journal, 2015, 46(1): 52-58.

[5] Razavi B. RF microelectronics [J]. Prentice Hall Communications Engineering & Emerging Technologies, 1998,

[6] Friis H T. Noise figures of radio receivers[J]. Proceedings of the IRE, 1944, 32(7): 419-422.

[7] Campbell C, Ye Y. Wide-band linear phase SAW filter design using slanted transducer fingers [J]. IEEE Transactions on Sonics and Ultrasonics, 1982, 29(4): 224-228.

[8] Wang P, Liu K, Li M Q. Design and simulation of new zero-IF receiving circuit[A]. Proceedings of the Advanced Materials Research, F, [C]. Trans Tech Publ. 2012.

[9] Law K, Cheng K, Yeung Y B. Design and analysis of switched-capacitor-based step-up resonant converters [J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2005, 52(5): 943-948.

[10] 森荣二. LC 滤波器设计与制作 [M]. 薛培鼎,译.北京:科学出版社, 2006.

[11] Kester W. Taking the mystery out of the Infamous Formula "SNR= 6.02 N+ 1.76 dB" and Why You Should Care [J]. Analog Devices, MT-001, 2005.

Study of High Performance Signal Processing Platform for Wideband Intermediate Frequency Signal

Dong Zhi, Ba Junhao, Huang Zhiping, Liu Chunwu

(Mechatronitics and Automation School, National University of Defense Technology, Changsha 410073, China)

the sample rate of modern ADC goes to GSPS (Giga Samples per Second), the high input bandwidth and precise working condition makes it difficult to achieve specified performance. Analyzed the limit of spurious free dynamic range and discussed the improving methods of SFDR achieved. Designed an IF signal process platform, the results show that the system achieved all functions and system requirement, and achieved 80 dBc for SFDR when the central frequency is 140 MHz or 70 MHz.

high performance; wideband; intermediate frequency signal

2016-05-25;

2016-07-14。

国家自然科学基金(61374008)。

董 志(1979-),男,辽宁葫芦岛市人,讲师,博士,主要从事网电空间测控方向的研究。

1671-4598(2016)12-0172-05

10.16526/j.cnki.11-4762/tp.2016.12.049

TN914.4

A