基于DSP+FPGA的导航制导一体化计算机设计

郑 帅,张 晞,孙昌军

(北京航空航天大学 仪器科学与光电工程学院,北京 100191)

基于DSP+FPGA的导航制导一体化计算机设计

郑 帅,张 晞,孙昌军

(北京航空航天大学 仪器科学与光电工程学院,北京 100191)

对于目前小型化导弹的发展趋势,文章设计了一种以DSP为核心算法处理芯片,FPGA为外围输入输出接口,可实现MEMS惯性导航与惯性、半主动激光制导,可进行PWM输出控制舵机的一体化计算机;文章对硬件设计给出了总体和分模块的详细描述,给出了软件设计的流程框图;设计实现了导航功能与制导功能的系统一体化与结构小型化,输入输出接口丰富;经过试验调试验证了其技术可行性。

DSP;FPGA;导航制导控制一体化

0 引言

导航、制导与控制技术是研究各类运动体的核心问题[1]。对于导弹的控制而言,从导弹发射到最终击中目标,一般采用初、中段制导加末制导的体制,即在导引头捕获目标之前,通过初、中段制导将导弹送到目标附近,使目标进入导引头的视场,之后末制导阶段,导弹根据导引头给出的视线偏差飞向目标。在这个过程中需要通过导航技术来获取自身载体的位置、速度和姿态信息,通过制导技术来得到目标相对弹体位置信息和通过控制技术来操纵导弹的执行机构使其在期望的弹道飞行。

在近、现代战争中,微、小型导弹由于其成本低、附带毁伤小、体积和重量小等优点,其发展逐渐受到各国重视。对于微小型导弹控制系统,相对于传统弹载计算机,其设计的小型化和一体化尤为重要。小型化设计是需要满足弹上的尺寸要求,一体化设计指在一个计算机上同时完成对导航、制导信息的采集与计算和对导弹执行机构的控制的功能。

DSP系统在进行数字信号的计算上有很大优势[2],其具有小型化、运算速度高、运算精度高及稳定性好等优点,目前已经在导航计算机中得到广泛应用。本设计采用DSP+FPGA的设计方案,利用FPGA强大的逻辑功能进行与外界的通讯和数据的采集,扩展DSP的接口,DSP进行后续的导航与控制算法[3]。

1 系统设计

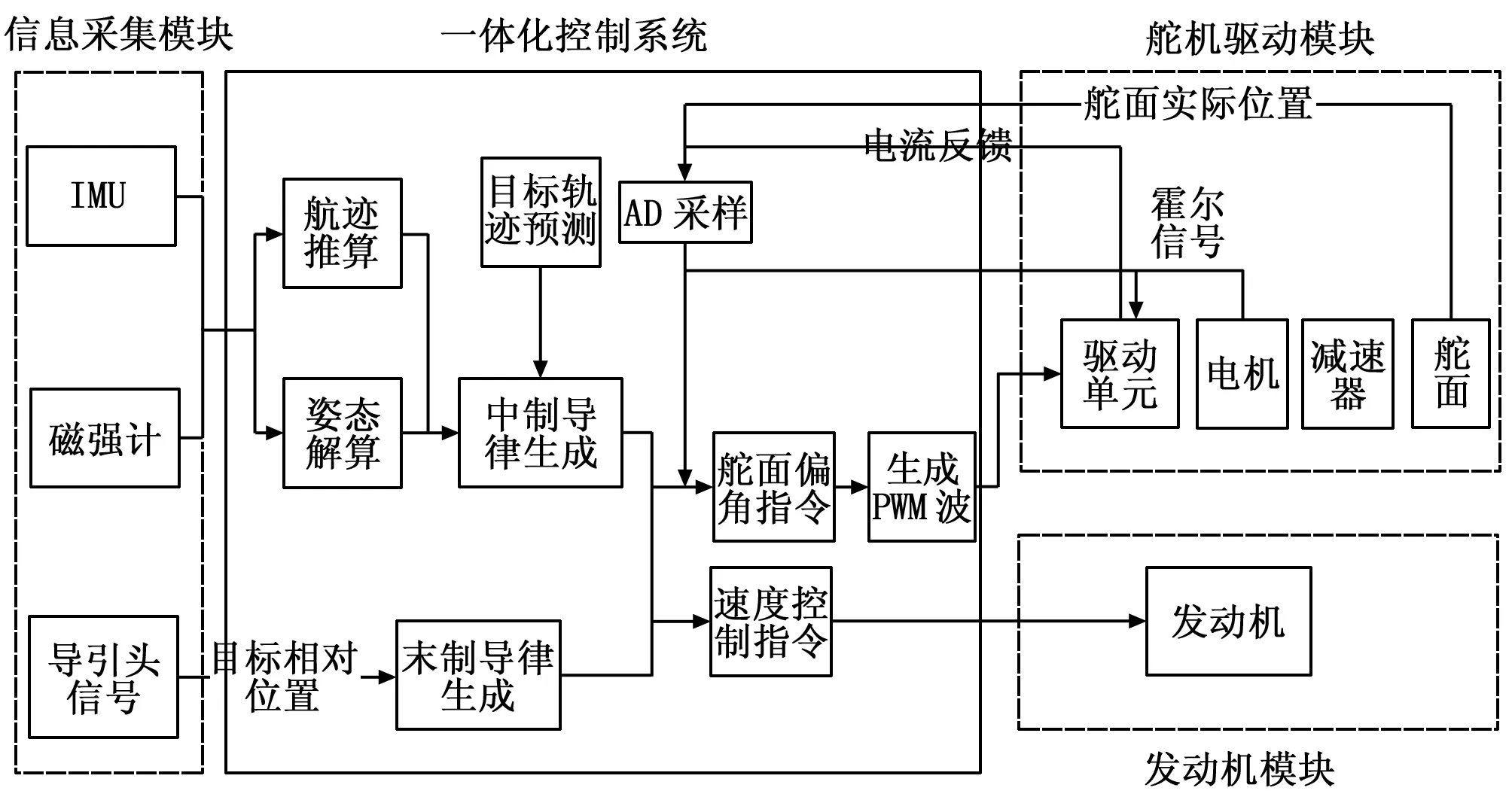

根据系统功能需求,一体化控制器导航板部分设计采用军品级DSP芯片为核心,扩展相应外围电路,使其应满足系统高速闭环控制需求。总体结构如图1所示。

图1 系统设计框图

系统总体结构主要由前段信息采集系统,中段控制与计算系统和末段的执行机构组成。系统设计的特点是中段的系统进行了一体化的设计,增强了集成性,减小了计算冗余,更加适用于小型化设计。

2 硬件设计

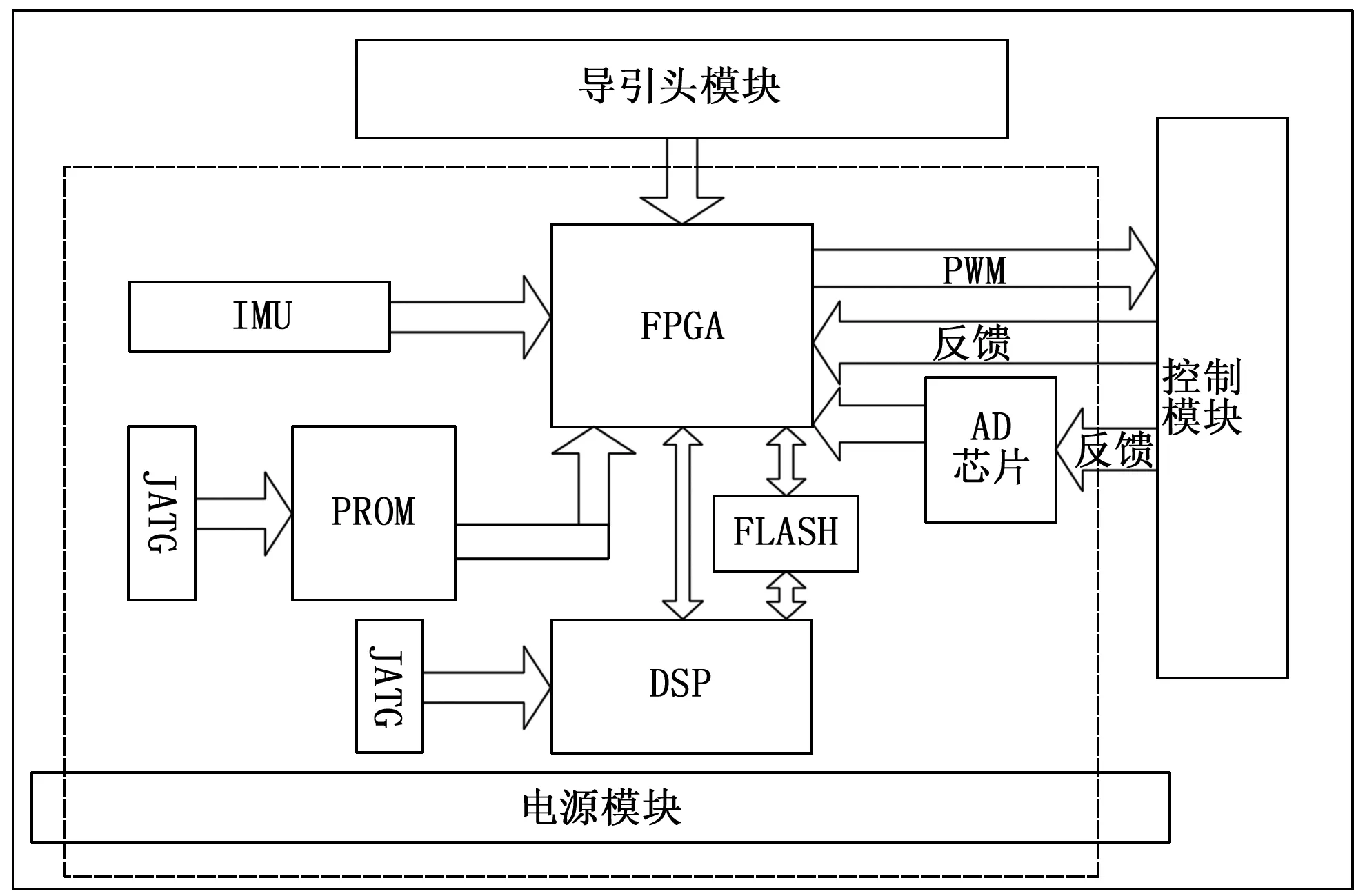

一体化计算机硬件电路设计包括主控模块,导航信息采集模块和舵机控制接口模块。硬件结构如图2所示。

1)IMU通过SPI接口向FPGA传输信号,SPI作为一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便。

2)计算机接口功能完全由FPGA实现,并在其内部进行缓存。FPGA主要实现对传感器的初始化配置,数据读写时序控制,数据预处理等功能。

3)DSP模块实现对传感器信息的处理功能,便于以后对组合导航算法的研究。

4)通过AD芯片采集舵机舵面的位置反馈和电流反馈[4]。

图2 硬件设计框图

2.1 主控模块设计

本设计中DSP芯片选用TI公司的TMS320C6727芯片,FPGA芯片选用Xilinx公司的Spanrtan-6系列xC6SLX16-2CSG225。6727是一款32/64位的浮点运算DSP,主频300 MHz,片上集成256 KB的RAM和384 KB的ROM,可以满足本设计需求。

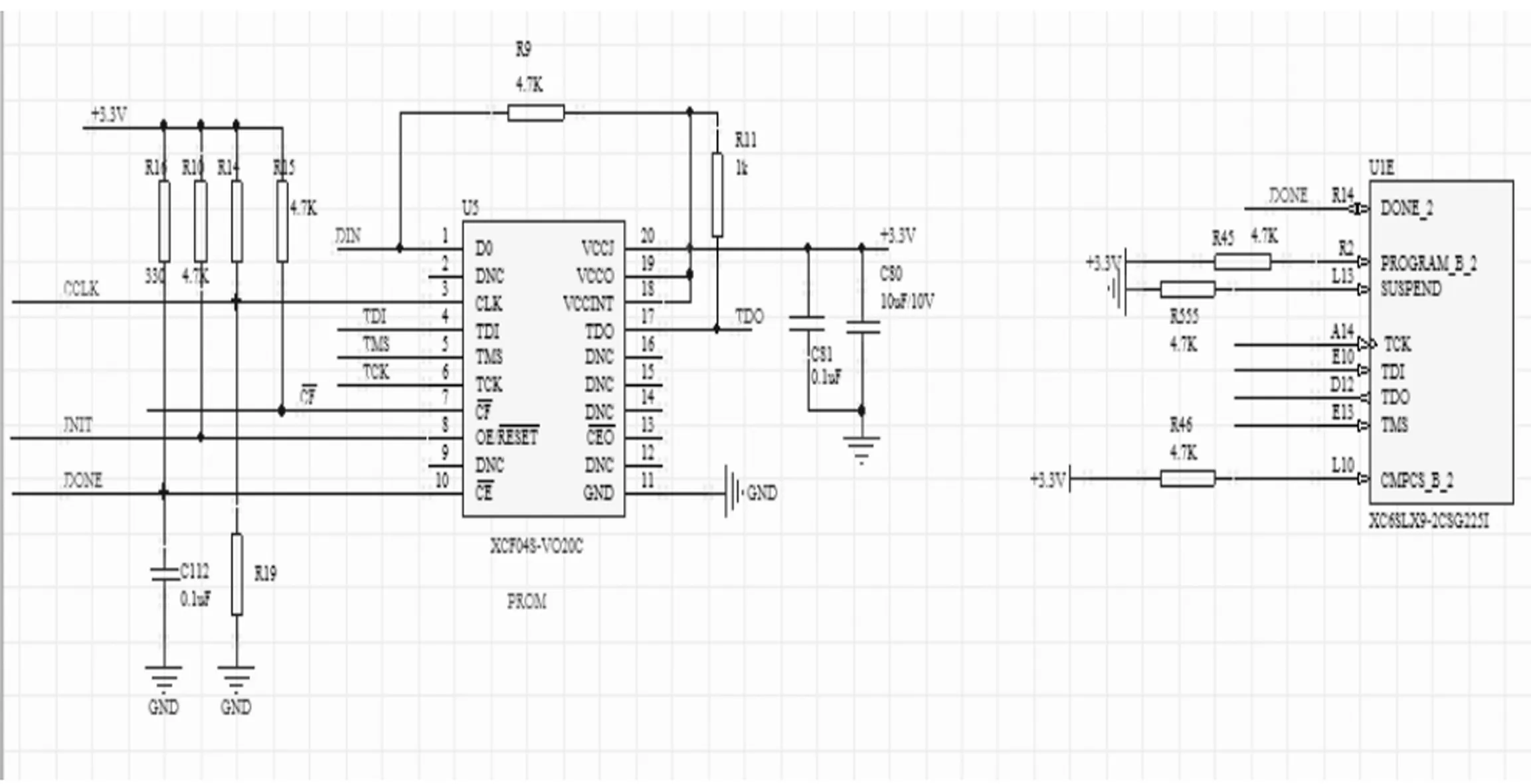

2.1.1 FPGA配置模式

由于FPGA掉电后编程信息立即丢失,芯片在每次上电时,都必须重新下载设计文件所生成的配置数据。目前,配置FPGA的方式有多种,可以通过JTAG接口配置(一般在调试过程),可以通过PROM、FLASH来配置,也可以通过CPU或者CPLD进行配置。本设计中采用最常用的主动串行模式对FPGA进行配置,配置模式引脚设置为M[1:0],PROM选用Xilinx公司的XCF04S-VO20C。配置原理如图3所示。

图3 PROM配置原理图

DIN为串行数据输入信号,用来串行接收来自PROM的配置数据。此模式下CCLK为配置时钟信号,是由FPGA提供给PROM器件的驱动时钟,电路板上CCLK信号走线尽可能短且外部连接少。INIT_B为芯片初始化指示信号,低有效,在配置开始阶段,清空PROM地址计数器,如果在配置中检测到CRC错误,会将其拉低。DONE为FPGA配置状态指示信号,在配置中使能PROM,配置完成后,关闭PROM。PROG_B为重配置FPGA信号,低有效。

2.1.2 DSP配置电路

2.1.3 FPGA与DSP通信

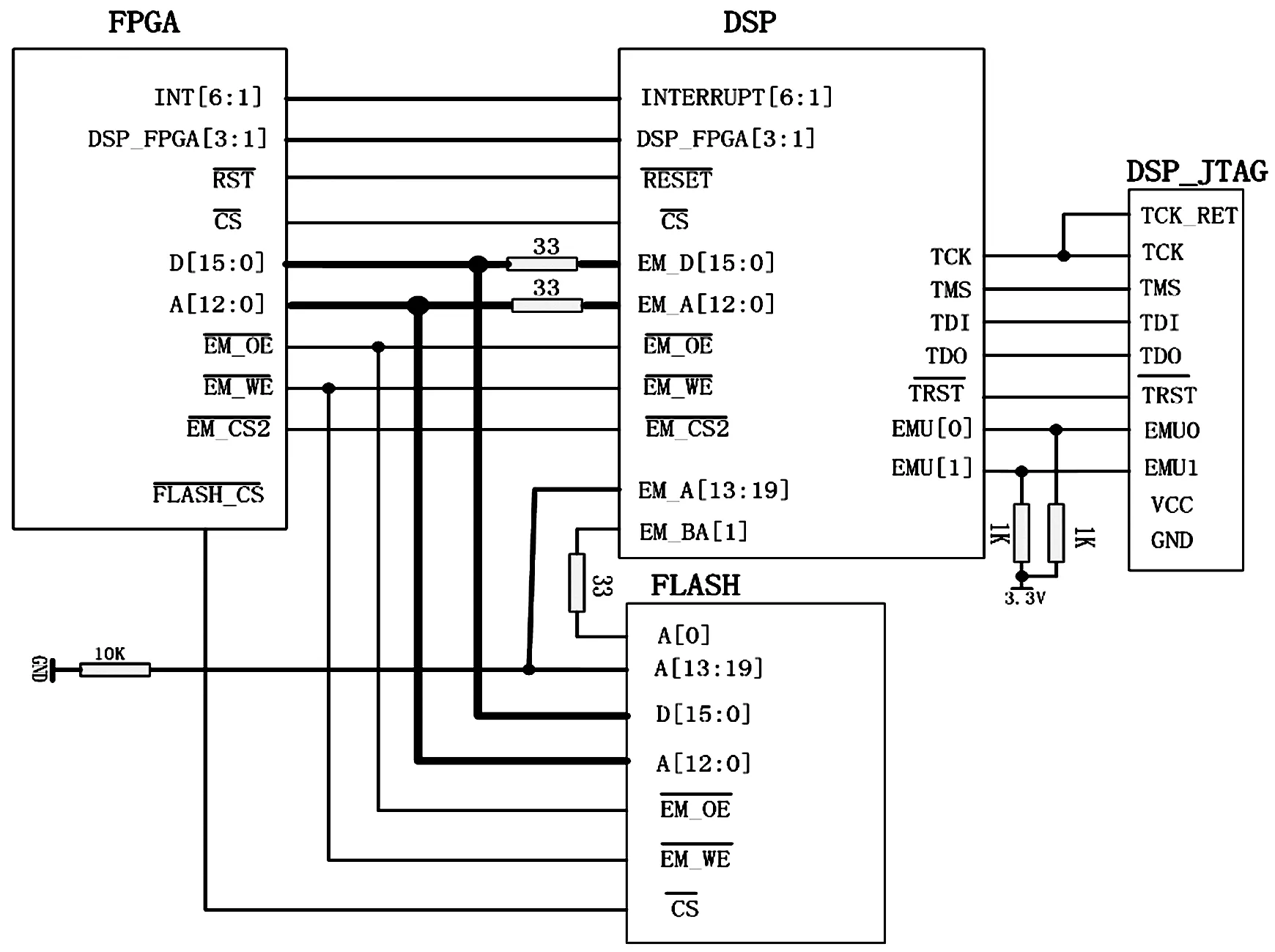

在FPGA与DSP的通信中需要FPGA利用内部的RAM中构建存储器,把FPGA设计为DSP的一个外部存储器,FPGA将采集的数据存放到构建的存储器中,DSP通过EMIF接口读取数据,从而实现了DSP与FPGA的并行通信。连接方式如图4所示。

图4 FPGA与DSP通信连接图

2.2 导航信息采集模块设计

由于单一的制导模式不能满足导弹的的需求,因此本设计采用惯性加激光制导的设计方式。为满足小型化和一体化的设计要求,惯性测量元件选用AD公司的MEMS产品ADIS16445,内置一个三轴数字陀螺仪和三轴数字加速度计。激光导引头采用捷连式半主动激光导引头。ADIS16445通过SPI接口和FPGA进行通信。连接方式如图5所示。

图5 IMU与FPGA连接图

SPI是一种高速、全双工、同步的串行通讯,它可以同时发送和接受串行数据,可以当作主机或从机工作,可提供频率可编程时钟、发送结束中断标志、写冲突保护、总线竞争保护等。ADIS16445的SPI工作模式为SP3,CPOL=1(极性),CPHA=1(相位)。与激光导引头的通信方式为全双工422串行接口,字长11 bit(8 bit数据位,1 bit起始位,1 bit校验位,1 bit停止位),波特率为115 200 bps。

2.3 舵机控制接口模块设计

图6 AD芯片配置方式

霍尔信号为数字信号,需要通过2 k的电阻拉高到5 V。通过FPGA采集时,需要将其转换为3.3 V,本设计选用TI公司的74LVC4245A电平转换芯片。

对每一个舵机采用4路PWM信号进行控制,从FPGA输出经电平转换芯片拉高到5 V后输出。

2.4 电源设计

电路板的电源设计需要满足板上不同组件的不同电源需求,AD7891芯片为单5 V供电,SN74LVC4245电平转换芯片需要3.3 V和5 V供电,DSP芯片需要3.3 V和1.4 V供电。

FPGA由3个要配置元素:可配置逻辑块(CLB),I/O块(IOB)以及其相互连接部分,其中CLB提供功能型逻辑元素,IOB提供封装引脚和内部信号之间的接口,可编程相互连接资源提供布线途径以连接CLB和IOB的输入和输出至合适的网络。施加于CLB的电压称为VCCINT,VCCO为IOB的供电电压,VCCAUX为辅助电压输入,为有严格时间要求的资源供电。因此,Spartan-6系列FPGA有VCCO、VCCINT、VCCAUX三种供电电压。

根据Spartan-6的芯片手册,对于速率级别为-2L的XC6SLX16-2CSG225I,VCCINT的典型值为1.2 V。VCCAUX的典型值为2.5 V和3.3 V,考虑到DSP同样需要3.3 V的电压输入,所以选择3.3 V作为VCCAUX的供电电压。对于VCCO,手册中的推荐电压范围为1.1至3.45 V,因此同样选择3.3 V作为供电电压,这就减少了稳压芯片的数量,降低了成本。

由于电路板和驱动板进行集成,电路板采用5 V供电,通过稳压芯片分别获得3.3 V、1.2 V和1.4 V的电压。稳压芯片采用TI公司的TPS73701和TPS73733各两片,其为线性低压差稳压器,输入电压范围为2.2~5.5 V,输出电压在1.2 V和5.5 V之间可调,具有0.5%的初始精度,同时具有体积小、发热少等优点。

3 软件设计

控制软件程序流程如图7所示。

图7 软件流程框图

程序主要分为发射前和发射后两个部分。发射前主要通过IMU进行初始姿态的装订。发射后程序主要为舵机控制程序和制导程序两个闭环控制。基本流程是通过IMU采集陀螺仪和加速度计的数据进行导航解算,得到当前时刻导弹的位置和姿态等导航信息,将这个信息和当前时刻预定的轨道信息进行比对,得到偏差量,此偏差量采用比例导引律计算,得到舵面应偏转的角度。在末制导阶段,导引头捕捉到目标后,可得到目标相对于弹体坐标系的俯仰和偏航角,此时关闭IMU数据通道,只采用半主动激光导引。控制舵面偏转生成PWM波的程序流程如图8所示[5-6]:

图8 PWM生成程序流程图

4 结束语

本文详细介绍了一种基于DSP+FPGA的导航制导一体化系统设计,该系统在通信接口、计算、控制等方面采用了可靠的设计,通过了实验调试,可实现预期技术功能。

[1] 王寒梅, 杨 博. 弹用 GNC 一体化的研究[A].2007 系统仿真技术及其应用学术会议论文集[C]. 2007.

[2] 高 敏, 任海龙, 杨 芳, 等.基于 DSP+FPGA 的弹载计算机设计[J].计算机测量与控制,2014,22(12):3995-3997.

[3] 邸小坤, 朱圣英, 徐 瑞. 基于 DSP 和 FPGA 的航天器一体化导航信息采集系统设计[A]. 中国宇航学会深空探测技术专业委员会第十届学术年会论文集[C]. 2013.

[4] 李赛辉, 雷金奎. 基于 DSP 的数字舵机控制系统的设计与实现[J]. 计算机测量与控制, 2009 (3): 484-486.

[5] 于增坤. 基于 FPGA 的电动舵机伺服控制系统研究[D]. 太原:中北大学, 2015.

[6] 高同跃, 龚振邦, 罗 均, 等. 一种超小型无人机舵机控制系统的设计[J]. 计算机测量与控制, 2007, 15(8): 1006-1007.

Design of Integrative GNC Computer Based on DSP+FPGA

Zheng Shuai, Zhang Xi, Sun Changjun

(School of Instrument Science and Opto-electronics Engineering, Beihang University, Beijing 100191,China)

With the development of miniature missile, this article designed a integrative computer based on DSP processor as algorithm operating chip and a FPGA as peripheral interface for input/output, which can achieve strap-down inertial guidance based on MEMS and semi active laser guidance.It can also control electro mechanical actuator by PWM; this article gives an explicit description of hardware in collectivity and in modules and software flow chart; this design realize a integrative and small system for navigation, guidance and control. It has plentiful interface and it was testified that the system is applicable.

DSP; FPGA; integrative GNC

2016-06-17;

2016-07-20。

郑 帅(1991-),男,陕西西安人,硕士研究生,主要从事导航制导一体化方向的研究。

1671-4598(2016)12-0100-03

10.16526/j.cnki.11-4762/tp.2016.12.028

TJ765

A