1200 V IGBT的性能优化

李宏

(上海先进半导体制造股份有限公司,上海 200233)

1200 V IGBT的性能优化

李宏

(上海先进半导体制造股份有限公司,上海 200233)

主要研究1200 V IGBT器件的性能优化方法。理论分析了IGBT结构参数与其主要性能的关系,按1200 V IGBT器件击穿电压和饱和压降的设计要求,重点讨论了FS、JFET注入、延长JFET退火时间和减小Pring注入剂量对IGBT器件击穿电压(BV)和饱和压降(Vdson)的影响,最终得到了满足器件设计要求的最佳性能参数。

IGBT;FS-IGBT;JFET注入;JFET退火;Pring注入;击穿电压;饱和压降

1 引言

上世纪80年代初,试图把MOS与BJT技术集成起来的研究导致称为绝缘栅双极晶体管(IGBT)的新型功率器件的发明。作为新型电力半导体器件的主要代表,IGBT被广泛用于工业、信息、新能源、医学、交通、军事和航空领域。随着半导体材料和加工工艺的不断进步,IGBT的电流密度、耐压和频率不断得到提升。目前,市场上的IGBT器件的耐压高达6500 V,单管芯电流高达200 A,频率达到300 kHz。在高频大功率领域,目前还没有任何一个器件可以代替它。本文着重分析讨论1200 V IGBT器件的性能优化。

2 IGBT结构和设计理念

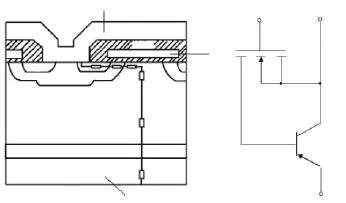

IGBT是一个复合器件,由一个MOSFET和一个PNP管组成,如图1。

IGBT集MOSFET的栅极电压控制特性和BJT的低导通电阻于一体,具有电压控制、输入阻抗大、驱动功率小、导通电阻小、开关损耗低及工作频率高等特点,并具有类似MOSFET的宽SOA(安全工作区)特性,是近乎理想的半导体大功率开关器件。然而对于IGBT的设计目前还是一个难点。为了减小器件开通的功率损耗以及开关损耗,希望器件的通态压降越小越好;同时为了兼顾高压器件的耐用性,希望IGBT的击穿电压尽可能高。击穿电压与导通电阻两者的矛盾要求IGBT各个结构参数做尽可能的最优化设计。

图1 IGBT结构图以及等效电路图

2.1IGBT击穿电压

击穿电压又称为反向阻断电压,当IGBT工作在反向阻断状态时,希望器件的漏电流越小越好。1200V IGBT的设计要求击穿电压1200 V以上,实际应用还必须考虑一定的余量,所以耐压一般要求在1250 V左右。影响击穿电压的主要因素有:

(1)漂移区的电阻(Rd);

(2)漂移区厚度;

(3)终端设计;

漂移区的电阻率越大,击穿电压越大;漂移区越厚,击穿电压越大。

2.2通态压降

通态压降(Vdson)又称为饱和压降(Vcesat),主要由图1中的电阻构成:

Vdson的大小决定着器件的耗散功率。对高压IGBT而言,主要影响Vdson的电阻是Rj和Rd,即JFET区域的电阻和N-漂移区内的电阻。因此,如何尽量降低Rj和Rd是大功率IGBT设计中应重点考虑的。

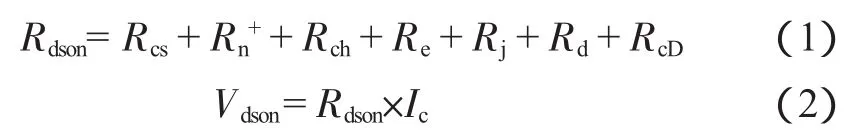

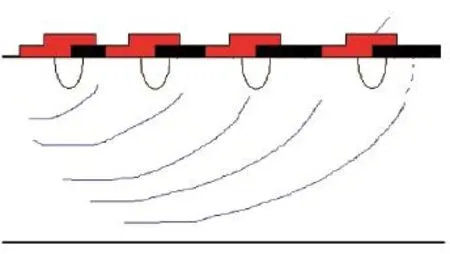

2.3终端设计

终端设计对IGBT的击穿电压有着决定性的作用,当前国内设计多采用的是多级浮空P-轻掺杂场限环与场板相结合的技术,见图2。

图2 IGBT终端结构平面图及截面示意图

3 1200 V IGBT性能优化

3.1基础工艺制造的IGBT性能

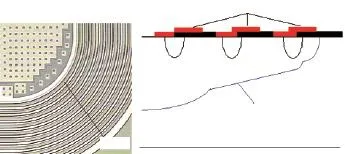

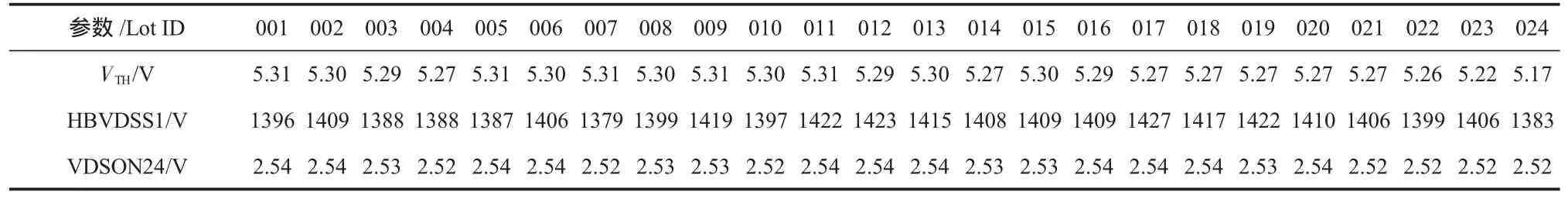

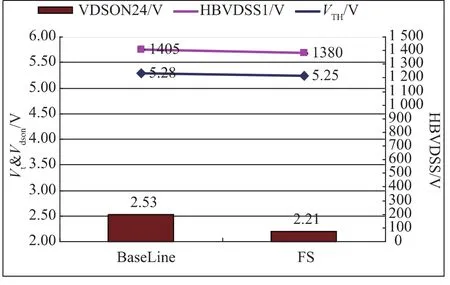

电阻率为65 Ω·cm的衬底,采用基础工艺制造的1200 V IGBT,其部分静态参数见图3。

图3 基础工艺下IGBT的静态参数

在当前条件下,击穿电压(HBVDSS,以后简称BV)、饱和压降(以后简称Vdson)以及开启电压(以后简称Vt)分别可以做到1405 V、2.53 V和5.28 V。详细数据见表1。

该产品最初主要应用于电磁炉,量产稳定。但是近来,部分客户反馈该产品在应用到高频大功率设备时,经常会出现“过热”现象,有极大的安全隐患。这就局限了产品的应用范围,只可以“屈就”低频领域。客户迫切希望自己的产品能够涵盖多领域,不再“短腿”。

3.2性能优化

客户反馈的“过热”现象一般都发生在设备工作期间,也就是IGBT导通状态下,功耗偏大。跟据公式PD=Vdson×IC,在工作电流IC稳定的前提下,由于Vdson偏高而造成了功耗偏大。解决“过热”即为降低Vdson。降低Vdson的方法很多,但是都会影响到BV,所以改动时要找到两者的平衡点。

表1 基础工艺下IGBT的静态参数平均值

3.2.1FS IGBT

FS IGBT为场终止IGBT,是在图1中的P和N-中加一层N+层,以此改变器件的纵向电场分布,使其可以在漂移区 (N-区)变薄的条件下,Vdson降低而BV几乎没有太大的影响,如图4所示。

图4 FS IGBT结构图及对应的纵向电场分布图

由于N+层的介入,使器件的厚度大大减薄。FS IGBT采用外延衬底——硅+浓薄外延层一+淡厚外延层二。加工时所有步骤都与基础工艺相同,只是将硅片减薄得更多,硅片的最终厚度比基础工艺薄了将近55 μm,Vdson大大降低,而BV以及Vt则在可接受范围内,如图5。

图5 FS与基础工艺关键参数的比较

FS IGBT经过客户评估使用,基本达到预期要求,无论低频高频器件。但是由于FS比基础工艺减薄得更多,在减薄以及随后的注入、蒸发、退火等工艺过程中接连出现了碎片,碎片率超过8%,若要解决,就需要更大的设备投入,投入与收入不成比例,因此FS虽然能解决客户的困扰,但是当前并不可行。

3.2.2JFET注入&退火时间优化

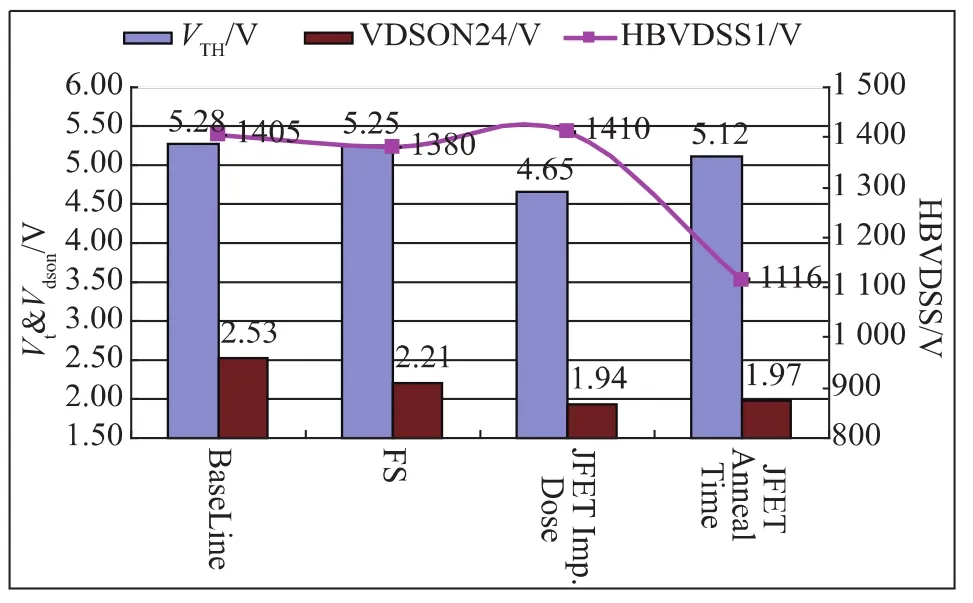

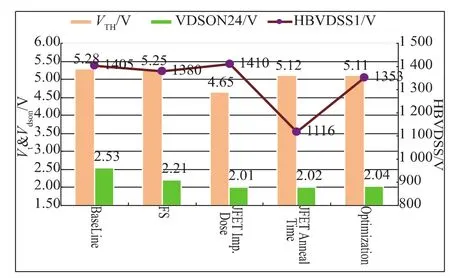

降低Vdson除了降低Rd外,还可以通过降低Rj来实现。降低Rj的方法主要有两个:增大JFET注入剂量或是延长JFET退火时间。通过这两种方法,都极大地降低了Vdson,甚至还优于FS工艺。见图6。

图6 Vt、Vdson、BV在4种条件下的对比

虽然Vdson都得到了极大的改善,但是单一化改进都造成了其他参数的失效:增大JFET注入剂量,符合了部分硼,改变了P-body的杂质分布,Vt变小;延长JFET退火时间,Vt也略有降低,仍在可接受范围内;BV大大降低,却在意料之外。对失效片进行目检,没有发现任何烧毁点,这就说明管芯仍旧可以正常工作,只是工作的耐压降低——击穿的尖峰电场仍旧发生在最外Ring环端;由于JFET退火时间加长,P环同时向左右以及下方扩散,各环之间的间距变小,P环的空间电荷区也随之向下以及左右扩散,作用于每个P环的尖峰电场的位置发生偏移,造成耐压降低。图7所示是未延长退火时间前的耐压原理图。每一个环按照设计时的要求承受固定的耐压,经过最后一个环,耐压达到了1300 V左右。

延长JFET退火时间,P环变宽变大,设计时计算好的环间距变小,各个Ring环承受的最大电压的位置由于势垒变大而发生偏移,如图8所示,最终导致最大耐压值变小。

根据图7、图8的理论,降低P-注入剂量,再延长JFET退火时间,可以调节P环的扩散宽度以及深度,从而在不影响P环间距的前提下,达到降低Vdson的目的,同时对Vt的影响微乎其微。经过拉偏实验,最终发现P-的注入剂量在降低到原来的七分之一时,再延长JFET退火时间,各个参数可以有效地建立平衡,如图9。

图7 未延长JFET退火时间前的耐压原理示意图

图8 延长JFET退火时间后的耐压原理示意图

图9 最终优化与基础工艺以及各个改动之间的参数对比

4 优化效果

优化后,Vdson达到了预期要求,Vt变动不大,虽然BV下降较多,但是对于1250 V的使用下限也高出了100 V左右,客户对此表示接受。优化后的产品经过使用评估,完全达到使用要求,应用趋于多元化,客户非常满意,基础工艺现已统一优化。根据此优化方案,采用现有的制程,在提高衬底电阻率的前提下,可以扩展衍生到1500 V甚至1700 V IGBT的制造优化上,形成一个稳定的IGBT工艺制造平台,提高生产效率。

5 结论

本文先在理论基础上分析了IGBT的结构和设计理念,并给出了基础工艺制造的1200 V IGBT的主要参数值。根据设计理念对基础工艺关键参数进行优化,得到了最平衡的制造方案,并将之量化成一个稳定的IGBT制造平台。

[1]关旭东.硅集成电路工艺基础 [M].北京:北京大学出版社,2003:349.

[2]施敏.现代半导体器件物理[M].北京:科学出版社,2001: 428.

[3]Michael Quirk.半导体制造技术[M].北京:电子工业出版社,2009:600.

[4]刘恩科.半导体物理学[M].北京:电子工业出版社,2008: 433.

[5]孟庆巨.半导体器件物理 [M].北京:科学出版社,2005: 310.

[6]维杰斯拉夫·本达.功率半导体器件——理论及应用[M].北京:化学工业出版社,2005:357.

[7]袁寿财.IGBT场效应半导体功率器件导论 [M].北京:科学出版社,2007:209.

[8]陈星弼.功率MOSFET与高压集成电路[M].南京:东南大学出版社,1990:373.

[9]Liu Chao.Comparative Study of MOSFET and IGBT[J]. Computer&Digital Engineering,2013,41(11):1772-1773.

[10]Stanley Wolf.Silicon Processing For The VLSI Era Vol 4 [M].USA:Lattice Press,2002:805.

An Optimization Method of 1200 V IGBT

LI Hong

(Advanced Semiconductor Manufacturing Corporation Limited,Shanghai 200233,China)

An optimization method of 1200 V IGBT is presented in this article.The relationship between the structure and performance of IGBT is analyzed.The influence of FS-IGBT,JFET implant,JFET anneal prolonging and Pring implant decreasing on the balance of breakdown voltage and saturation voltage is studied for better IGBT performance.

IGBT;FS-IGBT;JFET implant;JFET anneal;Pring implant;breakdown voltage;saturation voltage

TN305.3

A

1681-1070(2016)11-0044-04

2016-5-26

李宏(1978—),男,山东日照人,复旦大学在读工程硕士,先后在中国电子科技集团公司第47研究所和上海新进半导体制造公司任职,目前在上海先进半导体工艺整合部门工作。