基于ARM和FPGA高速1553B总线测试系统的设计

张玉福,刘鹏,王晓曼

(长春理工大学 电子信息工程学院,长春 130022)

基于ARM和FPGA高速1553B总线测试系统的设计

张玉福,刘鹏,王晓曼

(长春理工大学 电子信息工程学院,长春 130022)

鉴于传统的1553B总线设备传输速率低、接口单一化等不能满足实际应用需求的问题,利用Zynq-7000芯片设计一套基于嵌入式ARM控制器和FPGA的高速1553B总线测试系统。采用自顶向下的设计方法,对ARM(PS部分)、FPGA(PL部分)分别进行设计。PS部分采取USB和以太网双接口完成跟PC机的数据通信;设计IP核实现符合1553B总线协议的编解码处理功能。通过Xilinx自带仿真工具ISE Simulator对各个模式下消息传输进行时序仿真,表明系统提高了1553B总线接口传输速度,使得总线设备与PC机通信更加方便满足实际应用。

1553B总线;Zynq-7000;IP核;嵌入式

1553B(MIL-STD-1553B)总线是一种时分制命令/响应型串行多路复用的航空数据总线标准[1],鉴于其优异的性能被广泛应用在各种武器装备上。随着我国航空、航天、坦克以及舰船等技术的发展,1553B总线需要传输大量的数据,对其传输数据速率要求及高,而且数据结构更加复杂,1Mbp/s的总线带宽已达不到航空、航天及地面装甲车辆系统中数据的高速传输、大容量存储等基本要求。现在市场上可用的芯片多从国外进口,价格高昂,而国内生产的性能相对落后。本文应用Zynq-7000芯片设计基于嵌入式ARM控制器和FPGA的1553B总线测试系统,提高了1553B总线的传输速度,满足系统对1553B总线高速应用的需求。

1 1553B总线测试系统的硬件设计

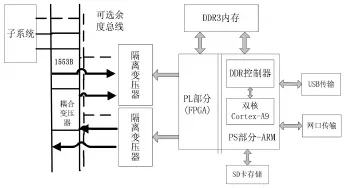

1553B总线包括三种终端类型:总线控制器(BC)、远端终端(RT)、总线监控器(BM),1553B总线接口的构造必须能够具备向双绞线发送消息、接收消息、信息处理以及传输数据给子系统的全部功能,即完成子系统与1553B数据总线的通信接口功能[2]。在接口设计上,ARM通过USB或以太网跟PC机通讯,设计IP核实现符合1553B总线协议的处理和编解码功能,提高总线接口的传输速率。

图1 系统总体方案设计框图

1.1 Zynq-7000 SoPC芯片

以Zynq-7000可扩展处理平台作为整个实时处理系统的核心,包括ARM(PS)、FPGA(PL)两部分。其中PS部分集成了最高可运行在1GHz的双核ARM Cortex-A9;PL部分包含了传统意义的FPGA逻辑单元,能够灵活地用于各种目标应用[3]。

ARM处理器内核有两个Cortex-A9处理器子系统,每个处理器包含独立的32KICASH和DCASH,运行速率高达800MHz,二者间共享有512K的L2 CASH。两个子系统工作模式可分为对称和非对称两种,也可以选择只用一个或者在它们之间建立调度关系,采用传统的ARM调试方法对处理器调试[4]。该芯片具备100-Gbps的峰值带宽,可以使ARM处理器和FPGA架构的硬件加速器高效的共享资源数据。PL部分有3000多个内部连接,利用其丰富的扩展能力扩展子系统,将FPGA紧密地与ARM的处理单元相结合,实现了无缝连接。

1.1.1 FPGA(PL部分)IP核

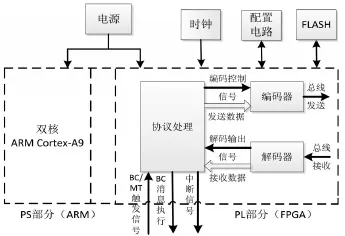

FPGA处理部分如图2所示,编解码部分主要实现FPGA内部的TTL信号与双极性曼彻斯特码之间的转换,协议处理实现命令字的分析,1553B总线接口的核心控制单元是数据的正确读写与发送等基本通讯功能,可被配置成BC、RT或BM控制器存储收发数据[6]。

图2 FPGA处理部分结构框图

本系统设计的重点和难点是利用Zynq-7000芯片的PL部分如何设计1553B总线的IP核协议。用FPGA(PL)部分实现总线协议的编码、解码的功能,具体过程:设计IP核构建协议处理器,解析1553B总线上传输的曼彻斯特码得到16位并行数据、各种校验信息等,通过内部的AXI总线输出至ARM接口,然后通过USB口或网口跟PC机完成上行通讯;上位机传送消息到ARM接口,再由FPGA协议处理、编码,将16位并行二进制数据转化为符合协议标准的20位消息,从而完成下行通讯。

1.1.2 双核ARM Cortex-A9(PS部分)

双核ARM Cortex-A9主要是用于整个系统的控制管理及跟PC机的通讯。双核ARM Cortex-A9内置USB 2.0全速器件/主机/OTG控制器并带有片上物理层接口(PHY),则不需额外使用专门的USB协议芯片;以太网部分配有功能齐全的10Mbps的MAC,只需配置PHY芯片即可[5]。ARM与FPGA通过内部AXI_HP、AXI_GP、AXI_ACP三种接口实现无缝通信,实现系统控制和数据交换功能;双核ARM Cortex-A9通过外设与上位机连接,根据相应的功能需求,通过控制以太网接口、USB接口完成相应信息的处理、传输和存储。

1.2 隔离变压器和耦合变压器

1553B总线是主从结构,采用的编码格式是曼彻斯特码,最多可以挂载31个终端。总线控制器到远程终端使用双绞屏蔽线传输,假若终端离总线很近(大约小于0.3米),那么终端与总线间就可以通过隔离变压器及串入的隔离电阻相接;反之假若终端离总线比较远则需要插入一个耦合变压器。总线系统与终端之间,无论是直接耦合还是通过变压器耦合,为了解决实现短路保护、直流隔离和阻抗匹配等问题,设计时必须接隔离变压器。

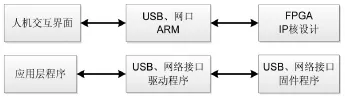

2 系统软件设计

软件设计主要由应用层程序、USB和网络接口的驱动程序移植等构成。各部分关系如图3所示:

图3 系统软件设计总体框图

该系统应用层程序主要由消息接收机、发送、存储等部分组成,是系统软件的主要组成部分。根据相关功能的需求,应用Xilinx公司专用的开发工具搭建开发环境,编写相应的收发、存储、处理等程序,满足用户的要求。

开发USB客户端驱动并编些接口固件程序,基于FPGA的IP核设计时,固件程序是将ARM接口传输过来的16位数据进行协议编码处理,继而输出20位的双极性曼彻斯特码[7],接收和发送数据是互逆的过程。

3 仿真验证

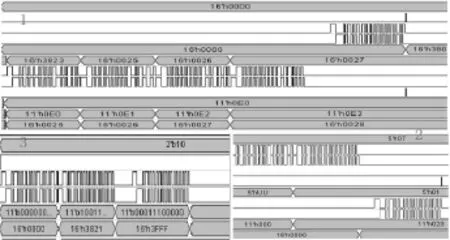

基于FPGA的IP核设计使用了Verilog HDL硬件描述语言,通过Xilinx自带仿真工具ISE Simulator对各个模式下消息传输进行时序仿真。

BC是总线上启动信息传输任务的终端,所数的信息传输都是由BC发出指令,其主要负责总线上数据流的调度,如图4所示1号为BC向RT发出发送指令时的时序仿真;RT是用户子系统跟数据总线间的接口,它在BC的控制下收发数据,通信中RT检测总线上的命令字,2号为RT响应BC接收指令的时序仿真;MT(总线监视器)是被指派接收总线通讯任务并继而提取将要使用信息的终端,它负责监控总线上的信息传输,从而完成数据的记录分析,但是它本身并不参与总线通信过程[8],3号为工作在MT模式下的时序仿真图。

图4 时序仿真

利用JTAG接口下载ARM和FPGA两部分的程序到Zynq-7000芯片中调试硬件[9]。将设计的测试系统和1553B总线信号源对接,进行总线设备之间的收发通讯。BC向RT发送各种不同格式的信息,使用数字示波器来捕获总线上的信号波形,观察总线上的波形验证消息传输的正确性[10]。

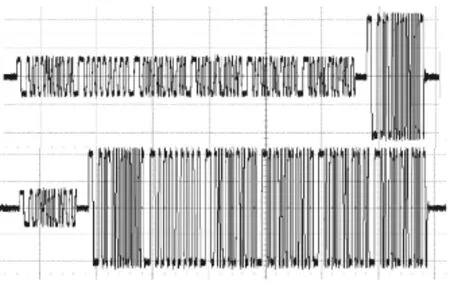

硬件测试时调试好硬件电路,测试设计的系统是否检测到1553B总线设备。ARM处理器启动消息的传输,RT在收到命令字和数据字后返回正确的状态字,数字示波器测得总线上的数据波形如图5上;RT向BC传输数据,数字示波器测得总线上的波形如图5下。

图5 示波器波形图

分析示波器捕捉到的波形,可以看到其频率及波形升降均达到1553B总线的协议标准,从而验证了信息传输的准确性。通过分析波形可以得出结论,硬件测试结果与软件仿真一致且传输速率支持1Mbps和10Mbps两种模式。

4 结论

通过研究1553B总线的协议,设计基于ARM和FPGA的高速1553B总线测试系统,分别从硬件和软件两方面论述本系统,并通过软件和硬件的仿真验证,实现其功能。在跟PC机通讯中,采用USB和网口,解决接口单一问题。另外,本系统体积小,便于携带,应用FPGA设计的IP核,降低了成本,增强了系统的性能,在未来电子设备中发挥了重要的作用。

[1] 国防科学技术工业委员会.GJB289A-97数字式时分制指令/响应型多路传输数据总线[S].中国标准出版社,1998.[2] 虞希清.专用集成电路设计实用教程[M].杭州:浙江大学出版社,2007:13-26.

[3] 代霜,王槐,徐抒岩.1553B总线通讯的可靠性设计[J].光机电信息,2010(9):52-58.

[4] 田耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008.

[5]林丰成,竺红卫,李立.数字集成电路设计与技术[M].北京:科学出版社,2008.

[6] 徐丽清,姬劳,1553B总线接口技术研究及FPGA实现.[D].西安:西北工业大学,2006(3):10-32.

[7] Diao Lifeng,Dai Ming,Lei Jianming.Application of IP Core Technology to the 1553B Bus Data Traffic[C].Conference on Postgraduate Research in Microelectronics and Electronics,IEEE,2010:338-342.

[8] Zhang Yongxiang,Zhang Weigong,Zhou Quan,et al. The Design of 1553B Communication Bus Based ofBU-61580[C].2010the5thIEEE Conference on IndustrialElectronics and Applications,2010: 1920-1923.

[9] Xilinx,Inc.XC18V00 Series In-System-Programmable Configuration PROMS[OL].DS026 January,2008.

[10] Xilinx Inc.DS190,Zynq-7000 Extensible Processing Platform Overview[DB/OL].2012.

Design of High Speed 1553B Bus Test System Based on ARM and FPGA

ZHANG Yufu,LIU Peng,WANG Xiaoman

(School of Electronics and Information Engineering,Changchun University of Science and Technology,Changchun 130022)

In consideration of the problem that the traditional 1553B bus device can not meet the requirements of practical application,such as low transmission rate,single interface and so on.A high speed 1553B bus test system based on embedded ARM controller and FPGA is designed by using Zynq-7000 chip.Using top-down design method,the ARM(PS part)and FPGA(PL part)were designed.The PS part adopts the USB and Ethernet dual interface to complete the data communication with the PC machine.Design the IP core to achieve the 1553B bus protocol coding and decoding processing function.Through the Xilinx comes with simulation tool ISE simulator for each mode message transmission timing simulation,show that the system improves the 1553B bus interface transmission speed,making bus devices and PC communication more convenient to meet the practical application.

1553B bus;Zynq-7000;IP core;embedded

TP332

A

1672-9870(2016)05-0088-03

2016-04-20

张玉福(1990-),男,硕士研究生,E-mail:1451406579@qq.com

王晓曼(1956-),女,教授,E-mail:wmftys@126.com