基于多核DSP互联架构的SAR处理研究与设计

张 强,冯仰松,郭 朋

(中航工业雷华电子技术研究所,江苏 无锡 214063)

基于多核DSP互联架构的SAR处理研究与设计

张强,冯仰松,郭朋

(中航工业雷华电子技术研究所,江苏 无锡 214063)

提出了一种基于多核DSP互联架构的SAR成像处理方案。首先,介绍了一种基于方位子块插值的PFA实时成像算法。其次,研究了TI多核DSP TMS320C6678的处理性能,介绍了一种典型的 RapidIO互联架构,并进一步提出基于该架构的SAR成像处理方案。最后,通过给出SAR成像结果并对比传统解决方案,证明了该处理方案的有效性和先进性。

多核DSP;互联架构;RapidIO;合成孔径雷达;极坐标格式算法

0 引言

合成孔径雷达(SAR)是一种具有全天候、全天时、远距离获取地面信息能力的传感器。SAR具有防区外探测能力,在国境侦察、战场侦察和战场精确打击等应用中发挥着重要的作用,具有极高的军事价值[1]。SAR成像在高分辨率及高测绘带宽的指标需求下,距离方位二维数据量庞大,并且算法复杂,因此对信号处理系统的数据传输和实时处理能力提出了很高的要求。

传统的单核DSP架构限于点对点的连接方式,只能形成固定的拓扑结构,而且单核DSP的处理能力有限,提高系统实时处理能力只能通过多DSP间并行加流水的方式,导致系统规模巨大。系统规模的增加会带来如复杂性高、稳定性差、散热差、重量大等一系列问题,并且随着系统指标要求的提高,这种固定的拓扑架构已经接近极限。多核DSP架构除了提高单个DSP的处理能力,减少系统 DSP数量,还支持 RapidIO等高速串行总线,不仅满足了系统对数据吞吐量的需求,也提供了更灵活高效的互联模式。

1 PFA成像处理算法

在聚束模式合成孔径雷达中,由于天线波束始终指向固定的成像区域,因此产生了雷达相对于目标区域的转动。极坐标格式算法(Polar Format Algorithm,PFA)最早是作为一种有效的旋转目标成像方法提出的,很快该方法就被成功地应用于聚束模式SAR成像中,并且大大地提高了聚束 SAR的聚焦成像范围[2]。

PFA是一种经典的聚束SAR成像算法,该算法采用极坐标格式存储数据,有效地解决了远离成像区中心散射点的越分辨单元走动问题,极大地提高了聚束SAR的有效聚焦成像范围。相比于其他算法,PFA算法具有简单高效、计算量小、实时性好和易于运动补偿等优点,广泛应用于SAR实时成像领域[3-4]。

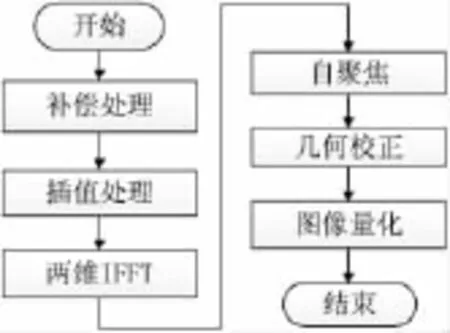

本文采用PFA成像算法,流程如图1所示。

图1 PFA算法流程

上述PFA算法在插值处理时需要存储大量数据,存储容量增加的同时还导致了成像时延变大。基于方位子块插值的 PFA成像算法[5],将所有距离线的集合分割成若干互有重合的子集合,每个子集合作为一个子块,分发到相应的处理器进行插值处理,减少了的存储容量的要求,降低了成像延时。

2 TMS320C6678多核DSP处理模式与性能研究

2.1多核DSP处理模式

TI推出新一代多核 DSP TMS320C6678(C6678),内嵌8个核,核速率最大 1.25 GHz,工业级芯片可达 1 GHz,单核浮点运算能力最高可达20 GFLOP。C6678处理能力提高的同时还具备了更强的IO能力,其中RapidIO最高支持 20 GB/s传输,以太网最高支持 1 GB/s传输。该DSP的内存可分为本地内存(LL2)、共享内存(SL2)和片外内存(DDR)。其中LL2为512 KB,SL2为4 MB,DDR可寻址8 GB空间[6]。

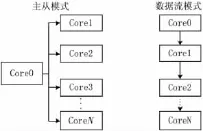

常用的多核处理模式有两种,即主从模式和数据流模式,如图2所示。

图2 多核处理模式

(1)主从模式,即一个核做数据接收和分发,对其他核的处理进行管理,即1+N的工作模式;

(2)数据流模式,即处理按照数据的传输串行执行。

由于多核共享数据带宽,数据流模式仅适用于核间传输数据量较小的情况,而SAR处理数据量较大,因此采用主从模式。

基于C6678的多核主从模式如图3所示。由于缓存(cache)会占用一部分 LL2的存储空间,剩余部分容量较小,所以LL2仅用于存储小数据量的常量;SL2用于保存各个核处理时使用的中间结果;DDR空间较大,可以存储DSP的输入、输出以及数据转角时需要存储的大量数据。

图3 TMS320C6678主从模式

主核首先将接收到的DSP输入数据分配给相应的从核,再根据不同的处理启动从核进行相应的子处理,然后等待所有从核处理完毕,最后汇总从核的输出结果并发送给其他DSP。这种主从模式将DSP的处理与数据传输分离,简化了DSP间的时序关系,提高了系统的稳定性。

2.2多核DSP处理性能研究

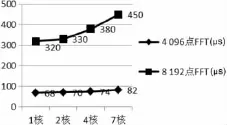

根据上述主从模式,以FFT运算为例,测试C6678多核并行处理性能。如图4所示,随着并行核数的增加,FFT处理时间也有所增加,这是由于多核共享SL2的数据带宽,从核并行处理时会产生竞争,导致DSP并行处理能力下降。因此,多核并行处理能力并不随着参与处理的从核数量的增加而线性增加。

图4 TMS320C6678多核FFT运算测试结果

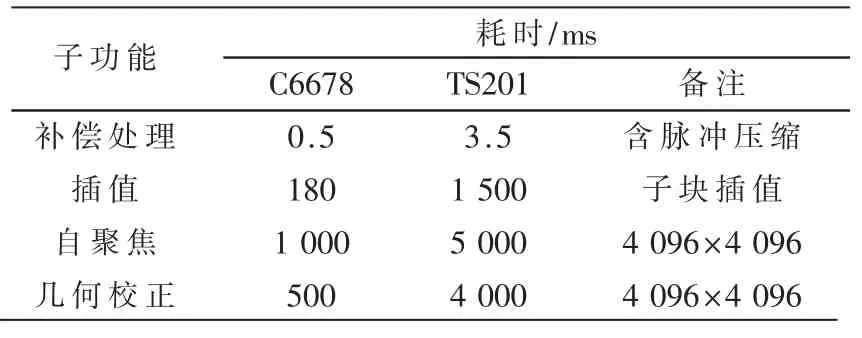

根据PFA成像算法流程,以1+4主从模式(1个主核加4个从核)为例,测试了SAR处理中各子功能多核并行处理性能,并对比单核DSP TS201,结果如表1所示。由于两种处理器的主频、内存总线宽度、优化能力等都不尽相同,并且某些子功能不适于并行处理(如自聚焦迭代过程),C6678与TS201的处理能力并不是简单的4倍关系。

表1 SAR子功能处理时间

2.3维护cache一致性

上文给出的结果,是在DSP使能cache的前提下得出的。对C6678来说,每个核都可以在LL2中开辟cache空间,在使能cache的情况下,每个核对SL2的读写操作都是在cache中进行的,这样极大地提高了内存读写效率。以4 096点FFT运算为例,使能cache的情况下耗时为68μs,非使能cache的情况下则高达600μs。

但是使能 cache会导致 cache一致性问题,cache一致性问题是指在含有多个cache的并行系统中,数据的多个副本因为没有同步更新而造成的不一致问题。这时需要软件来维护 cache一致性,维护 cache一致性的操作分为 cache无效化和 cache回写。例如当核 A需要更新数据给核B时,核A首先要执行cache回写操作,使cache中的数据更新到内存中去,核B在读取核A更新的数据前要执行 cache无效化操作,以保证从 cache读取的数据和内存中一致。除了多核间维护cache一致性外,核与外设(如SRIO、EDMA等)间也要维护cache一致性,因为外设对内存的读写操作是不经过cache的。

3 基于RapidIO互联SAR实时处理系统设计

提高DSP的处理能力只是保证系统实时性的一方面,在典型的嵌入式系统中,瓶颈往往在于系统级互联,即各元件之间的通信速度。RapidIO互联架构消除了该瓶颈,它提供了一种高性能、分组交换的互联技术。目前C6678支持最高20 GB/s的传输速率。

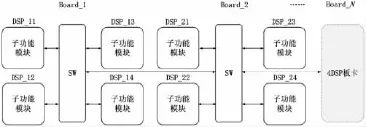

图5所示为一个典型的多核DSP互联架构,板内DSP通过交换设备(SW)互联,板间又通过 SW 互联,从而组成一个RapidIO互联网络。传统的固定拓扑架构由于通信链路单一,使得系统内每个DSP都不可替代。而在这种互联架构中,DSP在系统内的逻辑位置都是等效的,可以方便地实现系统的重构。同时,该互联架构以4DSP板卡为最小单元,可根据系统的需求进行扩展。这种RapidIO互联架构使得软件设计不再受限于固定的拓扑结构,具有很高的重构性和扩展性。

图5 多核DSP互联架构

为了充分利用多核DSP的并行处理性能,每个子功能模块需要尽可能地完成更多功能,这样也减少了子功能模块间即DSP间的数据传输,减少了流水级数,降低了系统的复杂度。

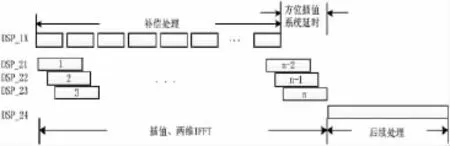

SAR处理时序如图6所示,补偿处理由于实时性要求高,需要4个DSP进行轮转处理,处理结果同样轮转发送到 DSP_21、DSP_22和 DSP_23 3个 DSP进行子块插值和二维 IFFT处理,DSP_21、DSP_22和 DSP_23处理完毕后发送输出结果给 DSP_24,DSP_24接收到所有子块结果后,产生复图像进行后续处理,最终产生图像并输出。

图6 SAR处理时序

4 成像结果验证

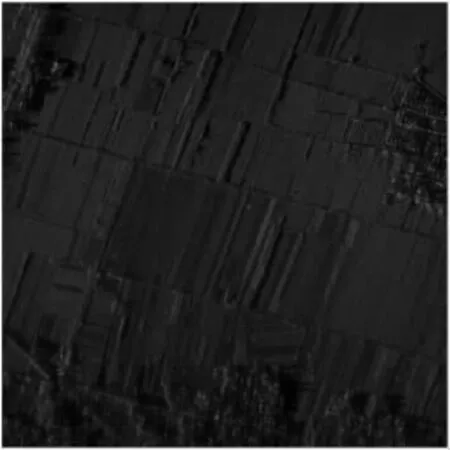

图7所示为该SAR成像处理系统的验证平台,调试计算机通过以太网输入试飞获取的原始数据,经过处理系统进行SAR成像处理,成像结果如图8所示,图像分辨率为 0.5 m。由图可见,该图像各个部位聚焦良好、细节清楚且层次丰富,验证了该成像系统的有效性。

图7 SAR处理验证平台

图8 SAR图像

传统的单核DSP架构,需要多达40个DSP才能勉强保证SAR成像处理的实时性,该多核DSP架构仅使用8个DSP即可满足需求,并且仍留有一定的余量(每个 DSP仅使用5个核),相比之下,该多核 DSP互联架构优势明显。

5 结论

本文介绍了一种适于工程实现的实时SAR成像处理算法,重点研究了多核DSP(C6678)的处理模式、处理性能,并详细分析了多核 DSP中 cache一致性问题。根据研究结论,测试验证了SAR处理的子功能模块。随后,介绍了一种典型的RapidIO互联架构,设计并实现了基于该架构的SAR成像处理系统。结果表明,该系统相对于传统架构具有高效性、重构性和可扩展性。

[1]周峰,王琦,邢孟道,等.一种机载大斜视 SAR运动补偿方法[J].电子学报,2007(35):463-468.

[2]孙进平.机载聚束模式合成孔径雷达的成像算法研究[D].北京:北京航空航天大学,2001.

[3]毛新华.PFA在SAR超高分辨率成像和SAR/GMTI中的应用研究[D].南京:南京航空航天大学,2009.

[4]CARRARA W G,GOODMAN R S,et al.Spotlight synthetic aperture radar signal processing algorithms.Artech House,Boston,1995.

[5]李爱波,姜明,何涛.一种基于改进PFA算法的机载大斜视SAR实时信号处理系统设计[J].计算机工程与应用,2014.

[6]TMS320C6678 Multicore Fixed and Floating-Point DigitalSignal Processor[J].USA:Texas,2011.

Research and design of SAR imaging based on multi-core DSP interconnection architecture

Zhang Qiang,Feng Yangsong,Guo Peng

(Avic Leihua Electronic Technology Research Institute,Wuxi 214063,China)

This paper proposes a SAR imaging solutions based on multi-core DSP interconnect architecture.First,a Polar Format Algorithm(PFA)based on sub-aperture azimuth interpolation is introduced.Then,research the processing performance of TI's multi-core DSP TMS320C6678,introduces an interconnect architecture based on RapidIO and then proposes a SAR imaging solution. Finally,a SAR image is given.Comparison with traditional solution proves that the solution is effective and advanced.

multi-core DSP;interconnect architecture;RapidIO;SAR;PFA

TN957.52

A

10.16157/j.issn.0258-7998.2016.01.009

(2015-09-10)

张强(1988-),通信作者,男,硕士研究生,工程师,主要研究方向:雷达信号处理,E-mail:zq_szz@163.com。

冯仰松(1984-),男,高级工程师,主要研究方向:雷达信号处理。

郭朋(1988-),男,工程师,主要研究方向:雷达信号处理。

中文引用格式:张强,冯仰松,郭朋.基于多核DSP互联架构的SAR处理研究与设计[J].电子技术应用,2016,42(1):37-39,43.

英文引用格式:Zhang Qiang,Feng Yangsong,Guo Peng.Research and design of SAR imaging based on multi-core DSP interconnection architecture[J].Application of Electronic Technique,2016,42(1):37-39,43.