多核同时多线程处理器的线程调度器设计*

周佳佳,李 涛,黄小康

(西安邮电大学 电子工程学院,陕西 西安 710121)

多核同时多线程处理器的线程调度器设计*

周佳佳,李涛,黄小康

(西安邮电大学 电子工程学院,陕西 西安 710121)

多核同时多线程处理器(SMT_PAAG)是用于图形、图像及数字信号处理的一种多核处理器。基于这种处理器提出了一种硬件线程调度器,该调度器采用同时多线程技术,最多可同时执行四个线程,支持八个线程阻塞模式下的快速上下文切换。这样避免了因阻塞带来的等待问题,能够有效提高处理器的工作效率和资源利用率。通过在处理器上运行图形处理算法进行性能评测。结果表明,SMT-PAAG处理器通过挖掘指令级并行和线程级并行,将处理器的性能提高了69.25%。

多核处理器;同时多线程;阻塞模式;图形处理算法;指令级并行;线程级并行

0 引言

随着并行技术的不断发展,如何更好地提高处理器的并行处理性能成为处理器设计者们急需解决的热点问题。传统处理器通过开发指令级并行(Instruction Level Parallelism,ILP)[1]来提高处理器的性能,但由于应用程序自身的ILP很低、硬件的复杂度及功耗等众多因素的影响导致处理器的性能不高。因此设计者们把目光纷纷投向更高层次的并行-线程级并行(Thread Level Parallelism,简称 TLP)[1-2]。

同时多线程最先由美国加州大学的 Tullsen等人在1995年开始研究,并提出了基本的 SMT[3-4]处理器模型。主要原理是通过资源竞争和资源动态共享的方式使所有的执行单元同时活跃,充分利用TLP和ILP来提高处理器的资源利用率。

目前的商用处理器采用的技术主要是同时多线程和片上多处理器技术,例如 Intel的 P4处理器[5]的Hyper-thread技术实现同时执行两个线程,IBM的Power5处理器[6]每个芯片有两个内核,每个内核可以同时执行两个线程。SUN的 Niagara处理器[7]每个芯片有 8个内核,每个内核可以同时执行4个线程。我国的龙芯2号处理器[8]也采用了超标量与同时多线程技术来设计。

本文在多核处理器[9-11]的基础上提出了一种采用同时多线程技术[3-4]的线程调度器[12]设计。与Niagara处理器相比,本文中的多线程处理器拥有16个核,每个内核一共具有8个线程,最大可以同时执行4个线程,并且可以在高低线程之间快速切换,减少了因为线程中遇到长周期指令所造成的资源浪费,同时也提高了处理器的利用效率。

1 整体硬件结构

时钟共享多线程处理器是一种适用于图形和图像处理的并行阵列机。该阵列机支持MIMD(Multiple Instruc-tion Stream Multiple Data Stream)运行模式、分布式指令并行模式和流处理运行模式这三种工作模式,同时还具有异步执行、核间通信以及线程间通信的机制。

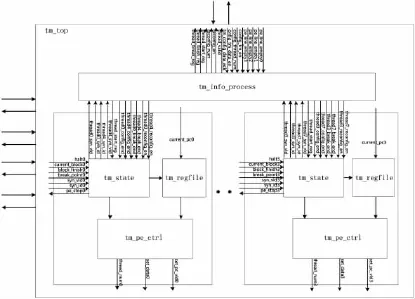

这种结构的阵列机由16个处理单元(Processing Element,PE)互连构成一个4×4的二维阵列,还包括1个前端处理器、4个协处理器、2个调度器及2个存储管理。系统的整体结构如图1所示。

图1 时钟共享多线程处理器系统整体框图

2 线程调度器功能描述

线程调度器完成的功能描述如下:

(1)监测预处理模块,当外部需要给线程加载指令或数据时响应预处理模块;

(2)当线程发生阻塞时负责切换线程,并产生 PE某一个线程的启动信息,其中包括启动有效信号、起始PC值、启动的线程号;

(3)线程之间的同步处理,负责监视需要同步的线程是否同步结束;

(4)当外部需要重新配置某一个线程的指令或数据时负责停止该线程,产生pe_stop信号;

(5)给外部提供三个8位的寄存器,分别为线程启动信息寄存器、线程结束信息寄存器、线程断点信息寄存器。

3 同时多线程设计方案

同时多线程技术最大的优点在于增加很少的面积,就能够获得很高的资源利用率,即用较小的成本换取较大的并行性能,充分地挖掘了线程级的并行。

本文基于时钟共享多线程处理器提出的线程调度器支持八个线程,最多可以同时执行四个线程。这四个线程同时执行各自的程序。每个线程拥有各自独立的取指单元、译码单元、指令存储和数据存储。而其他的资源,如各个执行单元和地址流水线,则是八个线程共享。

在每一个时钟周期的上升沿,每个PE最多有八条流水线在执行,且最多可输出四条流水线结果,这四条流水线产生的结果属于不同的线程组,每个线程组都拥有高低两个线程。因此在某一组中若有一个线程陷入阻塞状态,则可以切换至组内的另一线程来执行程序,可以有效隐藏线程由于等待过程所造成的延迟,提高处理器整体的工作效率。

4 线程调度器详细设计

4.1线程管理器的总体结构

该调度器由信息处理模块、状态控制模块、寄存器模块、PE控制模块四大部分构成,各模块的连接关系如图2所示。

图2 线程调度器的整体架构框图

线程调度器的工作流程为:信息处理模块接收来自预处理模块的配置信息、指令、数据及加载结束信号,判断是否需要启动该线程。线程启动之后状态控制模块中对应的线程状态机发生跳转,同时寄存器模块实时记录该线程的PC值。当接收到译码模块的阻塞信息时停止当前运行的线程且切换线程,PE控制模块负责产生新线程的启动信息。当线程运行结束后,信息处理模块负责记录线程的结束信息。

4.2线程调度器的工作模式

线程调度器拥有五种工作模式:启动模式、阻塞工作模式、同步模式、断点模式和重配置模式。

启动模式线程接收来自预处理模块的线程启动信息配置要启动的线程,将对应的线程ID号和PC值发送给PE来执行。

阻塞工作模式表示当某一线程遇到阻塞,则切换到其线程组内的另一线程上来执行。若是两个都阻塞,则先解除阻塞的线程先执行。

同步模式下对需要同步的几个线程进行等待处理,并判断是否达到同步。若达到,则解除同步模式,开始正常执行;若没有达到,则继续等待。

断点模式是用来方便处理器进行调试错误的一种工作模式。当程序计数器PC遇到断点时,该线程停止工作,保存工作信息以待调试检查。

重配置模式是对线程进行重新配置,根据上层的需要对线程要执行的程序内容进行添加或更改。

4.3线程状态转移关系

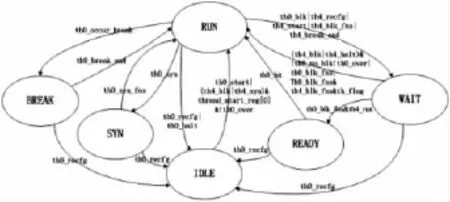

如图3所示,为线程调度器中线程的状态转移图。

图3 线程状态转移图

其中各个状态说明如下:

(1)IDLE:空闲状态。当线程启动信号有效时(th_start=1),则状态跳转到RUN运行状态;

(2)RUN:运行状态。当线程位于此状态时,表示线程正在执行,遇到阻塞或等待跳转到WAIT状态;

(3)BREAK:断点状态。当线程的断点数据收集结束(th_break_end=1)时,状态跳转到RUN运行状态;

(4)WAIT:等待状态。当线程发生重配置(th_recfg=1)时,则状态跳转到IDLE初始状态;当线程阻塞解除(th_blk_fns=1)时状态跳转到RUN运行状态;

(5)SYN:同步状态。线程位于该状态下,遇到同步解除(th_syn_fns=1)信号,跳转到READY状态;

(6)READY:准备状态。表示线程处于一个随时可以启动的状态,当线程被选中时(th0_hit=1),则状态跳转到RUN运行状态。

5 仿真结果分析和比较

本文采用 Xilinx公司的 ISE14.4工具对硬件电路进行了综合,选用 Xilinx公司型号为 XC7V2000t-2fhg1761的FPGA,设计电路的最高频率可以到达431.816 MHz。

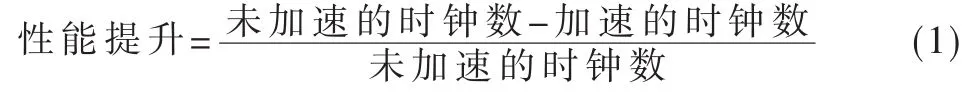

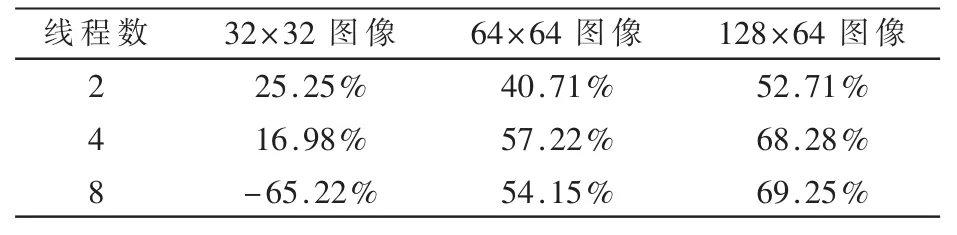

在完成功能仿真和综合的同时,本文还进行了简单的性能分析。测试在8个PE上进行,采用图像处理中的边缘检测算法,分别对32×32、64×64以及128×64的图像进行测试,最后得到的结果如表1所示。另外根据性能提升计算公式(1)[12]可以得出整体处理器的性能提升百分比如表2所示。

表1 执行时间(时钟数)

表2 性能提升(百分比)

可以看出,对于比较小的图像,过多的线程会导致整体运算速度变慢。这是因为此时图像整体运算时间比较短,线程切换所造成的延时会在整体时间中占据比较大的比例。而对于更大的图像,同时多线程技术则对处理器的性能提升影响比较大。对于多核同时多线程处理器而言,八个线程的线程调度器设计会使处理器得到更高的性能提升,充分体现了同时多线程技术的优点。

6 总结

本文通过对时钟共享多线程处理器架构的深入研究,采用同时多线程技术设计和实现了处理器的核心部件——线程调度器。通过在处理器的多个线程上运行图像处理算法,得到处理器的加速比最大为69.25%,充分提高了多核处理器的性能。并对所设计的硬件电路进行了全面仿真验证,综合和仿真结果表明电路的功能正确,工作频率为431.816 MHz,达到了时钟共享多线程处理器的需求。

[1]THEO U,BORUT R,JURIJ S.Multithreaded processors[J]. The Computer Journal,2002,45(3):320-348.

[2]BRUNIE N,COLLANGE S,DIAMOS G.Simultaneous branch and warp interweaving for sustained GPU performance[C]. Computer Architecture(ISCA),2012:49-60.

[3]刘权胜,杨洪斌,吴悦.同时多线程技术[J].计算机工程与设计,2008,29(4):963-967.

[4]EGGERS S J,EMER J S,LEVY H M,et al.Simultaneous multithreading:A platform fornext-generation processors[J]. IEEE Micro,1997,17(5):12-19.

[5]张云.解析超线程技术[J].甘肃联合大学学报,2007,21(4):99-101.

[6]Frank Soltis.Power5对 i系列意味着什么[J].中国经济和信息化,2004,20(6):A2-A3.

[7]POONACHA K.Niagara:a 32-way multithreaded sparc processor[J].Mirco,IEEE,2005,25(2):21-29.

[8]李祖松,许先超,胡伟武,等.龙芯2号处理器的同时多线程设计[J].计算机学报,2009,32(11):2266-2273.

[9]黄虎才.多态阵列处理器的并行计算研究[D].西安:西安邮电大学,2014.

[10]李涛,杨婷,易学渊.萤火虫 2:一种多态并行机的硬件体系结构[J].计算机工程与科学,2014,12(2):191-200.

[11]李涛,肖灵芝.面向图形和图像处理的轻核阵列机结构[J].西安邮电学院学报,2012,17(3):41-47.

[12]钱博文,李涛,韩俊刚,等.多态并行处理器中的线程管理器设计[J].电子技术应用,2014(2):30-32.

Design of a thread scheduler in a simultaneous multi-threaded muti-core processor

Zhou Jiajia,Li Tao,Huang Xiaokang

(School of Electronic Engineering,Xi′an University of Posts&Telecommunications,Xi′an 710121,China)

SMT-PAAG is a simultaneous multithreaded multi-core processor for graphics,image and digital signal processing.The design of hardware thread scheduler for this processor is presented here.The scheduler uses simultaneous multi-threading technology(SMT)that can simultaneously execute up to four threads,and supports fast context switching with eight threads in blocking mode. This avoids the waiting caused by obstruction,at the same time,the design improves efficiency and resource utilization of the processor effectively.We conducted performance evaluation by running on the processor with graphics processing algorithms.The result shows that the performance of SMT-PAAG processor is increased by 69.25%by exploring instruction level parallelism(ILP)and tread level parallelism(TLP).

multi-core processor;SMT;blocking mode;graphics processing algorithms;ILP;TLP

TN492

A

10.16157/j.issn.0258-7998.2016.01.003

国家自然科学基金重点资助项目(61136002);教育部科学研究计划重点资助项目(2111180)

2015-06-09)

周佳佳(1989-),女,硕士研究生,主要研究方向:数字集成电路。

李涛(1954-),男,博士,教授,主要研究方向:计算机体系结构、计算机图形学、大规模集成电路。

黄小康(1992-),男,硕士研究生,主要研究方向:电路与系统。

中文引用格式:周佳佳,李涛,黄小康.多核同时多线程处理器的线程调度器设计[J].电子技术应用,2016,42(1):19-21.

英文引用格式:Zhou Jiajia,Li Tao,Huang Xiaokang.Design of a thread scheduler in a simultaneous multi-threaded muti-core processor[J].Application of Electronic Technique,2016,42(1):19-21.

——以大庆长垣萨尔图油田为例