二次耦合直流输出的金属氧化物TFT行驱动电路

胡宇峰, 李冠明, 吴为敬*, 徐 苗, 王 磊, 彭俊彪

(1. 华南理工大学 电子与信息学院, 广东 广州 510641;2. 华南理工大学 发光材料与器件国家重点实验室, 广东 广州 510641)

二次耦合直流输出的金属氧化物TFT行驱动电路

胡宇峰1, 李冠明2, 吴为敬2*, 徐 苗2, 王 磊2, 彭俊彪2

(1. 华南理工大学 电子与信息学院, 广东 广州 510641;2. 华南理工大学 发光材料与器件国家重点实验室, 广东 广州 510641)

为了弥补现有氧化物TFT的行驱动电路输出模块在功率消耗、响应速度、输出摆幅等方面的不足,提出了基于二次耦合的直流输出模块,并由此研究设计新的行驱动电路拓扑。仿真结果表明,该输出模块具有驱动能力强、响应速度快等优点。最后,基于刻蚀阻挡层(ESL)结构的氧化物TFT工艺,在玻璃衬底上成功制备了该行驱动电路,实测单级功耗为325 μW。

行驱动电路; 氧化铟锌薄膜晶体管; 耦合效应

1 引 言

阵列行驱动集成(Gate-driver on array,GOA)技术是利用薄膜晶体管(Thin film transistor,TFT)将行驱动电路集成至显示屏阵列以取代传统外接驱动芯片的技术。GOA技术具有减少制造工艺、节约生产成本、降低边框宽度等优点[1-3]。GOA技术常用的TFT器件有非晶硅TFT、低温多晶硅TFT以及金属氧化物TFT(Metal oxide TFT, MOTFT)3种。MOTFT因其简单的制造工艺、良好的一致性以及适中的电子迁移率等优点成为当前GOA技术研究与应用的热门。然而MOTFT为N型增强型器件,且当其栅源电压为0时,其漏源极间仍有较强的电流流通能力。MOTFT的这些特点增加了行驱动电路的设计难度[4-6]。

目前已有一些基于MOTFT的行驱动电路的报道,这些电路利用多个负电源[7-9]、浮栅结构[10]、相邻TFT串接反馈(Series-connected two transistor, STT)[11]等方式,彻底关闭MOTFT,有效解决了因MOTFT漏电而导致电路失效的问题[12]。然而上述电路的输出模块多采用AC-AC输出模块[7-12], 虽然AC-AC方式结构简单、易于控制,但驱动晶体管的极间寄生电容会产生较大的动态功耗,并且该功耗正比于时钟频率,导致电路效率随频率的升高而变低。针对这一不足,文献[13]提出了一种AC-DC输出模块, 虽然使极间寄生电容不再产生动态功耗,但仍存在响应速度慢、驱动能力弱的缺点。

本文提出了一种基于二次耦合的直流输出模块,通过两次耦合效应,增强了电路驱动能力,降低了充电延迟时间,同时直流输出结构消除了行驱动TFT极间寄生电容引起的动态功耗,从而达到了高速度、低功耗的效果。

2 TFT器件结构与性能

图1为AC-AC、AC-DC和本文提出的二次耦合直流输出模块的电路图。图1(a)所示为AC-AC输出模块,其中,移位输出晶体管Ta1与行驱动输出晶体管Ta2的栅极连接至同一节点,漏极与各自对应的时钟信号相连,由时钟信号产生输出信号。AC-AC方式的缺点是驱动晶体管的极间寄生电容会产生较大的动态功耗,并且该功耗正比于时钟频率,导致电路效率随频率的升高而变低。图1(b)所示为AC-DC输出模块,分离移位输出晶体管Tb1与行驱动输出晶体管Tb2的栅极,将移位输出COUT作为Tb2的栅控制信号,并将Tb2漏极与正电源连接形成直流输出结构。因Tb2的漏极电平稳定不变,极间寄生电容不产生动态功耗。但Tb2仅在移位输出COUT的电压大于阈值电压时开启,且Tb2不具备电压自举能力,输出摆幅有限,因此AC-DC方式存在响应速度慢、驱动能力弱的缺点。图1(c)所示为本文提出的基于二次耦合的直流输出模块, 其中一次耦合结构与二次耦合结构电路原理一致,一次耦合结构的输出作为二次耦合结构、直流输出结构的控制信号。二次耦合结构的输出作为级联输出COUT。行驱动输出晶体管Tc3的漏极与正电源相连构成直流输出结构。该模块通过两次耦合效应,增强了电路驱动能力,降低了充电延迟时间,同时直流输出结构消除了行驱动TFT极间寄生电容引起的动态功耗,从而达到了高速度、低功耗的效果。

Fig.1 Three types of output modules. (a)AC-AC output module. (b)AC-DC output module. (c)Twice-bootstrap DC output module.

本文提出的行驱动电路使用了如图2(a)所示的蚀刻阻挡层(Etch stop layer, ESL)结构的非晶氧化铟锌TFT(Indium zinc oxide-TFT,IZO-TFT),其制造步骤如下:

首先在玻璃衬底上沉淀一层金属钼作为栅极,其厚度约为200 nm;然后通过等离子体增强化学气相沉积的方法在栅极上形成一层SiO2作为栅极绝缘层,其厚度约为200 nm;再通过磁控溅射方法在SiO2层上溅射一层In与Zn的量比为1∶1的IZO有源层,其厚度约为30 nm;随后在有源层上制作一层刻蚀阻挡层,其厚度约为200 nm;再通过直流溅射法将源漏电极金属沉淀在阻挡层上,并利用湿法刻蚀使其图形化;最后再形成一层SiO2作为钝化保护层[14]。

图2(b)为使用安捷伦半导体测试系统B1500A对宽长比为20 μm/10 μm的IZO -TFT分别在Vds为0.1 V和10.1 V的条件下测得的转移特性曲线。该TFT的阈值电压为1.3 V,迁移率为18 cm2/(V·s),开关比为2.95×109。其中,阈值电压为深线性区电流(Vds= 0.1 V)的线性外延在Vgs轴上的截距,而迁移率通过深线性区电流的斜率得到。

图2 (a)TFT结构图;(b)TFT转移特性曲线。

Fig.2 (a) Device structure of TFT. (b) Transfer characteristic of TFT.

3 行驱动电路结构

图3(a)为所述行驱动电路的电路原理图。该行驱动电路可以划分为输入模块、反相器模块、二次耦合直流输出模块。其中,反相器模块是将T3的栅极、T4的栅极和源极与时钟CK1连接起来的时钟控制反相器,这种结构能够消除传统二极管结构的反相器因存在直流通路而产生的额外功耗,提高电路工作效率[15]。二次耦合直流输出模块由一次耦合结构、二次耦合结构以及直流输出结构构成。其中,一次耦合结构由T5A、T5B、T6A、T6B和C1组成,T5A(T6A)与T5B(T6B)相串联并与T11构成STT结构,因此分析时可将这两个TFT等效为一个宽长比等于T5A(T6A)、寄生电容增大1.5倍的TFT。二次耦合结构由T7、T8和C2组成。二次耦合结构的输出作为移位输出信号COUT并连接至T11的栅极,COUT为高电平时打开T11,将CK3反馈至T5与T6,维持Q点电平稳定。直流输出结构由T9、T10组成,T9的漏极与正电源VD相连形成直流输出结构,T9的栅极与二次耦合结构的T7的栅极连接至同一节点Q,使T9在第二次耦合时彻底打开,提高输出摆幅。

图3(b)为所述行驱动电路的时序图,单级行驱动电路的工作时序可分成以下几个阶段:

(1)输入阶段:CK1变为高电平,其他时钟保持低电平不变,T1、T3被打开,输入信号VIN通过T1存储至电容C1的一端M点上。正电源VD通过T3对Qb点充电,使Qb变为高电平并打开T6、T8和T10,Q点被拉低至低电平VSL,T7和T9此时为关闭状态,COUT、GOUT输出低电平分别为VSL、VS。

(2)预输出阶段(第一次耦合阶段):CK1变为低电平而CK2升至高电平,CK3保持低电平。CK1变低使T1和T3关闭。由于电容耦合效应,M点电平在CK2变为高时被耦合至更高并彻底打开T5,CK2通过T5对Q点充电,Q点电平逐渐上升。Q点电平升高使T4打开并将Qb点拉至低电平VSL,关闭T6、T8与T10。第一次耦合完成。需要注意的是,T7、T9在此阶段已经被打开,COUT因CK3为低电平而保持低电平VSL不变,GOUT的电平逐渐升高但始终低于VD。尽管此阶段GOUT信号驱动能力较弱,但仍具备一定的驱动能力,因此可通过调整像素电路的时序,利用GOUT信号预先对负载RC充电,从而降低GOUT在输出阶段的上升时间,提高电路响应速度。

(3)输出阶段(第二次耦合阶段):CK2降至低电平而CK3跳至高电平,CK1保持低电平。CK3变高打开T2,电容C1存储的电荷通过T2被释放,M点变为低电平VSL。Q点电平因为C2的耦合效应被提高至两倍VD,彻底打开T7与T9,使COUT与GOUT摆幅达到最大。同时,COUT通过T11反馈至T5和T6,彻底关闭T5与T6,减少Q点电荷泄漏,稳定输出状态。第二次耦合完成。

(4)复位阶段:CK1变为高电平而CK3降为低电平,CK2保持不变。T3再次打开,VD通过T3对Qb点充电并打开T6、T8、T10,电容C2存储的电荷通过T6被释放,Q点被拉至低电平VSL。同样地,COUT、GOUT也被分别拉低至低电平VSL、VS,电路复位完毕。

图3(c)为所述行驱动电路的级联图。其中,第N级的行驱动电路的移位输出信号连接至第N+2级的输入端,相邻级间无信号关联。该行驱动电路共使用了1个正电源VD,2个负电源VS、VSL和3个驱动时钟CK1、CK2、CK3。

图3 行驱动电路的电路原理图(a)、时序图(b)和级联图(c)。

Fig.3 Circuit schematic (a), timing diagram (b) and block diagram (c) of the proposed gate driver, respectively.

4 电路仿真

4.1 行驱动电路功能分析

对图2所示的TFT使用Silvaco的Utmost IV工具进行参数提取与建模,利用Smartspice仿真软件对所述行驱动电路进行了仿真验证。仿真条件以及电路设计参数与如表1所示。其中CK1、CK2、CK3的脉宽为3 μs,占空比为1/3,相位差为120°。

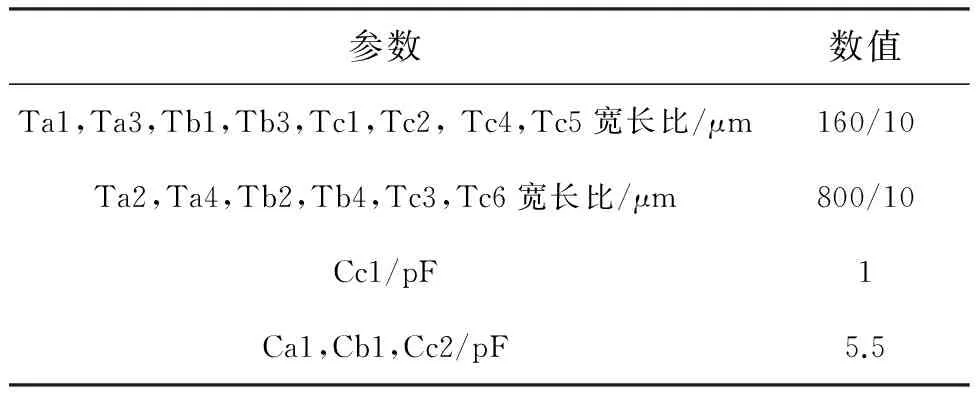

表1 仿真条件与电路设计参数

Tab.1 Simulation conditions and design parameters of gate driver

参数数值VD/V10VS/V-6VSL/V-10CK1/V-10~10CK2/V-10~10CK3/V-10~10负载R/kΩ5负载C/pF50T1,T2宽长比/μm80/10T3,T4宽长比/μm100/10T5A,T5B,T6A,T6B,T7,T8宽长比/μm160/10T9,T10宽长比/μm800/10T11宽长比/μm10/10C1/pF1C2/pF5.5

仿真波形如图4所示,其中图4(a)为行驱动电路关键节点在两次耦合过程中电压的跳变波形。第一次电压跳变发生在M点处,VIN对C1充电后,M点处电平为Vm,当时钟CK2变高时,M点电平升高ΔV1:

(1)

其中,Csn和Cdn分别代表TFT的源极、漏极的寄生电容,Vckn为时钟信号CKn变化幅度。故耦合后M点的电平为:

(2)

由式(2)可知,C1的值与M点电压增量成正比,即可通过增大C1来提高ΔV1。但过大的电容值会延长C1的充电时间,降低电路速度,且更大电容需要更大电路面积,因此必须适中取值,此处C1取1 pF。

第二次电压跳变发生在Q点处,第一次耦合后C2的Q点电平为Vq,当CK3变高时,Q点电平升高ΔV2:

(3)

(4)

由于驱动晶体管T7、T9的尺寸远大于其他TFT,对应的极间寄生电容也远大于其他TFT的极间寄生电容,C*对ΔV2的影响可以忽略,因此式(3)可化简为:

耦合后Q点的电平为:

(6)

相同地,C2的值决定耦合时电压增量,C2应足够大以维持输出时Q点电平稳定,但增大C2也会增大电路的动态功耗,因此C2适中取值为5.5 pF。

图4(b)为行驱动电路输出波形图,其中GOUT信号在预输出阶段结束时已上升至80%最大摆幅,证明二次耦合直流输出模块有较好的预充电能力。此外,COUT与GOUT信号在输出阶段保持相对同步,没有因驱动信号不同源而产生相对超前或滞后,证明二次耦合直流输出模块有较好的时序稳定能力。

图4 电路仿真波形图。(a) 关键节点波形;(b)输出波形。

Fig.4 Simulation waveforms of the proposed gate driver. (a) Waveforms of key nodes. (b) Output waveforms.

4.2 3种输出模块对比

4.2.1 响应速度

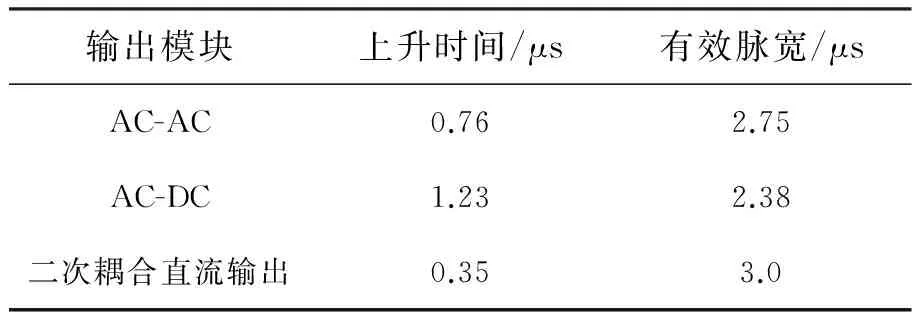

通过对图3所述行驱动电路的输出模块替换,图1中3种输出模块在表1中相同仿真条件下的输出波形如图5所示。表2为这3种输出模块的设计参数。

参数数值Ta1,Ta3,Tb1,Tb3,Tc1,Tc2,Tc4,Tc5宽长比/μm160/10Ta2,Ta4,Tb2,Tb4,Tc3,Tc6宽长比/μm800/10Cc1/pF1Ca1,Cb1,Cc2/pF5.5

通过对图5中输出波形进行参数提取,得到这3种输出模块的性能参数如表3所示。其中,有效脉宽为输出信号大于1/2正电源电压至输出阶段结束所持续的时间。根据之前的分析可知,尽管二次耦合直流输出模块的信号上升时间过程较长,但这一过程分可为预输出阶段与输出阶段,在预输出阶段完成时,输出信号已经达到80%最大摆幅,因而能够极大地缩短信号在输出阶段的上升时间。

表3 3种输出模块的性能参数

Tab.3 Performance parameters of three types of output modules

输出模块上升时间/μs有效脉宽/μsAC-AC0.762.75AC-DC1.232.38二次耦合直流输出0.353.0

4.2.2 动态功耗

行驱动电路的功耗可以分为静态功耗和动态功耗,由于静态功耗远小于动态功耗,分析时可以忽略,因此行驱动电路的功耗可表示为[13]:

(7)

其中,N为校正系数,fclk为时钟频率,C为寄生电容,Vclk为时钟电压摆幅。

根据式(7),计算得到的3种输出模块在不同驱动脉宽下产生的动态功耗见表4。

由于二次耦合直流输出模块比AC-DC输出模块多一级耦合结构,动态功耗增加了34%,但仍比AC-AC输出模块降低了10%。

综合上述分析,二次耦合直流输出模块具有响应速度快、驱动能力强、功耗适中等优点。

表4 3种输出结构的动态功耗

Tab.4 Dynamic power consumption of three types of output modules

输出模块功耗/μW3μs脉宽10μs脉宽AC-AC678205AC-DC455138二次耦合直流输出611185

5 实验与分析

根据表1的电路设计参数,我们在玻璃基板上成功地制作了该行驱动电路,图6(a)为电路的光学显微图。包含信号引线的单级行驱动电路的尺寸为1 504 μm ×270 μm。

为避免因蚀刻差异而引起的相邻器件参数失衡以及避免因时钟走线长度差异过大而引发时序竞争冒险,各器件以水平对称方式放置。同时,为避免静电击穿和电磁干扰,对走线与走线、走线与器件、器件与器件均设置了足够的安全距离。

图6(b)为电路在VD 为10 V、VS 为-6 V、VSL为-10 V、时钟频率为66.7 kHz、负载电阻为1 kΩ、电容为30 pF的条件下的输出波形,波形稳定平滑,没有发生畸变,证明该电路具有足够的驱动能力。该实测波形是由包含有半导体脉冲发生单元(SPGU)和源测试单元(SMU)的B1500A测试系统测得。在该条件下,实测单级行驱动电路功耗为325 μW。

图6 (a) 实际制作的行驱动电路的光学显微图;(b)实测输出波形。

Fig.6 (a) Micrograph of the proposed gate driver. (b) Measured output waveform.

6 结 论

本文针对AC-AC和AC-DC驱动模块在功率消耗、响应速度、输出摆幅等方面的不足,提出了一种新型的基于二次耦合的直流驱动模块。该模块通过两次电容耦合效应,可以缩短内部电路充电时间和提高输出TFT的栅极电平,从而提高电路响应速度。在此基础上,提出了一种新型行驱动电路拓扑,仿真表明该行驱动电路具有驱动能力强、响应速度快、功耗适中的优点。最终使用基于ESL结构的氧化物TFT工艺,在玻璃衬底上成功地制造了该行驱动电路。实验表明,该电路能够正常工作在66.7 kHz的驱动频率下,且单级电路功耗仅为325 μW。

[1] LIN C L, TU C D, WU C E,etal.. Low-power gate driver circuit for TFT-LCD application [J].IEEETrans.ElectronDev., 2012, 59(5):1410-1415.

[2] CHU L W, LIU P T, KER M D. Design of integrated gate driver with threshold voltage drop cancellation in amorphous silicon technology for TFT-LCD application [J].J.Disp.Technol., 2011, 7(12):657-664.

[3] LIAO C W, HE C D, CHEN T,etal.. Implementation of an a-Si∶H TFT gate driver using a five-transistor integrated approach [J].IEEETrans.ElectronDev., 2012, 59(8):2142-2148.

[4] 曹镛,陶洪,邹建华,等. 金属氧化物薄膜晶体管及其在新型显示中的应用 [J]. 华南理工大学学报(自然科学版), 2012, 40(10):1-11.

CAO Y, TAO H, ZOU J H,etal.. Metal oxide thin film transistors and their application to novel display technology [J].J.SouthChinaUniv.ofTechnol. (Nat.Sci.Ed.), 2012, 40(10):1-11. (in Chinese)

[5] BARQUINHA P, PEREIRA L, GONÇALVES G,etal.. P-202L: late-news poster: long-term stability of oxide semiconductor-based TFTs [J].SIDSymp.Dig.Tech.Pap., 2010, 41(1):1376-1379.

[6] LOOK D C, FARLOW G C, REUNCHAN P,etal.. Evidence for native-defect donors in n-type ZnO [J].Phys.Rev.Lett., 2005, 95(22):225502-1-4.

[7] HONG S J, KANG J S, LEE C H,etal.. P-18: low-power and small-sized scan driver using amorphous oxide TFTs [J].SIDSymp.Dig.Tech.Pap., 2012, 43(1):1108-1111.

[8] KIM B, RYOO C I, KIM S J,etal.. New depletion-mode IGZO TFT shift register [J].IEEEElectronDev.Lett., 2011, 32(2):158-160.

[9] YOO S J, HONG S J, KANG J S,etal.. A low-power single-clock-driven scan driver using depletion-mode a-IGZO TFTs [J].IEEEElectronDev.Lett., 2012, 33(3):402-404.

[10] KANG C K, PARK Y S, PARK S I,etal.. 4.2: integrated scan driver with oxide TFTs using floating gate method [J].SIDSymp.Dig.Tech.Pap., 2011, 42(1):25-27.

[11] KIM B, CHOI S C, LEE S Y,etal.. A depletion-mode a-IGZO TFT shift register with a single low-voltage-level power signal [J].IEEEElectronDev.Lett., 2011, 32(8):1092-1094.

[12] WU Z Y, DUAN L Y, YUAN G C,etal.. 3.2: an integrated gate driver circuit employing depletion-mode IGZO TFTs [J].SIDSymp.Dig.Tech.Pap., 2012, 43(1):5-7.

[13] HUANG C Y, ZHANG L R, ZHOU L,etal.. A low-power scan driver employing IZO TFTs including an AC-DC type output module [J].Displays, 2015, 38:93-99.

[14] LI M, LAN L F, XU M,etal.. Performance improvement of oxide thin-film transistors with a two-step-annealing method [J].Solid-StateElectron., 2014, 91:9-12.

[15] WU W J, LI G M, XIA X H,etal.. Low-power bi-side scan driver integrated by IZO TFTs including a clock-controlled inverter [J].J.Disp.Technol., 2014, 10(7):523-525.

[16] 张立荣,马雪雪,王春阜,等. 基于金属氧化物薄膜晶体管的高速行集成驱动电路 [J]. 物理学报, 2016, 65(2):028501-1-8.

ZHANG L R, MA X X, WANG C F,etal.. High speed gate driver circuit basd on metal oxide thin film transistors [J].ActaPhys.Sinica, 2016, 65(2):028501-1-8. (in Chinese)

[17] WU W J, SONG X F, ZHANG L R,etal.. A highly stable biside gate driver integrated by IZO TFTs [J].IEEETrans.ElectronDev., 2014, 61(9):3335-3338.

[18] LIN C L, TU C D, CHUANG M C,etal.. Design of bidirectional and highly stable integrated hydrogenated amorphous silicon gate driver circuits [J].J.Disp.Technol., 2011, 7(1):10-18.

[19] ZHENG G T, LIU P T, WU M C,etal.. Design of bidirectional and low power consumption gate driver in amorphous silicon technology for TFT-LCD application [J].J.Disp.Technol., 2013, 9(2):91-99.

胡宇峰(1990-),男,湖南邵阳人,硕士研究生,2013年于湖南农业大学获得学士学位,主要从事氧化物TFT器件集成与应用的研究。

E-mail: fisher0729@sina.com吴为敬( 1979-),男,福建福州人,博士,副教授,2008 年于华南理工大学获得博士学位,主要从事金属氧化物TFT集成电路的研究。

E-mail: wuwj@scut.edu.cn

基金项目: 国家自然科学基金(11574306);中国国际科技合作计划(2014DFG62280);“863”国家高技术研究发展计划(2015AA03A101)资助项目

Abstract: Highly stress tests were carried out for mid-power GaN-based LEDs encapsulated with silicone and green/red mixed phosphors. Except for the optical and electrical measurement, the reflection spectroscopy and time of flight-secondary ion mass spectrometry (TOF-SIMS) were also used to investigate the failure mechanism. Our results show that the high temperature and humidity play an important role in determining the failure mode for mid-power blue and white LEDs. The decrease of the blue emission is related to the degradation of the transparent silicone and the reflectivity by the oxidation and the contamination of sulfide and chlorine. While the dissolution of the phosphors in white LEDs will lead to the decrease of the conversion efficiency and deteriorate the photometric and colorimetric properties of mid-power white LEDs.

Key words: mid-power LEDs; package materials; degradation behaviors

Gate Driver Integrated by MOTFTs Using Twice-bootstrap DC Output Module

HU Yu-feng1, LI Guan-ming2, WU Wei-jing2*, XU Miao2, WANG Lei2, PENG Jun-biao2

(1.SchoolofElectronicandInformationEngineering,SouthChinaUniversityofTechnology,Guangzhou510641,China; 2.StateKeyLaboratoryofLuminescentMaterialsandDevices,SouthChinaUniversityofTechnology,Guangzhou510641,China)

*CorrespondingAuthor,E-mail:wuwj@scut.edu.cn

The gate driver integrated by metal oxide thin film transistors is able to lower the cost of driving ICs and narrow the bezel of display panel, but there are some disadvantages like poor power efficiency, slow response speed and small output swing for the existing output modules. In order to solve these problems, a novel twice-bootstrap DC output module was proposed, and a new gate driver topology was designed based on this module. The simulation results show that the circuit has strong driving ability and fast response speed. Finally, the gate drivers were successfully fabricated on glass substrate integrated by MOTFTs with etch stop layer structure. The power consumption of single stage of the gate driver is 325 μW.

gate driver circuit; IZO thin film transistor; bootstrapping effect

1000-7032(2016)10-1230-07

Degradation Analysis of Mid-power GaN-based LEDs with Different Package Materials

FU Jia-iia, CAO Hai-cheng, ZHAO Li-xia*, WANG Jun-xi, LI Jin-min*

(SemiconductorLightingResearch&DevelopmentCenter,InstituteofSemiconductors,ChineseAcademyofSciences,Beijing100083,China)

*CorrespondingAuthors,E-mail:lxzhao@semi.ac.cn;jmli@semi.ac.cn

TN383+.1 Document code: A

10.3788/fgxb20163710.1230

1000-7032(2016)10-1223-07

2016-05-01;

2016-05-24

国家自然科学基金(61574062,61574061); 广东省科技计划项目(2015B090914003,2014B090916002,2016B090906002)资助

TP394.1; TH691.9

A DOI: 10.3788/fgxb20163710.1223

16-04-28; 修订日期: 2016-05-22