基于ZYNQ的CPFSK数字解调的设计与实现

佐风玲,刁节涛,李 楠,朱 策

(国防科学技术大学 电子科学与工程学院,湖南 长沙 410073)

基于ZYNQ的CPFSK数字解调的设计与实现

佐风玲,刁节涛,李 楠,朱 策

(国防科学技术大学 电子科学与工程学院,湖南 长沙 410073)

传统数字调制解调设计采用FPGA+DSP或ADC的模式,通过传输总线完成数据的存储与传输,针对传输总线设计困难的问题,采用Xilinx新平台ZYNQ,充分利用PL部分并行运算能力强的特点完成了CPFSK解调算法IP核的设计,PS部分通过AXI总线访问IP核,传输速率高达10 Gbit·s-1,提高了对调制信号的处理速度,增加了系统的灵活性,降低了系统的体积和功耗,且便于在机载车载环境下的应用。

连续相位频移键控;ZYNQ;数据传输

ZUO Fengling, DIAO Jietao, LI Nan, ZHU Ce

(School of Electronic Science and Engineering, National University of Defense Technology,Changsha 410073, China)

连续相位频移键控(CPFSK)信号具有较高的频带利用率,相位连续并且兼具了FSK恒包络的特点,被广泛应用在卫星通信系统和便携式移动通信系统中。国内在研究CPFSK调制解调过程中,一般采用DSP、单片机、CPLD、FPGA等平台实现。在实际工程应用中,为满足系统的功能,利用较少的硬件成本资源完成对信号的处理具有很高的使用价值[1-2]。

2011年12月,Xilinx宣布开始向客户出货首款Zynq-7000可扩展处理平台,它将业界标准的ARM双核Cortex-A9 MPCore处理器系统与Xilinx可扩展的28nmFPGA架构整合在一起,以低功耗和低成本等系统优势实现良好的系统性能、灵活性和可扩展性。同时在Zynq上进行数据处理,有别于在其他ARM上进行数据处理,Zynq7000是FPGA内嵌ARM的架构,Xilinx提供了SDK开发工具支持CC++对ARM的编程,使算法的移植比较简捷,也可以使用CC++对FPGA进行IP核编写与封装,这样使ARM与FPGA共同完成数据的处理,加快了数据处理的速度[3-4]。本文利用Zynq异构多核架构的优点,使用软硬件协同设计的方法设计实现,设计流程如图1所示。

图1 软硬件协同设计流程图

1 CPFSK信号调制解调模型设计

常规的FSK信号是由载波频移产生的,频移量mF反应所要表达的数字信息,而FSK是无记忆的。从一个频率到另一个频率切换的实现方法是使用M=2K个调谐到期望的频率的振荡器,再从M个频率中选择一个频率,选择的依据是在信号间隔时间T=K/R秒内要发送的特定kbit·s-1符号。然而,在连续的信号传输时间间隔中,从一个振荡器输出到另一个的突发式切换,造成信号在主要频段之外有较大的频谱旁瓣。因此,采用CPFSK调制方式,提高频带利用率,使得频谱主瓣能量集中、旁瓣滚降系数衰减快,利用软件无线电平台实现CPFSK信号时具有重要意义[1]。

1.1 CPFSK概述

CPFSK是CPM调制的一种特殊形式,当传送的M进制的码元序列为I={±1,±3,…,±M-1},调制信号可表示为

(1)

其中,Eb为码元能量;θ为载波初始相位;fc为载波频率;φi(t)是携带的相位信息

(i-1)T≤t≤iT

(2)

(3)

fd(τ)是瞬时频率偏差

(4)

式中,h为调制指数;T为符号周期。

1.2 模型设计

根据CPFSK信号的概述,调制模块的系统框图如图2所示。由伯努利随机信号发生模块产生二进制随机序列,对二进制随机序列进行差分编码,消除相位模糊[10-12]。然后将随机序列转换成两路数据,根据传输数据符号的不同,通过波形形成模块变为它们所表示的波形符号,此时已经得到了不同的基带波形,再将该波形的同相分路和正交分路分别乘以载波,便可得到CPFSK一次的调制信号,实现了调制的功能。

图2 调制模型

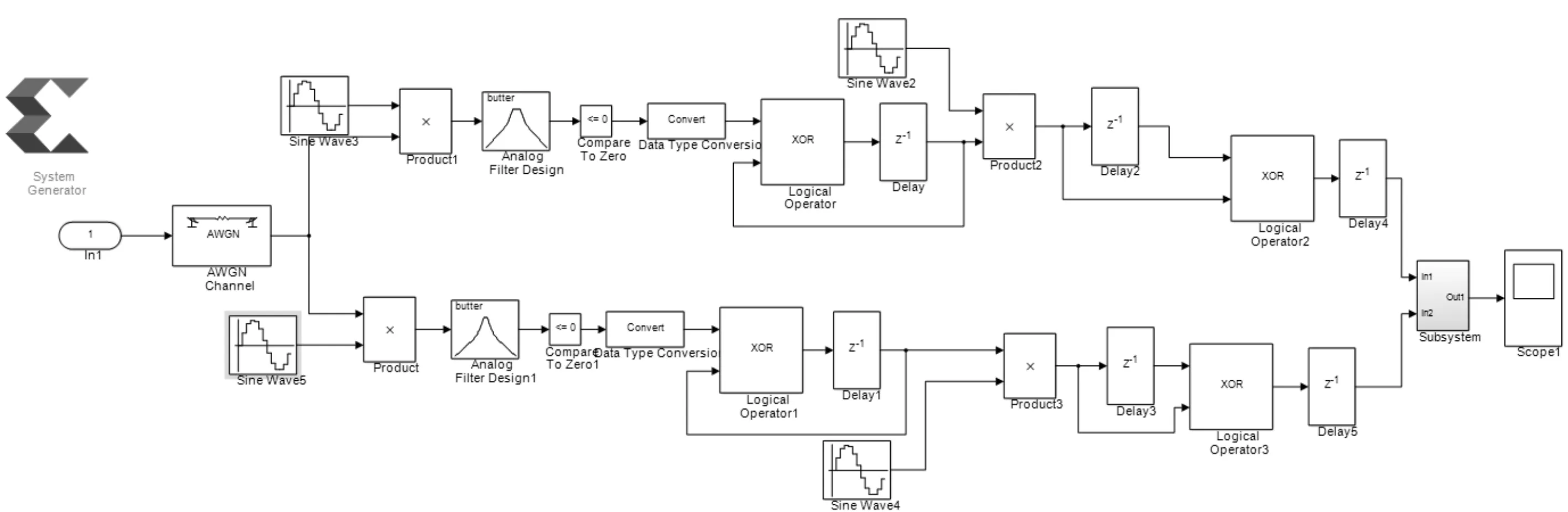

CPFSK的解调模型如图3所示。在信号传输的过程中,外界环境总是会影响信号的传输,所以在仿真过程中,将调制信号通过加入高斯白噪声的信道后进行解调。在Simulink仿真模块库中找到AWGN模块,设置其参数来调整传输过程中的信噪比。解调的主要目的是实现对载波调制的解调和对码元信息的恢复两部分[11-13]。模型的前半部分是对一次载波的解调,后半部分主要是从两路解调波形中恢复出波形所携带的码元信息。

图3 解调模型

2 建立CPFSK解调IP核

Xilinx及许多第三方公司为用户提供了众多IP核,这些IP核将一些特殊功能封装起来供用户调用。在实际使用中,有时用户需要实现一些特殊的功能,可以使用Xilinx提供的工具组装自己的IP核。封装后的IP核可以通过设置相应的参数供用户使用[5-7]。

在模型设计完成,并且验证其正确性之后,可以用System Generator生成HDL网表或者是把模型编译为硬件协同仿真模型、用户自定义IP、综合检查点等。在Vivado环境中通过IP设计实现工程是方便的,在 System Generator中将模型打包成一个IP,并且添加Xilinx为用户提供的一些IP,完成系统搭建。

在System Generator中选择如图4所示的配置IP_Catalog输出方式,选用的器件类型为Zynq xc7z020-1clg484,更改输出路径,配置IP的相关信息。在Generation Comleted完成之后,在Vivado中打开.xpr工程文件。

图4 System Generator的输出

将定制好的IP核添加到设计中,并且添加ZYNQ7 Processing System IP核和AXI Interconnect IP核到设计中,定制IP核通过AXI总线实现与PS的通信,对ZYNQ7 Processing System IP核也要进行配置,将配置好的各个IP核模块连接起来,完成规则检查,并将其封装成顶层HDL文件。系统搭建如图5所示。

图5 Vivado系统搭建

对解调系统进行综合后,根据芯片型号添加封装形式添加管教约束文件,对设计进行映射、翻译等来实现,最后生成比特流。将设计工程导入到SDK平台,在SDK中建立对应的板级驱动包(BSP),BSP提供了一系列的API函数,直接调用API函数可以脱离繁琐的底层寄存器的读和写,提高编程效率。

3 测试验证

系统的基本参数设置:码元速率为60 symbol·s-1;载波频率为20 kHz;采样频率100 kHz;调制指数为0.5。

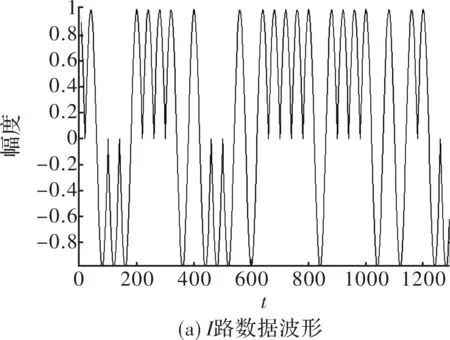

图6 测试分析结果对比

二进制随机数经过调制后得到相位连续的调制信号,分别将调制信号的实部作为I路调制信号,虚部作为Q路调制信号,它们具有正弦函数的性质,而且相互正交。从图6(c)中看出,解调信号与基带信号有一些延迟,但对基带信号的恢复影响较小。调制过程中调制指数对整个系统有较大影响,调制指数越小相位越连续。

4 结束语

国内对CPFSK调制解调的研究都是基于FPGA或者是DSP,本文基于ZYNQ平台,充分利用了Zynq内部FPGA+ARM架构实现了CPFSK的解调,占用了较少的硬件资源,降低了系统的功耗,并且在Simulink环境中完成解调模型设计之后自动生成HDL代码,节省了时间,也使得该算法具有更好的移植性。

[1] Anderson J B, Aulin T, Sundberg C E. Digital phase modulation[M].New York: Applications of Communications Theory,1986.

[2] 胡典荣,郭春生.基于ZedBoard 的 SPI 和以太网传输设计[J]. 杭州电子科技大学学报,2013,13(5):126-129.

[3] 陆佳华,江舟,马岷. 嵌入式系统软硬件协同设计实战指南:基于Xilinx Zynq[M]. 北京: 机械工业出版社,2013.

[4] Xilinx. Xilinx Zynq-7000 all programmable SoC ZC702 evaluation kit[EB/OL].(2013-12-10)[2015-12-15] http:// www.xilinx .com/products/boards-and-kits/EK-Z7-ZC702-G.htm.

[5] Aulin T, Rydbeck N, Sundberg C E W. Continuous phase modulation-part II: partial response signaling[J]. IEEE Transactions on Communications, 1981,29(3):210-225.

[6] 符晓,张国斌,朱洪顺. Xilinx ZYNQ-7000 AP SoC开发实战指南 [M].北京: 清华大学出版社,2016.

[7] Zhang L, Liu B, Xin X, et al. MAMSK-OFDM signal for RoF access with increased tolerance toward frequency offset[J]. Photonics Technology Letters IEEE, 2013,25(4):397-400.

[8] 黄嵩.CPFSK调制解调的研究与实现 [D].成都:西南科技大学,2011.

[9] Hachmeister A, NöLle M, Molle L, et al. Performance comparison of MSK and QPSK optical long haul DWDM transmission with coherent detection[J]. Optics Express,2012,20(4):3877-82.

[10] Xilinx.Optimizing DSP systems design-Xilinx[J].DSP Magazine,2006(1):5-9.

[11] Aulin T, Sundberg C E.Continuous phase modulation-Part I:Full response signaling[J].IEEE Transactions on Communication,1981,3(29):196-209.

[12] Lindell G, Sundberg C E, Aulin T. Minimum euclidean distance for combinations of short rate 1/2 convolutional codes and CPFSK modulation[J]. IEEE Transactions on Information Theory,1984,30(3):509-519.

[13] 刘占线.基于System Generator的QPSK数字调制解调器[J].电子科技,2011,24(8):31-35.

[14] 刘立枫.无线跳频通信中的多进制CPFSK解调技术[D].杭州:浙江大学,2005.

[15] Harris F J, Dick C, Rice M. Digital receivers and transmitters using polyphase filter banks for wireless communications[J]. IEEE Transactions on Microwave Theory & Techniques,2003,51(4):1395-1412.

Design and Implementation of CPFSK Demodulation Based on ZYNQ

The traditional digital modem designed using FPGA + DSP or ADC mode performs data transmission by the bus storage and transmission. But the design of transmission bus is difficult. The new Xilinx platform ZYNQ is adopted to solve this problem. The IP core of the CPFSK demodulation algorithm is designed by taking advantage of the parallel computing capability of PL, and accessed by the PS via AXI bus at a speed of up to 10 Gbit/s, thus improving the processing speed and the flexibility of the system while reducing the system size and power consumption.

continuous phase frequency shift keying; ZYNQ; data transmission

2016- 03- 29

佐风玲(1990-),女,硕士研究生。研究方向:嵌入式系统与固态存储技术。

10.16180/j.cnki.issn1007-7820.2016.10.006

TN925

A

1007-7820(2016)10-018-04