基于TMS320DM365视频压缩传输系统的设计

旦喜荣,陈建春

(西安电子科技大学 电子工程学院,陕西 西安 710071)

基于TMS320DM365视频压缩传输系统的设计

旦喜荣,陈建春

(西安电子科技大学 电子工程学院,陕西 西安 710071)

针对原始视频数据量大,不利于存储与传输的问题,设计了基于TMS320DM365的视频压缩传输系统。实现将多路输入的模拟视频转换为数字视频,在TMS320DM365中压缩编码并打包成TS码流。提供帧率、分辨率、P/I比等参数的设置功能,能适应于多种应用场景。实验结果表明,系统可实现25帧/s、D1分辨率标清视频的压缩传输,满足视频监控的需求。

视频压缩;TMS320DM365;系统电路设计

DAN Xirong, CHEN Jianchun

(School of Electronic Engineering, Xidian University, Xi’an 710071, China)

原始视频数据量大,不利于存储与传输。因此,视频数据的压缩对于视频应用尤为重要。尤其是目前视频质量越来越高,传输方式各式各样,这对于视频采集设备、压缩算法以及视频解决方案又提出了更高的要求。

本文基于视频压缩技术的发展现状与课题具体需求,设计了一种视频压缩传输系统,该系统能够将输入的多路模拟视频信号中任一路转换为数字视频并以MPEG-4压缩编码规范压缩处理,将两路音频信号转换为数字音频并以AAC格式压缩编码,按照MPEG-2系统规范将音视频压缩数据打包为TS码流进行传输。

1 视频压缩总体方案设计

本文采用TI公司DaVinci系列低功耗、低成本的多媒体处理芯片TMS320DM365作为系统的核心处理器,外围加以必要的辅助器件,完成音视频采集压缩传输的嵌入式系统设计。作为高性能数字媒体处理器,TMS320DM365内部集成ARM9处理器与视频图像协处理器,支持H.264、MPEG4等多种格式的视频编解码操作[1]。系统总体框图如图1所示。

图1 系统总体框图

系统的硬件设计包括音视频采集模块、压缩编码模块、DDR存储模块、Flash系统存储模块、传输接口模块以及电源时钟模块[2-3]。其中视频A/D选用TI公司的TVP5146,支持NTSC、PAL、SECAM制式的多路复合视频或者S端子转换为BT.656格式的数字视频,能与TMS320DM365的视频处理前端完美无缝连接。采用处理速度较快、存储空间较大的DDR2作为系统缓存,设计Flash模块存储嵌入式操作系统。模拟音视频数据经过A/D转换之后,在DM365中压缩编码并打包成TS码流,最后经EMIF接口传输至FPGA进行数据的传输。

2 主要模块电路设计

2.1 DDR2缓存模块设计

缓存模块在系统中的主要功能是存储必要的程序和数据,对于视频压缩系统而言,通常需要高速缓存大量的数据,DDR2(Double Data Rate 2)SDRAM由于其速度快、容量大,且价格便宜,因此能较好地满足系统对于缓存的需求[4]。

本系统采用的DDR2为Micron(美国镁光)公司的MT47H64M16,8个L-Bank,16位数据宽度,128 MB的存储空间完全满足视频压缩系统的开发。TMS320DM365内部集成有DDR2控制器,可与DDR2完美无缝连接,两者的电路连接如图2所示。

图2 DDR2电路连接图

其中,电源供电要求1.8 V,DM为输入数据掩码,写数据的过程中若DM为高,则输入数据被屏蔽掉而无效。其中LDM为低8位数据的数据掩码,UDM为高8位数据的数据掩码,分别与TMS320DM365的DQM[0]、DQM[1]相连。DQS(数据锁存信号)是数据的同步信号,采用差分对形式,LDQS与LDQS#为低字节数据锁存信号,UDQS与UDQS#为高字节数据锁存信号。

DDR2中使用ODT(On-Die Termination)新技术,将终端匹配电阻集成到芯片内部。ODT终端电阻值可通过DDR2内部的EMR寄存器来进行设置,有关闭、50 Ω、75 Ω、150 Ω这4种模式供选择。使用DDR2内部终端电阻一方面减少了PCB的板上面积和布局布线的压力,一方面能获得更好的信号完整性。

2.2 NAND Flash存储模块设计

本系统采用的NAND Flash为三星公司的K9K8G08U0A,具有1 GB的存储空间。系统中NAND Flash的主要功能是存储包括引导程序(UBL)、启动程序(UBoot)、内核文件(uImage)以及文件系统等操作系统数据[5]。其中引导程序占用空间20 kB,启动程序占用149 kB,内核文件占用2 001 kB,文件系统占用51.6 MB,总共约54 MB≪1 GB的空间容量。故采用此芯片作为系统的存储模块,可为后期系统的扩展预留较大的空间。

2.3 EMIF接口模块设计

外部存储器接口(EMIF),External Memory Interface,是TI DSP器件上用于外扩存储的一种接口。EMIF可实现DSP与不同类型存储器(SRAM、NAND Flash、OneNAND Flash)的连接,也可与FPGA相连实现数据的高速处理或传输[6]。本系统中将EMIF接口与NAND Flash以及FPGA相连,通过片选来实现分别选通。其中,与NAND Flash的连接完成操作系统等信息的交互,与FPGA的连接则是将压缩好的音视频数据从TMS320DM365传输到FPGA中。具体是在FPGA中设计一个双口RAM,其一端连接TMS320DM365接收数据,另外一端在FPGA中实现数据的缓冲与传输。

其中,EMIF的地址总线由EM_BA与EM_A结合构成,使用方法依赖于数据位宽的选择。当使用16位数据模式时,EM_BA[1]代表最低有效地址位,EM_BA[0]代表地址位EM_A14。而当使用8位数据模式时,EM_BA[1:0]为有效地址位的低两位。

2.4 SPI接口设计

串行外设接口(Serial Peripheral Interface,SPI)是一种高速、全双工同步通信总线[7]。DM365内部集成了SPI模块,支持2~16位的数据宽度,可编程的时钟极性和相位选择。分别在数据格式寄存器(SPIFMTn)中的POLARITYn位与PHASEn位进行设置。与传统视频压缩系统固定启动参数不同,本系统设置动态参数缓冲区,在系统启动前通过PCI桥从上位机获取启动参数,使用SPI接口传输音视频压缩参数到DM365中,系统每次上电后从FPGA中的RAM处读取包括帧率、分辨率、P/I帧比率以及时间等信息再进行嵌入式系统的启动,以适用于不同的应用场景。

3 嵌入式系统软件设计

各个模块硬件电路的功能测试成功之后,进行嵌入式软件的设计。首先进行嵌入式系统的启动,由于DM365片内存储器空间只有32 kB,而一般UBoot文件>100 kB(系统采用的UBoot-1.3.4大小为149 kB),所以想要采取片内存储器的方式从NAND Flash启动系统,至少需要3个阶段的代码引导,即RBL→UBL→UBoot,最后再加载内核及创建文件系统[8]。以本系统选择的NAND Flash启动方式为例,系统加电后先执行固化在芯片内部只读存储器中的RBL程序,RBL根据UBL程序描述符读取UBL程序到芯片内部存储器并运行。UBL程序对底层硬件做简单的初始化之后开始加载功能复杂的UBoot程序到DDR2并运行。UBoot程序可设置更多的参数及器件的初始化,然后从Nand Flash加载、解压和运行Linux内核uImage并启动系统。

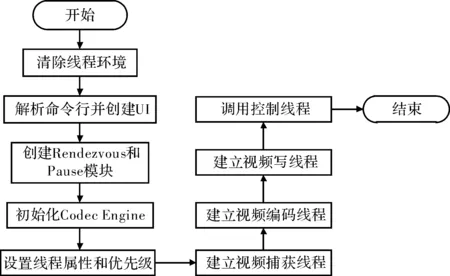

本系统嵌入式软件采用多线程设计思想,软件设计包括主线程、视频捕获线程、视频编码线程和视频写线程[9]。主线程执行必要的初始化并创建其他线程后变成控制线程[10],视频捕获线程采集原始数据,视频编码线程接收来自视频捕获线程的帧数据进行编码,写线程将编码后的视频帧通过EMIF接口发送给FPGA。其中,主线程运行流程如图3所示。

图3 主线程运行流程图

4 测试结果

为验证系统中所设计软件的可行性,在目标板中进行程序测试。测试环境包括操作系统为Windows XP的PC机一台,其中安装有VirtualBox虚拟机以及uBuntu 9.04操作系统;使用系统设计的目标板作为硬件平台;800线标准模拟摄像头作为视频采集设备;使用Windows XP自带的超级终端作为宿主PC机与目标板之间通信的终端界面。

由于NFS服务不用将操作系统及应用程序烧写到目标板中,而能借助于虚拟机中的操作系统进行开发,可加快程序调试和修改的效率。所以在调试阶段一般使用NFS模式进行应用软件的调试。NFS模式下系统启动界面如图4所示。

图4 系统启动界面

系统启动成功后,运行编解码程序,显示效果如图5所示。图像质量较为清晰,25 fra·s-1下720×576分辨率的码率约为500 kbit·s-1。

图5 视频编解码显示效果图

本文针对不同的应用场景,提供参数选择功能。用户可根据实际需求对视频编码程序的帧率、分辨率、码率、P/I帧比率等参数进行灵活设置。以P/I比参数为例,在视频编码过程中,会出现几种不同类型的帧,包括关键I帧、预测P帧以及双向B帧。P帧以前一个I帧做参考,描述帧间变化,B帧则根据两个I帧进行预测。P帧与B帧的使用可有效的降低数据率,在低速目标或静止目标场景较为适用。在venc1.c中修改intraFrameRate可修改P/I帧的比例,默认为30(即每30帧出现一帧I帧)。修改interFrameInterval可修改P/I帧间的B帧比例。修改前后对比如图6所示。

图6 P/I修改前后对比

两图均为25 fra·s-1下352×288分辨率的效果图。其中,图6(a)为默认P/I比30的测试结果,其平均码率约为130 kbit·s-1。图6(b)为P/I比1 800的测试结果,其平均码率约为40 kbit·s-1,可见数据量大幅降低。

5 结束语

本系统设计实现了视频数据的采集、压缩以及传输。在低成本低功耗的前提下,较为有效的解决了原始视频存储与传输的问题。测试结果表明,系统可实现25帧/s、D1分辨率标清视频的压缩传输。且可灵活的设置分辨率、帧率、P/I帧比例等参数,能满足多种应用场景的需求,具有一定的工程实用性。

[1] Texas Instruments. TMS320DM365 digital media system on chip[M].Texas, USA:Texas Instruments,2011.

[2] 王飞.基于DaVinci技术的视频编码系统实现[D]. 西安:西安电子科技大学,2012.

[3] 郝舜.基于DaVinci技术的数字视频系统设计[D]. 西安:西安电子科技大学,2012.

[4] 韩彬,于潇宇,张雷鸣.FPGA 设计技巧与案例开发详解[M].北京:电子工业出版社,2014.

[5] 欧洋.基于闪存的高速PCIe固态存储卡的研究与实现[D].长沙:国防科学技术大学,2012.

[6] 周顺燕,吴丹.TMS320C6713 DSP的高速EMIF数据接口设计与实现[J].计算机测量与控制,2010,18(7):1654-1656.

[7] 刘文博.基于FPGA的微控制器设计[D].西安:西安电子科技大学,2011.

[8] Texas Instruments. TMS320DM36x Digital Media System on Chip ARM_SUBSYSTEM User Guide[M]. Texas,USA:Texas Instruments,2009.

[9] 高玉龙,白旭,吴玮.达芬奇技术开发基础、原理与实例[M].北京:电子工业出版社,2012.

[10] 肖福海.基于DM6446的数字多媒体播放系统的设计[D].哈尔滨:哈尔滨工程大学,2011.

Design and Implementation of Video Compression and Transmission System Based on TMS320DM365

A video compression transmission system based on TMS320DM365 is designed, which is not conducive to the storage and transmission of the original video data. The multi-channel analog video is converted into digital video with compressed encoding and packaged into TS standard stream in TMS320DM365. Setting of such parameters as resolution, frame rate,P/Iratio is provided for use in various application scenarios. Experimental results show that video compression transmission of 25 frames per second andD1resolution is achieved, meeting the needs of video surveillance.

video compression; TMS320DM365; system circuit design

2015- 11- 27

旦喜荣(1990-),男,硕士研究生。研究方向:视频压缩与电路设计。陈建春(1962-),男,博士,教授。研究方向:电子系统设计,信号处理。

10.16180/j.cnki.issn1007-7820.2016.10.005

TN919.8

A

1007-7820(2016)10-15-04