基于FPGA+DSP实时图像采集处理系统设计

靖固 杨华宇

摘要:采用FPGA和DSP的结构实现实时图像采集处理系统,利用FPGA运行速度快、并行处理能力强的优势,采用“对数拉伸”算法对摄像头采集的数据进行前期预处理,达到图像增强,使得停车场类昏暗光线图像亮度分布不均匀的图像变得清晰;利用DsP具有较强处理复杂算法的优势,对FPGA传送过来的分块图像数据采用JPEG并行压缩算法进行图像的压缩,实验结果表明,图像增强模块能够明显改善图片质量,FPGA和DSP的结构能够很好的满足系统实时性的要求,

关键词:FPGA;DSP;图像采集;图像增强;图像压缩

DOI:10.15938/j.jhust.2016.04.008

中图分类号:TP391.41

文献标志码:A

文章编号:1007-2683(2016)04-0040-05

0引言

随着现代技术的发展和人们对图像采集处理质量需求的不断提升,对图像采集系统的性能和实时性提出了更高的要求,而对于数据量大、噪声干扰严重的图像数据,采用单个DsP芯片难以满足系统的性能和实时性的要求,用FPGA对图像进行预处理并实现对DSP的控制与管理,就可以很好的解决了这类问题,本系统针对停车场类昏暗光线图像,利用FPGA采用零有效视频信号提取算法提取出输入的有效的YUV视频数据,采用对数拉伸增强算法对图像进行预处理,预处理后的图像送入到DSP内采用并行JPEG压缩算法对数据进行压缩,仿真结果表明,图像增强模块使昏暗光线图像明显增强,数据压缩后使信息传输量减少20%,能很好地满足系统实时陛要求,

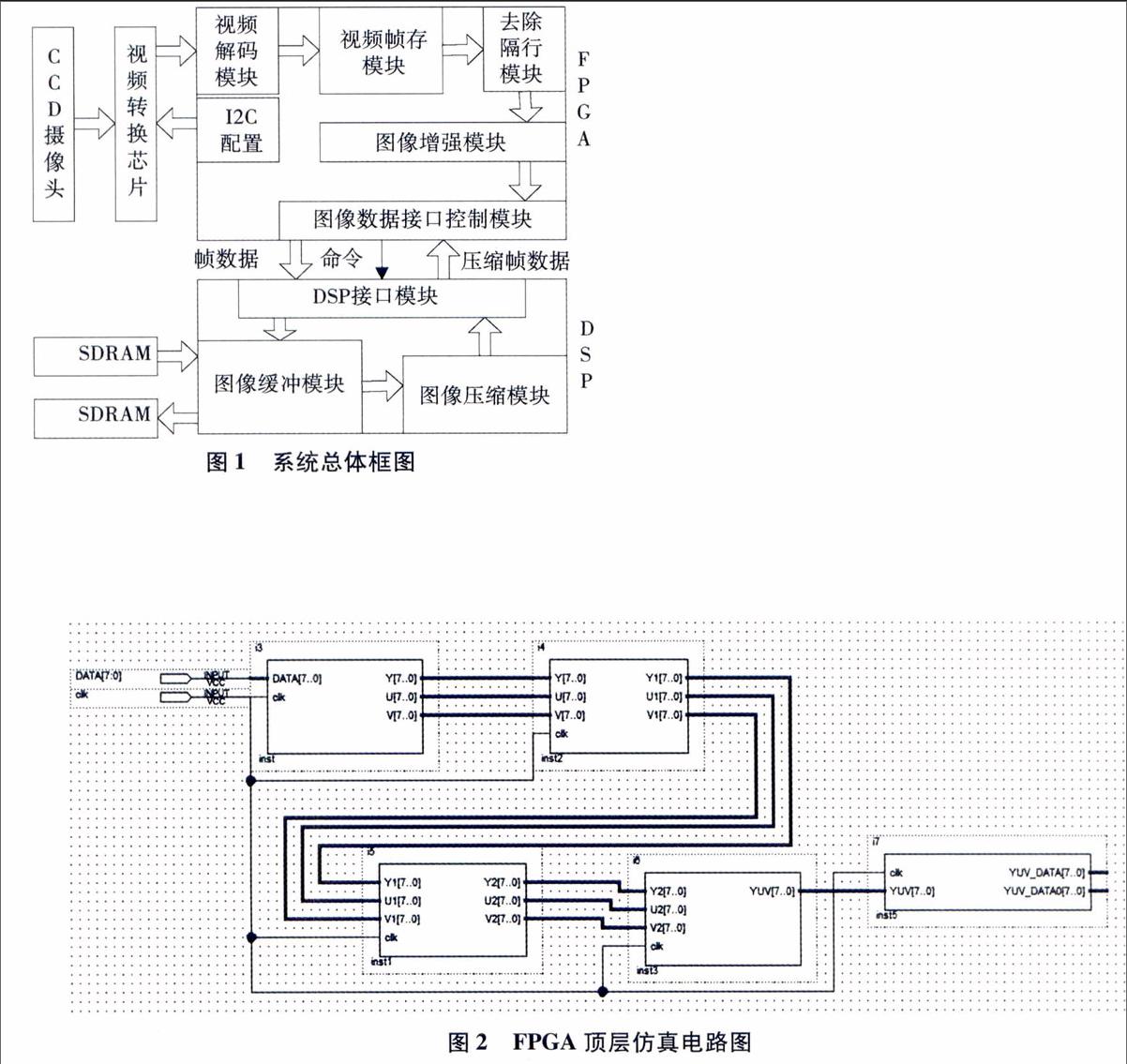

1.实时图像采集处理系统总体结构

系统总体框图如图1所示,系统分为9个模块,FPGA内包含的模块有视频解码模块,12C配置模块,视频帧存模块,去除隔行模块,视频增强模块,DSP接口模块,

DSP芯片内包含的模块有图像数据接口模块,图像数据缓存模块,图像压缩模块,通过CCD摄像头对视频进行采集,图像数据送入视频A/D转换芯

2.1视频解码模块设计

视频解码模块接受模数转换器ADV71781 B的YUV数字信号,这些数字信号中包含有场参考信号VS、行参考信号HS和奇偶场信号,要对YUV信号分别进行处理必须从图像数据中提取出有效的Y、u、V数据,摄像头采集的数据经过ADV7181B转片中,经12C总线对视频A/D转换芯片初始化,完成控制寄存器的配置,使其上电后进人工作模式;A/D转换芯片输出图像送人视频解码模块,视频解码模块接收A/D转换的视频流后对视频流进行解码,产生YUV数据;视频帧存储模块采用乒乓存储算法结构对YUV数据进行存储,使YUV图像数据转化成并行数据;为了增强视频效果,消除抖动闪烁去除隔行模块完成采集图像的奇场帧和偶场帧的合并,由于系统应用于地下车库监控系统,采集的图像数据光线以及灯光等原因图像画面不清晰,通过图像增强模块增强其对比度使图像清晰;增强后的图像数据通过DSP接口模块送入DSP芯片内进行压缩;DSP芯片压缩处理数据量很大,为避免数据丢失,图像数据通过DSP内部的接口模块和图像缓存模块缓存到SDRAM中;缓存一帧图像数据后,在DSP内也采用乒乓读写操作将数据送入压缩模块进行压缩,压缩后数据送回FPGA存储待发送。

2.FPGA内部模块设计

FPGA内部共有5个模块组成,顶层仿真设计电路如图2所示,输人为摄像头采集的复合信号DATA,时钟信号elk,输出为经过处理的视频有效信号和压缩后传回FPGA的YUV_DATA、YUV_DA-TA0信号,换后输出符合ITU—R656的信号DATA,行同步信号HS,帧同步信号VS,DATA的数据格式如图3所示,视频解码模块主要是提取出YUV数据,即将串行的数据转换为并行的YCrCb数据,

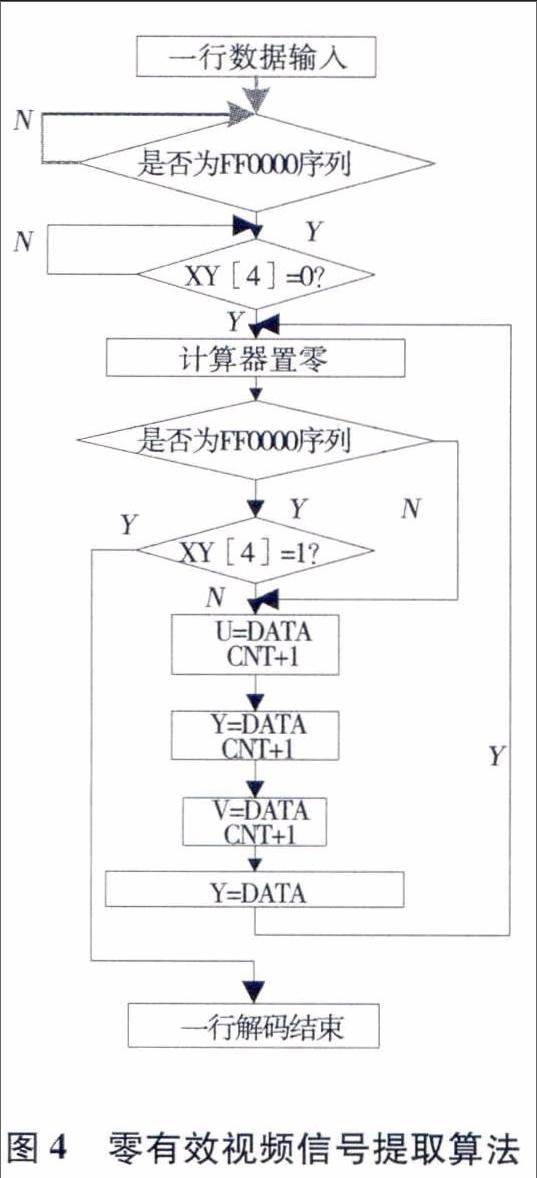

从上图可以看出AV信号都是以“FF0000”作为开始信号,但SAV的XY[4]=0,EAV的XY[4]

1.利用这点我们构造一个检测电路来实现YUV数据的并行输出,视频数据提取算法如图4所示,算法在实现上利用状态机完成对“FF0000'数据流以及SAV、EAV的识别,识别出有效数据后操作设置好的计数器cnt,算法中YUV数据为422格式,当cnt=0时输出Cb,cnt=1时输出Y,cnt=2时输出Cr,cnt=3输出Y,最终得到YUV有效的视频数据,

2.2视频帧存模块设计

视频解码模块输出的YUV信号需要三个缓存器进行缓存,通过软件自带的端口RAM的宏模块把每个缓存定义成双端口的深度均为1024,每个数据端口宽度为8位RAM缓存器,

2.3去除隔行模块设计

去除隔行模块采用帧内复制的方法,具体实现方法就是改变视频帧存模块中双端口RAM的读写时钟,使读时钟是写时钟频率的两倍,这样每行的数据读两遍,隔行数据就变成了逐行数据,

2.4图像增强模块设计

2.4.1图像增强算法

地下车库的灯光相对较暗,往来进出的车辆很多而且都开着大灯,在图像中显示结果为车灯的部分特别亮,使得周围的图像模糊不清,从灰度值方面来说,灰度值为O~125之间和200~255之间的像素特别集中,这时如果直接使用原图,则图中的一部分低灰度细节可能会丢失,由于原图的灰度动态灰度值分布范围不均匀,可能大于显示设备允许的范围,使得原图的一些灰度级显示不出来,为此将地下车库的采集图像做灰度映射,使原图的动态灰度值分布变得均匀,对数形式的压缩算法可以很好地解决此类问题,其原理为:

利用上式可将原来动态范围很大的s转换为动态范围较小的t,从图5中可以看出,大部分低灰度值的像素经过映射后其灰度值会集中到高亮度区段,总体来说就是同时增大图像的亮度,对于原来灰度值小的增亮的幅度大些,原灰度值大的增亮的幅度小些,从而达到图像亮度均匀,细节不模糊的效果,

2.4.2图像增强模块硬件结构设计

图像增强主要针对于亮度信号,也就是YUV信号中的Y路信号,去除隔行模块输出的是YUV三路并行的8位信号,因此在增强模块中还要保证u、V两路信号的同步,为此采用与之前模块同样的方式设置三个宽度为8位,深度为1024的FIFO,增加一个检测电路使三路信号完成并行转换到串行,使输出给接口控制模块的数据为单路8位宽的有效图像数据,从后面仿真对比图可以看出经过图像增强模块后图像对比度明显增强,从图6的a)图可以得出整个处理过程共需O,17 ms,而从b)图可以看出在MATLAB软件上完成的时间为1,7s,

2.5接口控制模块设计

FPGA内部的接口控制模块通过一个时钟锁相环来控制,FPGA和DSP的数据通信接口如图7所示,为了将处理后的视频数据并行处理,采用8个FIFO寄存器将视频数据进行分块,第9个FIFO用来接收DSP送回的压缩数据,视频数据采集、处理完成之后,FPGA通过FIF08的空信号(empty flag)查看8个FIFO中是否数据已满,如果未满,则将数据在写时钟的逻辑控制下,顺序写入到FIFO中;同时将FIF08中满信号连接到DSP的中断引脚,满信号置高,会触发DSP的DMA进程,将寄存器中数据读走,DSP压缩一帧数据完成后通过EMIF接口将数据送回FPGA。

3.DSP内部设计

3.1图像压缩并行算法

为了达到实时性的目的对预处理后的图像进行并行JPEG压缩处理,JPEG压缩编码主要由预处理、DCT变换、量化、Huffman编码等流程构成,如图8所示,

JPEG压缩编码时,需先将原始的二维图像分成8×8的数据块并行处理,然后将各数据块按从左到右,从上到下的顺序分别进行DCT变换、量化、“之”字型(Zig-Zag)扫描和Huffman编码,分别需要量化表和Huffman编码表的支持,将8×8数据块的DCT转换为16次一维8点DCT变换,只要提高一维DCT的速度就可以提高二维DCT的速度,利用DSP的专用指令乘累加运算来优化DCT算法,DCT变换和Huffman编码采用和传统算法一样的实现方法,用C语言和汇编语言在DSP内部实现,

与传统JPEG算法在DSP芯片上实现有所不同的是,在图像压缩模块中并没有进行对二维图像的分块处理,DSP压缩模块接受的是经过FPGA分块处理后的图像数据,DSP在经过缓存后可以直接对其进行后续的压缩处理,这样既提升了整个系统的处理速度,更好的满足实时性,又减少了DSP对存储器的调用,

3.2图像压缩结果

经过DSP芯片压缩后的数据通过与FPGA接口模块传送回FPGA,最终存储或显示出来,由图9(a)(b),可以明显看出比原图像更加清晰,由图9(c)可以看出压缩后尽管有一些失真,但还是保留了原图像的细节,达到了要求,

5.结论

利用FPGA和DSP结构能很好地解决图像采集系统的实时性要求,针对昏暗场所的图像数据采用“对数拉伸”算法,可有效增强图像,使得亮度分布不均匀的图像变得清晰;采用并行JPEG压缩算法在FPGA发送数据前对二维图像进行分块,减少了处理时间;JPEG压缩虽为有损的图像压缩算法,但能使信息传输量大大减少的同时有效地保留原始图像的细节,达到预期处理目的。