基于OVM的可重用自动化验证平台

杨小丽

(西安航空学院 电子工程学院, 陕西 西安 710077)

基于OVM的可重用自动化验证平台

杨小丽

(西安航空学院 电子工程学院, 陕西 西安 710077)

介绍了OVM(Open Verification Methodology)验证方法学的基本概念和技术,从验证环境的体系架构、验证组件的可重用性和验证过程等方面进行详细说明,给出一个使用e语言实现的基于OVM的可重用自动化验证平台的实例。基于OVM的可重用自动化验证平台可提高SoC(System on a chip)功能验证的可重用性、可扩展性和验证效率。

OVM;可重用;验证平台;SoC

0 引言

随着集成电路工艺几何尺寸和电路特性的持续改进,半导体制造商成功的实现了摩尔定律的预期和发展速度,SoC(System on a Chip)设计的规模和复杂度日益增加,导致验证工作的困难呈指数级增长。统计显示,验证占据了超过70%的设计开发周期,是SoC设计开发的主要瓶颈,这就使得验证的方法受到高度重视,验证方法学成为研究的热点。使用先进的验证方法学建立高效的、可重用的自动化验证平台对片上系统设计的成功起着关键作用[1]。

OVM(Open Verification Methodology)验证方法学是Mentor Graphics公司和Cadence公司共同推出的通用、开放源代码的验证方法学,提供了丰富的验证资源和高级的验证技术[2]。应用OVM搭建验证平台可以提高SoC的验证效率。

1 验证平台的搭建方法及特点

功能验证平台的搭建一般有以下几种方法:基于硬件描述语言HDL的传统方法;基于断言的验证方法;基于高级验证语言和验证方法学的方法。

1.1基于硬件描述语言HDL的传统方法

传统方法使用Verilog或VHDL硬件描述语言来构建验证环境,开发测试向量进行仿真。一般来说具有以下特点:针对DUT(Device Under Test)的特定属性,编写大量定向测试用例;由人工来决定验证路径和验证目标,人工检查和判断验证结果。

随着设计复杂度的增加,传统验证方法显现出诸多缺点:

(1)验证平台缺乏层次化,难以重用和扩展,可读性和可维护性差;

(2)需要手动开发大量边缘测试案例;

(3)覆盖率低;

(4)面对复杂设计难以开发强大的验证环境;

(5)排查错误困难,验证效率低等。

1.2基于断言的验证方法

基于断言的验证方法是在设计源码中的关键点插入断言语句,在仿真过程中,由断言语句发现设计优缺点,具有如下优势:

(1)可以提高设计的可观测性,找出传统方法的输出结果难以表现的错误;

(2)快速跟踪错误根源,缩短调试时间;

(3)易于发现设计IP集成过程中出现的问题,提高设计效率;

(4)不需要用户设计复杂的验证环境。

基于上述优点,在今后的设计中插入断言语句将成为一种趋势。但是,也存在一定问题,一般断言是设计者描述的,有可能设计代码和验证代码都是错误的,导致无法发现问题,而且目前的断言不可综合,以后仿真中无法使用。

1.3基于高级验证语言和验证方法学的验证平台

基于验证语言和验证方法学的方法即基于专用验证语言,并在相应的验证方法学的指导下构建验证平台,具有相应工具的支持,可为功能验证的实现提供完整的解决方案。该方法能有效克服传统验证环境的缺点,具有高度的可重用性,并能利用先进的自动化验证技术,大大提高验证效率。

由于硬件描述语言和C语言等传统语言在验证方面的能力不足,难以开发有效的验证环境,于是出现了专门用于验证的高级验证语言,例如,SystemC、SystemVerilog、e语言等。这些高级验证语言都有相应的验证方法学的支持,如SystemVerilog可以基于VMM方法搭建验证平台[3]。目前主流的验证方法学主要有Synopsys公司的RVM、VMM,Mentor公司的AVM,Cadence公司的UVM以及Cadence和Mentor联合推出的OVM等[4]。其中VMM和OVM作为新兴的验证方法学,逐渐取代其他方法学,得到广泛应用。

2 基于OVM的验证环境

2.1OVM简介

OVM(Open Verification Methodology)是一个支持多种验证语言的、开源的方法学和技术[5]。OVM是基于SystemVerilog提出的,在e语言基础上发展起来的一种验证方法学。为了整合资源,适应更复杂的验证需求,Cadence和Mentor联合推出了为多语言而构建的开源方法学OVM,可以将SystemVerilog、e以及SystemC等不同语言所构建的验证环境以及VIP(Verification IP)整合在一起使用。OVM是独立于验证语言的验证方法学。OVM方法学提供了构建可重用验证环境的方法和规范,包含针对每种语言的方法指导、库、例子和培训,指导验证人员进行验证代码的设计、编码和封装,构建可重用的验证组件。下面对OVM的验证环境、验证组件UVCs(universal verification components)、OVM如何实现可重用性和验证自动化作简要介绍。

2.2OVM验证环境

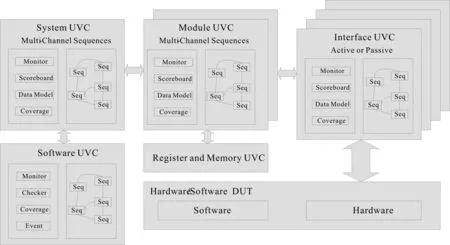

OVM验证环境由可重用验证组件UVCs(universal verification components)组成。对于这些验证组件的组织安排决定了验证环境搭建的质量。OVM对UVCs的结构、封装、配置和术语等制定了一套标准。典型的OVM环境结构如图1所示。

图1典型的OVM环境

由图 1可见,一个典型的OVM环境包括Interface UVCs、 Module UVCs、 System UVCs和Software UVC等。Interface UVC是OVM验证环境最基础的组成模块,Module UVCs可由Interface UVCs和其他需要的组件组成,System UVCs可由Module UVCs和Interface UVCs组成。每个UVC里都包括检查(checking),覆盖率(coverage)的统计和激励序列(sequences)等。

2.3可重用UVCs

UVCs(universal verification components)是OVM验证环境的基本组成模块。每一个UVC都是封装好的可配置的组件。通常有三种类型的UVCs:Interface UVCs、Module UVCs和System UVCs。

Interface UVCs是与DUT的直接接口,通常涉及某个特定的协议,像PCI,TCP/IP,Ethernet等。Interface UVCs通常包括如下元素:

Agents:模拟DUT的顶层文件,与VHDL实现中的实体类似[6]。通过端口(ports)连接到DUT,由Driver,Sequencer和Bus monitor组成。一个UVC可以包含多个agent。Agents可通过配置参数来实现不同的操作模式,可以配置为驱动并监视接口的主动(Active)模式或仅仅监视接口的被动(Passive)模式。

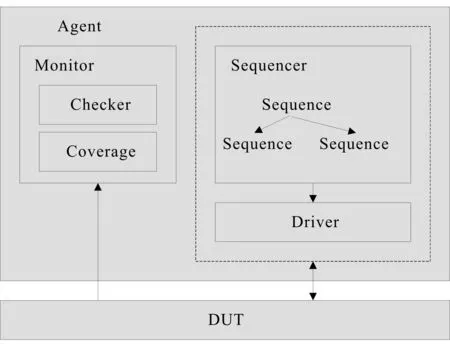

典型的UVC Agent,如图2所示。

图2 UVC Agent

Driver也叫BFM(Bus Function Model):通过驱动和采样DUT信号来与DUT交互,将传递的数据流转换为DUT需要的格式,与总线的功能相似。

Sequencer:产生验证人员希望加载给DUT的激励数据并传给Driver来执行。

Bus monitor:从总线上提取需要监测的信号信息,并转换成其他组件可用的数据结构,同时还控制着检查(checking)和覆盖率的统计。通过监视总线上的信息来进行协议和数据两方面的检查。通过侦测总线传输,数据结构的转化,事件的发生等,来通报coverage进行覆盖率收集。

System UVCs用来对系统进行验证,如CPU、bridge或手机。相关的小系统UVCs称作Module UVCs。System UVCs由Interface UVCs和Module UVCs构成。它可以没有自己的agents,而仅仅实例化其他UVCs,把它们连起来形成一个更大的验证环境,其中Interface UVCs用于连接到系统接口,而Module UVCs是当前验证系统的子模块或子系统。

System UVCs和Interface UVCs的结构相似。它的Monitor从Interface UVCs的monitor处收集信息。Scoreboard收集Monitor采集到的数据送给参考模型进行对比分析。在System UVCs里还定义了Virtual (multiple channel) sequence,它连接到Interface UVCs和Module UVCs的sequence上,可同时控制所有的系统接口。另外多数系统都有寄存器,System UVCs引入vr_ad模型库实现对寄存器的验证。

2.4可重用性

验证占据了芯片开发周期的绝大多数时间,因此,验证的可重用性对于开发效率的提高是至关重要的。OVM验证平台的可重用性主要有下面两方面内容。

(1)UVCs的重用。虽然每个UVC都针对不同的协议、设计,但是UVCs还是有很多共性的,如都包含激励、检查和覆盖率信息等,这些相对固定的结构,便于开发标准UVCs,针对不同设计,只需扩展相应文件即可。

(2)验证环境的重用。高一级的验证环境或组件可通过重用低一级的来实现,例如,模块级的验证环境在系统级的重用,系统级也可以在更大的系统验证环境中重用。

OVM方法学的拓扑结构和配置以及层次性等确保了UVCs以及验证环境的可重用性,使得验证环境搭建的效率极大提高,验证人员可以将更多的时间用于验证过程本身而不是环境的搭建。

2.5验证自动化

覆盖率驱动验证CDV(coverage-Driven Verification)方法已是验证人员所熟悉的一种高效率的验证方法,通过自动化测试向量生成和对覆盖率的测量,CDV可确保验证目标的实现和验证过程自动化。而OVM提供了较好的框架来实现CDV。基于OVM搭建的验证平台可实现CDV方法中的带约束的随机向量的生成,通过Monitor、Coverage和Check,实现由覆盖率驱动的自动化验证过程。

3 验证平台实例

下面给出一个使用e语言实现的基于OVM的可重用自动化验证平台的实例。这里以异步串行通信接口UART为DUT。UART是发送和接收UART帧的SoC外围设备,可以实现全双工通信,将需要发送的总线并行数据转换为串行数据,同时,将接收到的串行数据转换为总线并行数据,其主要接口为APB总线和UART通信接口。

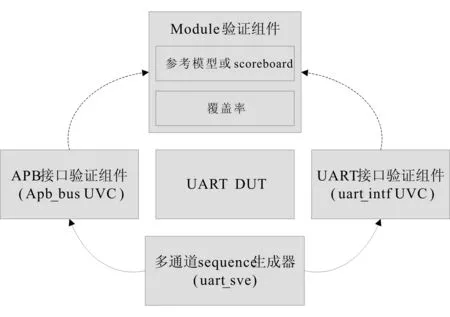

3.1UART验证环境

UART验证环境如图3所示,主要由四部分组成,其中APB UVC、UART UVC和Module UVC三部分文件结构相同,分别负责主机接口,通信接口和模拟DUT本身的工作。而顶层验证环境uart_sve主要是将各个验证组件有效的组织在一起,并实现虚拟sequence进行激励的有效控制。

图3 UART验证环境

3.1.1Interface UVC

UART验证环境中包括两个Interface UVC,分别为APB UVC和UART UVC。APB UVC主要模拟主机对DUT的配置行为,按照APB总线协议访问时序完成对DUT的读写访问。UART UVC为通信端的接口,主要模拟DUT与DUT的通信行为,按照规范和DUT进行通信,相当于在更高层次对DUT的行为模拟。

Interface UVC各个部件都是用e语言中的struct或unit等来实现的。主要部件的实现如下:

(1)Item struct:代表输入到DUT的交互数据,包括数据包,指令等。对于APB UVC主要定义地址、数据和读写等,而对于UART UVC主要定义了按照协议规定的各种传输类型的数据包。

(2)Agent unit:分为active和passive两种子类型,在passive下,只例化了monitor,而在active下,例化了monitor、bfm和sequence driver,除此之外,在agent下可以定义与DUT交互的端口信号。

(3)sequence driver unit:主要是生成数据架构,并且连接bfm,将生成的数据包发送给bfm。

(4)bfm unit:将sequence driver产生的数据包,按照规范要求的访问规则驱动到DUT,同时也检测DUT的响应。

(5)monitor unit:主要负责监测传输。检测总线上的一切活动,接收有效的数据流,并将其转换为抽象级别高的字符。根据规范所定义的字符含义,发出相应的有效事件,这些事件可供bfm引用,同时在接收过程中自动检测数据正确性。

3.1.2Module UVC

Module UVC主要是DUT的代理,负责监测DUT与主机接口和通信接口的交易事务,并且做相应的check和coverage收集。由于使用了寄存器存储器模型(vr_ad),所以该UVC还实现了寄存器文件的定义、例化和寄存器访问的sequence。

3.1.3顶层验证环境

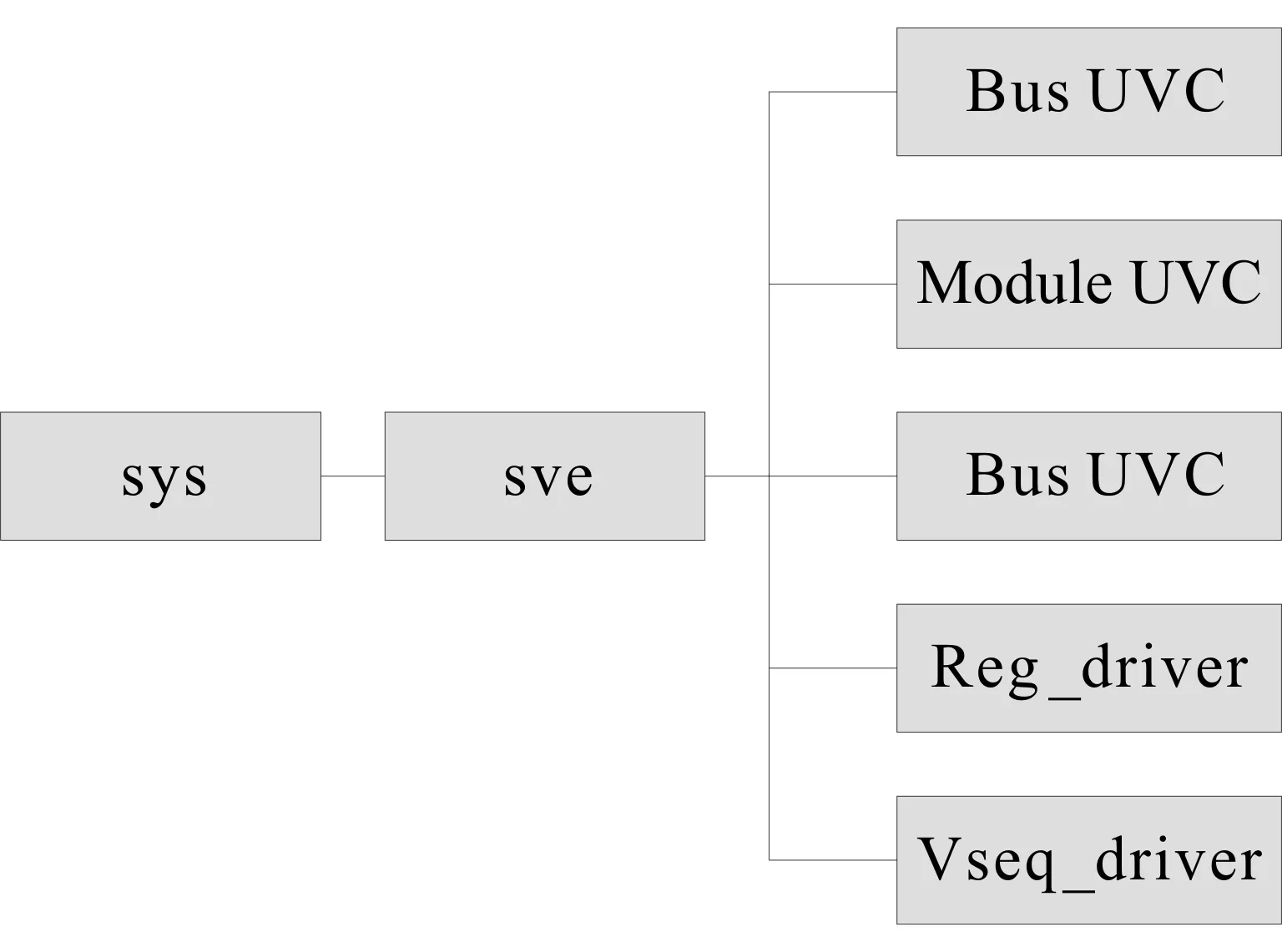

Uart_sve为UART验证的顶层环境,其作用主要是组织三种UVC,并且定义虚拟sequence来调度各种sequence。验证环境的层次如图 4所示。

图4 UART顶层验证环境

3.2UART的验证流程

通过OVM方法学所搭建的UART验证平台,其验证流程如下:

(1)通过APB UVC写寄存器来配置DUT的工作模式;

(2)使用Testcase对DUT产生所需要的测试激励,在APB和UART接口间交互数据;

(3)通过Module UVC检查DUT的功能正确性;

(4)通过Module UVC收集和分析DUT的功能覆盖率;

(5)通过对覆盖率的分析对Testcase进一步完善,补充没有验证到的情况;

(6)重复2~5步,直到功能覆盖率达到100%。

由验证流程可见,OVM方法学所搭建的验证平台可以很方便的实现覆盖率驱动验证,提高验证的自动化程度。

4 结语

本文介绍了基于OVM验证方法学来搭建可重用自动化验证平台的方法,并以UART为例,详细介绍了验证环境各组件的实现方法,该验证环境已成功在多个项目中得到重用,提高了验证效率,保证了验证的可靠性。

[1] Rashinkar P,Paterson P,Sinagh L.系统芯片(SOC)验证方法学与技术[M].北京:电子工业出版社:2005.

[2] 蔡金池.基于OVM架构的网络数据包随机序列构建与产生[J].电脑知识与技术,2010,6(34):9678-9680.

[3] 肖庚亮.基于VMM的SoC可重用验证平台设计[J].科学技术与工程,2010,10(5):1149-1152.

[4] 高红霞.基于高级验证语言的IP验证方法[D].西安:西安电子科技大学,2012.

[5] 何萌.高抽象层次化的OVM验证平台设计[D].西安:西安电子科技大学,2014.

[6] 文良,靳荣利,吴龙胜,等.基于AHB总线接口的可重用性验证环境的实现[J].微电子学与计算机,2011,28(7):202-204.

[责任编辑、校对:东艳]

Reusable and Automatic Verification Platform Based on OVM

YANGXiao-li

(School of Electronic Engineering,Xi'an Aeronautical University,Xi'an 710077,China)

The basic concept and technology of OVM (Open Verification Methodology)are introduced in this paper.It elaborates the verification environment architecture,the reusability of verification components and the process of verification.An application example of reusable and automatic verification platform based on OVM and e language is offered.This kind of methodology is proved to be very useful to improve reusability,extendibility and efficiency of SoC functional verification.

OVM;reusable;verification platform;SoC

2016-09-01

杨小丽(1981-),女,陕西渭南人,工程师,主要从事信息技术方面的研究。

TN407

A

1008-9233(2016)05-0060-05