基于STILLink平台的测试向量转换研究*

张晓羽 顾 颖 杨士宁

(航天科工防御技术研究试验中心 北京 100854)

基于STILLink平台的测试向量转换研究*

张晓羽顾颖杨士宁

(航天科工防御技术研究试验中心北京100854)

STILLink平台是以STIL语言为核心的测试向量转换平台,支持多种格式的相互转换方案。STILLink平台的多种转换方案,大大缩短了从设计、流片到测试的全过程。STIL语言提供了一种数字测试生成工具与测试系统之间的接口,宗旨为寻求一种数字测试信息从测试生成工具到测试系统的转换方案。在论文中,将以电平转换器SY100ELT24为例,重点介绍WGL格式文件转换成STIL格式文件的方法,以及STIL格式文件向V93000测试程序的转换过程。

测试向量转换; STILLink; STIL; WGL; V93000

Class NumberTP312

1 STIL语言概述

集成电路设计的规模和复杂性不断增加,用于测试芯片的测试向量[1]变得非常庞大,同时测试时序设计需考虑多种因素,从而导致测试开发工作困难程度大大增加。一般来说,自动化测试设备(ATE)[2]不能直接使用EDA产生的仿真向量,需要通过转换得到可识别的测试向量,测试向量转换已经成为测试程序开发的重要环节[3],起到节约成本和缩短时间的作用。

STIL是联系集成电路设计端和测试端的通用接口语言。在前端设计、后端仿真、测试数据产生等方面,不同的集成电路制造商拥有各自的流程及相对固定的数据格式。然而并没有建立一个统一标准用以实现各种仿真数据与ATE的测试数据间的相互转换,但是STIL语言的出现使得这一过程变得简单快捷[3~5]。所有EDA工具都能通过使用STIL语言转换到各种ATE上进行测试,标准化的流程带来很多益处:缩短从设计到测试的整个周期;减少中间环节并且降低由于标准不统一而引发错误或不兼容的可能性;扩大可测试性设计的使用范围[4]。

现今STIL已广泛应用于日本和欧美等集成电路行业发达国家。在日本,以东芝为首的集成电路制造巨头正在积极推动STIL成为行业标准。在美国,英特尔、德州仪器、飞思卡尔等公司在集成电路设计到测试过程中已经采用STIL作为标准数据格式。此外,一些有关STIL的产品已开始使用,如Synopsys公司的TetraMAX、Mentor公司的FastScan与Cadence Encounter Test[4]。

STIL的IEEE标准1450-1999包括以下三个部分[4,6]: 1) EDA到ATE的大容量数字信号的测试向量文件的转换。 2) 定义数字信号的测试向量所对应的被测元器件、format、timing和pattern。 3) 产生结构测试的向量文件,比如SCAN、BIST等。

2 STIL语言的数据结构

STIL语言的数据结构是以块为单位的,每一种特定的数据类型都被定义在相同类型的数据结构块内。该数据格式主要包含文件说明块、信号组块、信号块、时间定时组、测试图形块、信号组与信号关系块、信号与定时关系块及测试向量与定时关系块,如图1所示。每个定义模块之间按树形层次展开,同一层的模块之间是或的关系。因此,该结构会非常清晰,易于转换和分析。下面将对这些模块进行详细说明[7]。

图1 层次结构

1) 文件说明块:由文件名、文件类型和向量总时间长度等总体描述性信息组成。文件可以是各种仿真格式文件和测试图形程序。文件类型包含事件型向量和周期型向量。

2) 信号组块:根据不同条件对信号进行分组,包含组号和组名。总线信号一般以组的形式存在。

3) 信号块:由信号说明块、信号组与信号关系块、信号与定时关系块组成。信号与定时关系块对每个定时组包含的信号名称进行定义,并且规定了每个信号中输入的驱动前沿、输入的驱动后沿、输出的响应前沿、输出的响应后沿、输入的驱动高阻起始时间、输入的驱动高阻结束时间及输入的波形调制格式。信号与定时关系块和时间定时组块能够有效解决多时序问题。

4) 时间定时组块:包括定时组号、组名与测试周期等元素。面向事件型向量,时间定时组块可省略。

5) 测试图形块:由块说明信息、测试图形符号类别、测试向量及测试向量与定时关系块组成。面向事件型向量,信号波形跳变数值与时间被连续存储于测试图形块中。而对于周期型向量,定时组号与测试向量按周期被连续存储于测试图形块中。

3 STILLink平台及转换工具

STILLink平台为以色列Test Insight公司以STIL语言为核心的测试向量转换平台。它支持多种格式的相互转换方案,VCD格式、WGL格式向STIL格式的转换,STIL格式向Test Bench的转换,93000测试程序文件格式向Test Bench的转换,各种ATE测试程序文件向STIL格式的转换等。STILLink平台的多种转换工具大大缩短了从设计、流片到测试的全过程。

WGL属于数据描述语言的一种,通过描述扫描的结构、状态,及测试图形的时序和数值来支持器件内的硬件扫描结构与测试程序的生成,既可以实现变量定义和内嵌方程表达式,又能够使用二进制格式取代ASCII图形数据表示[7]。WGLSTIL转换工具[8]将WGL文件转换为以时间周期为驱动格式的STIL文件。该转换工具的输入文件是WGL文件,输出文件为STIL文件。WGLSTIL转换工具通过参数命令行或通过设置控制参数,或者两个结合的方式执行转换过程。

ATEGen转换工具[9]提供从STIL文件格式转换成多种目标测试系统文件格式的转换流程,大大降低了转换的复杂程度。ATEGen转换工具作为STILLink软件平台的一部分,需要与目标测试系统的ATE工具包一起使用。目前ATEGen支持的目标测试系统包括[10]:Advantest公司的T2000和T66XX系列测试系统,Credence公司的Sapphire D10测试系统,LTX公司的enVision测试系统,Nextest公司的Magnum测试系统,Teradyne公司的Catalyst和J750测试系统,Verigy公司的93000和V50测试系统。

4 转换方案设计及实现

本单位具备将VCD格式、WGL格式以及STIL格式等仿真向量转换为Verigy公司93000测试系统的测试程序的能力。本文的转换方案是通过STILLink软件平台将WGL文件转换成Verigy公司的93000测试系统的测试程序。其中,电平转换器SY100ELT24的WGL文件名称为simple.wgl文件大小为10KB。

在STILLink软件平台启动服务器,同时在操作系统上运行DOS命令行,启动WGLSTIL转换工具。WGLSTIL转换工具具有以下几种典型命令,分别为

· -template:生成配置文档模板,包含所有可选配置参数。

· -setup:指定生成配置文档模板的路径。

· -stil_project_directory:指定生成STIL输出文件的文件名称。

在本文中,通过参数命令行的方式执行WGL文件向STIL文件的转换过程,控制参数均使用默认值。

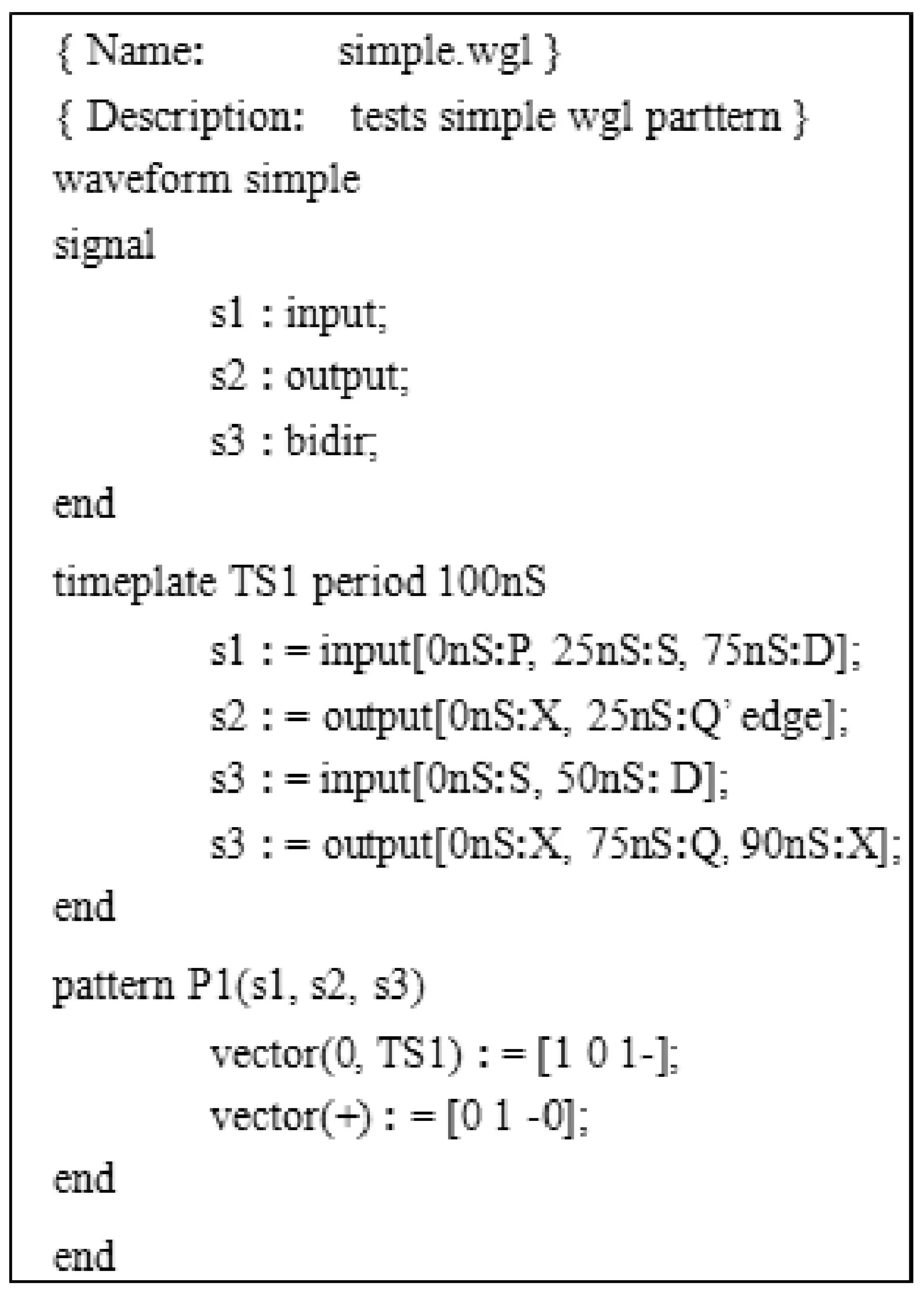

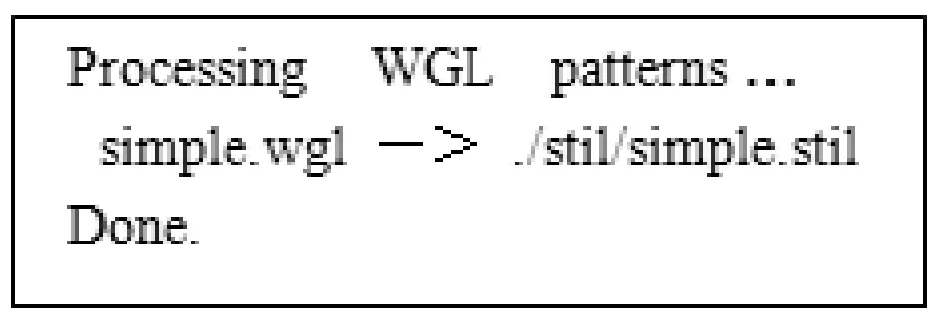

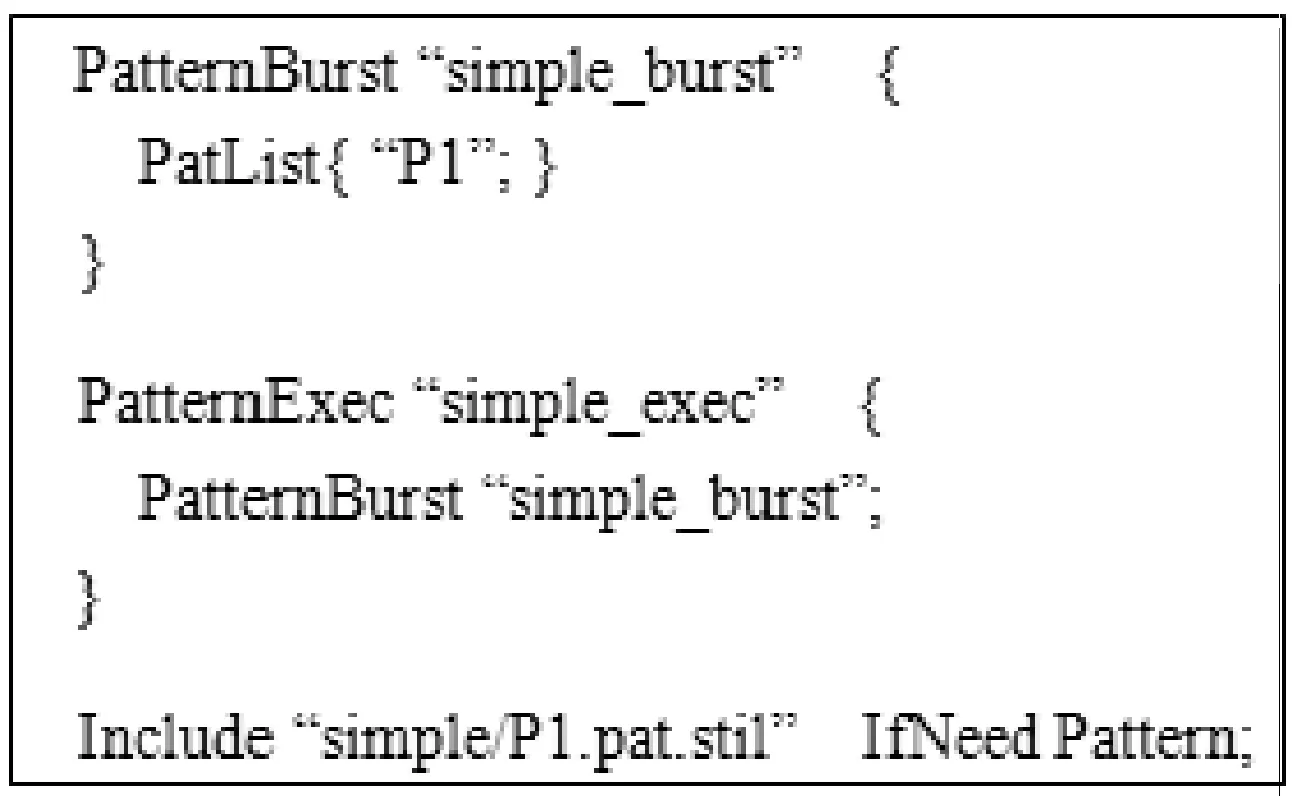

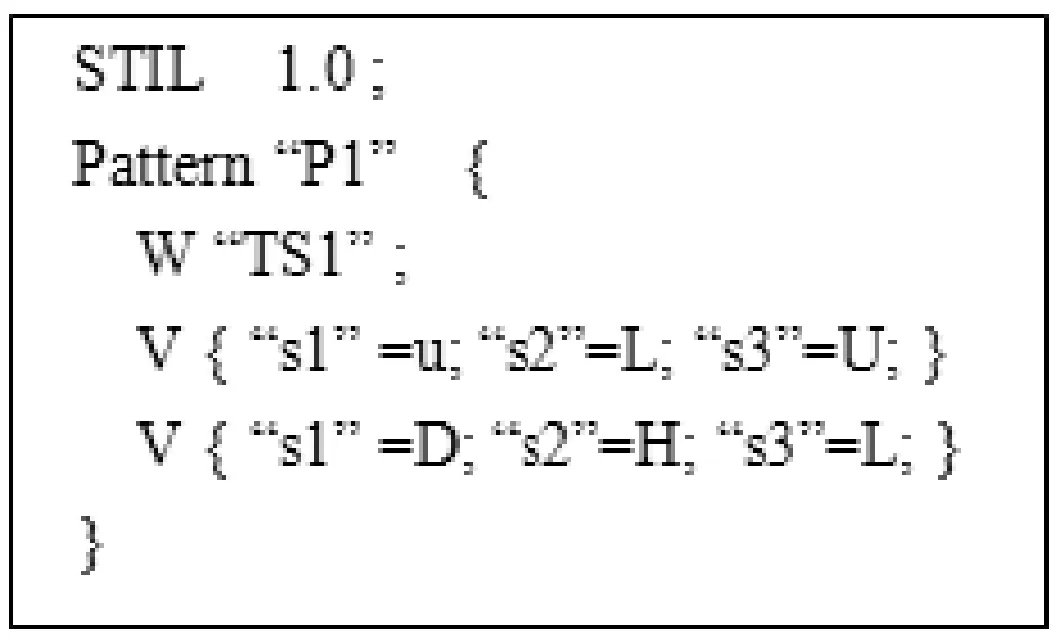

首先将simple.wgl文件拷贝至STILLink平台的bin文件夹里,然后在DOS命令行内键入如下命令将把simple.wgl文件中的所有信号定义等相关信息输出到stil文件和pattern stil文件。生成的simple.stil文件被存于stil文件夹中,而生成的P1.pat.stil文件所在目录为stil/simple/P1.pat.stil。图2为simple.wgl文件,图3为转换工具处理的过程,图4~6为生成的simple.stil文件,图7为生成的P1.pat.stil文件。

>wglstil simple.wgl

图2 simple.wgl文件

图3 转换工具的处理过程

图4 生成的simple.stil文件(信号部分)

图5 生成的simple.stil文件(时序部分)

图6 生成的simple.stil文件(测试图形部分)

图7 生成的P1.pat.stil文件

在操作系统上运行DOS命令行,启动ATEGen转换工具。ATEGen转换工具具有以下几种典型命令,分别为

· -debug:生成调试用的中间STIL文件。

· -target:指定目标ATE的名称。

· -workdir:指定生成测试程序文件的文件名称。

· -unify_periods:运用预处理以使不同波形的周期一致。

接着将stil文件夹中全部内容拷贝至STILLink平台的bin文件夹里,最后在DOS命令行内键入如下命令将生成的simple.stil文件转换成Verigy公司的93000测试系统的测试程序文件,图8给出了STIL文件格式到93000测试系统文件格式的转换过程。

>ategen -target 93000SD simple.stil -workdir 93k_output

5 结语

自动测试设备软硬件平台的通用性是目前测试领域研究的热点之一。通用ATE技术的最终目标是集成电路检测项目的软硬件具有独立性,使得硬件接口板与测试程序具备通用性和可移植性。STIL作为EDA-ATE间的标准接口,集成电路产业链各环节为其设计和开发新的工具及产品。STILLink软件平台提供了设计与测试之间的桥梁,实现了设计与测试相融合发展方向,加快了数字电路从设计、流片到测试的全过程。

图8 STIL文件格式到93000测试系统文件格式的转换过程

[1] 张俊,袁云华.一种FLEX系列FPGA测试建模方案[J].计算机与数字工程,2015(1):113-116.

ZHANG Jun, YUAN Yunhua. A FLEX Series FPGA Test Modeling Scheme[J]. Computer & Digital Engineering,2015(1):113-116.

[2] 胡勇,李轩冕,贺志容.单片机测试向量生成技术研究[J].计算机与数字工程,2010,38(9):90-92.

HU Yong, LI Xuanmian, HE Zhirong. Test Pattern Generating Technology Research for Microcontroler[J]. Computer & Digital Engineering,2010,38(9):90-92.

[3] 陈辉.ATE测试向量转换方法研究[D].广州:华南理工大学,2010.

CHEN Hui. The Research of ATE Test Vector Conversion Method[D]. Guangzhou: South China University of Technology,2010.

[4] 孙亚春.STIL——ATE与EDA之间的桥梁[J].中国集成电路,2010,133(6):70-72.

SUN Yachun. STIL-The Bridge Between ATE and EDA[J]. China Integrated Circuit,2010,133(6):70-72.

[5] 杨大为,钟宏伟.集成电路测试程序的移植与建库[J].微处理机,2008,29(3):43-44.

YANG Dawei, ZHONG Hongwei. The Transplant and Build-library of IC Test Program[J]. Microprocessors,2008,29(3):43-44.

[6] “Standard Test Interface Language (STIL) for Digital Test Vector Data”[S]. IEEE International Standard, (IEEE Std 1450),2007.

[7] 吴明行.芯片的测试向量转换技术研究与系统实现[D].中国科学院研究生院,2006.

WU Mingxing. Research and Realization on IC Test Vector Automatic Translation[D]. Wuhan: Graduate University of Chinese Academy of Sciences,2006.

[8] “WGLSTIL Manual Application Notes”, Test Insight, Aug,2010.

[9] “ATEGen Tutorial Application Notes”, Test Insight, Aug,2010.

[10] “ATEGen Manual Application Notes”, Test Insight, Aug,2010.

Test Pattern Transformation Based on STILLink Platform

ZHANG XiaoyuGU YingYANG Shining

(China Aerospace Science & Industry Corp Defense Technology R&T Center, Beijing100854)

STILLink is a test pattern transformation platform based on STIL language, which supports the method of multi-format data conversion. STILLink platform can greatly shorten the whole process from design, tape-out to testing. STIL language provides an interface between digital production tools and testing system, and its aim is to seek a method of digital test information transformation from test generation tools to test system. In this paper, the level translator SY100ELT24 is taken as an example. The emphasis of this paper is on the file conversion method from WGL format to STIL format and the conversion process from STIL format to V93000 test program.

test pattern transformation, STILLink, STIL, WGL, V93000

2016年3月7日,

2016年4月28日

张晓羽,女,博士,工程师,研究方向:测试向量转换技术。顾颖,女,高级工程师,研究方向:集成电路测试技术。 杨士宁,男,工程师,研究方向:集成电路测试技术。

TP312DOI:10.3969/j.issn.1672-9722.2016.09.021