电子战中的基带雷达信号源设计

白 玉,杨斌斌,杨承志,王 龙

(1.沈阳航空航天大学电子信息学院,辽宁 沈阳 110136;2.空军航空大学信息对抗系,吉林 长春 130022)

电子战中的基带雷达信号源设计

白玉1,杨斌斌1,杨承志2,王 龙2

(1.沈阳航空航天大学电子信息学院,辽宁 沈阳 110136;2.空军航空大学信息对抗系,吉林 长春 130022)

现代战争中部队信息化作战的能力已经成为战争成败的关键因素,构建高逼真度的基带雷达信号源对于电子战的指挥与训练具有重要意义。研究了一种基于FPGA基带雷达信号源的设计。首先在上位机开发应用程序,对FPGA进行参数配置,然后研究了DDS产生信号的原理,将关键的信号产生模块封装成AXI总线接口的IP核,增强了设计的灵活性和重用性,最后结合一片高速D/A芯片进行数模转换,完成了基带雷达信号源的设计。利用频谱仪测试了信号源的性能指标,实测表明整体设计符合电子战中对雷达系统的应用需求。

电子战;FPGA;IP核;DDS;高速D/A芯片

0 引言

战场电磁环境的复杂性日益加剧,要求现代雷达不仅要具有良好的目标识别与超近程的探测能力,还要具备极高的距离分辨率和很强的抗干扰性能,这就要求雷达的发射信号要具备大的带宽。用数字方法产生宽带雷达信号,无论在频率、幅度以及信号的信噪比等方面均优于模拟方法,且具有精度高、外围电路简单等优点。目前使用数字方式产生信号主要通过直接数字频率合成(DDS)法[1]实现。例如文献[2~3]采用DDS的思想,分别介绍了使用可编程器件CPLD和FPGA控制DDS专用芯片来产生线性调频信号。文献[4]利用FPGA提供的知识产权IP核资源,在FPGA芯片中调用多个DDS IP核来产生波形信号。

本文在上述文献设计的基础上,提出基于FPGA的专用IP核的设计思想,将关键的信号产生模块封装成AXI总线结构的IP核,提高了模块的灵活性、易用性和重用性,直接调用多个IP核来产生多路特定参数相关的信号,再通过并串转换技术将其合成一路信号,最后借助ADI公司的高速D/A芯片AD9129进行数模转换,完成基带信号源的设计。

1 系统原理介绍

1.1基于DDS的信号产生原理

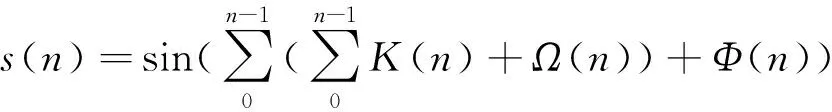

DDS是直接数字频率合成技术的简称,它是一种基于相位累加结构的信号产生系统,与其它频率合成方法相比,它具有输出频率相对带宽较宽,频率转换时间短,分辨率高,可编程,全数字化等一系列优点。DDS芯片主要包括相位累加器、波形查找表、数模转换器、低通滤波器等构成。本文根据需求,结合DDS的原理,设计了具有二阶相位累加结构的DDS模块,如图1所示。并将其封装为AXI总线结构的IP核,在FPGA中调用该IP核来产生所需的雷达信号。雷达信号的一般表达式为:

(1)

式中,A(t)表示信号的时域包络,f(t)为信号的频率调制函数,φ(t)为信号的相位偏移调制函数。对式(1)作离散化,可得其离散形式如式(2)所示:

(2)

式中,K(n)为n时刻的调频斜率,Ω(n)为n时刻的频率偏移,Φ(n)为n时刻的相位偏移。通过控制这3个量,即可输出单载频信号、线性调频和相位编码等调制形式的雷达信号。

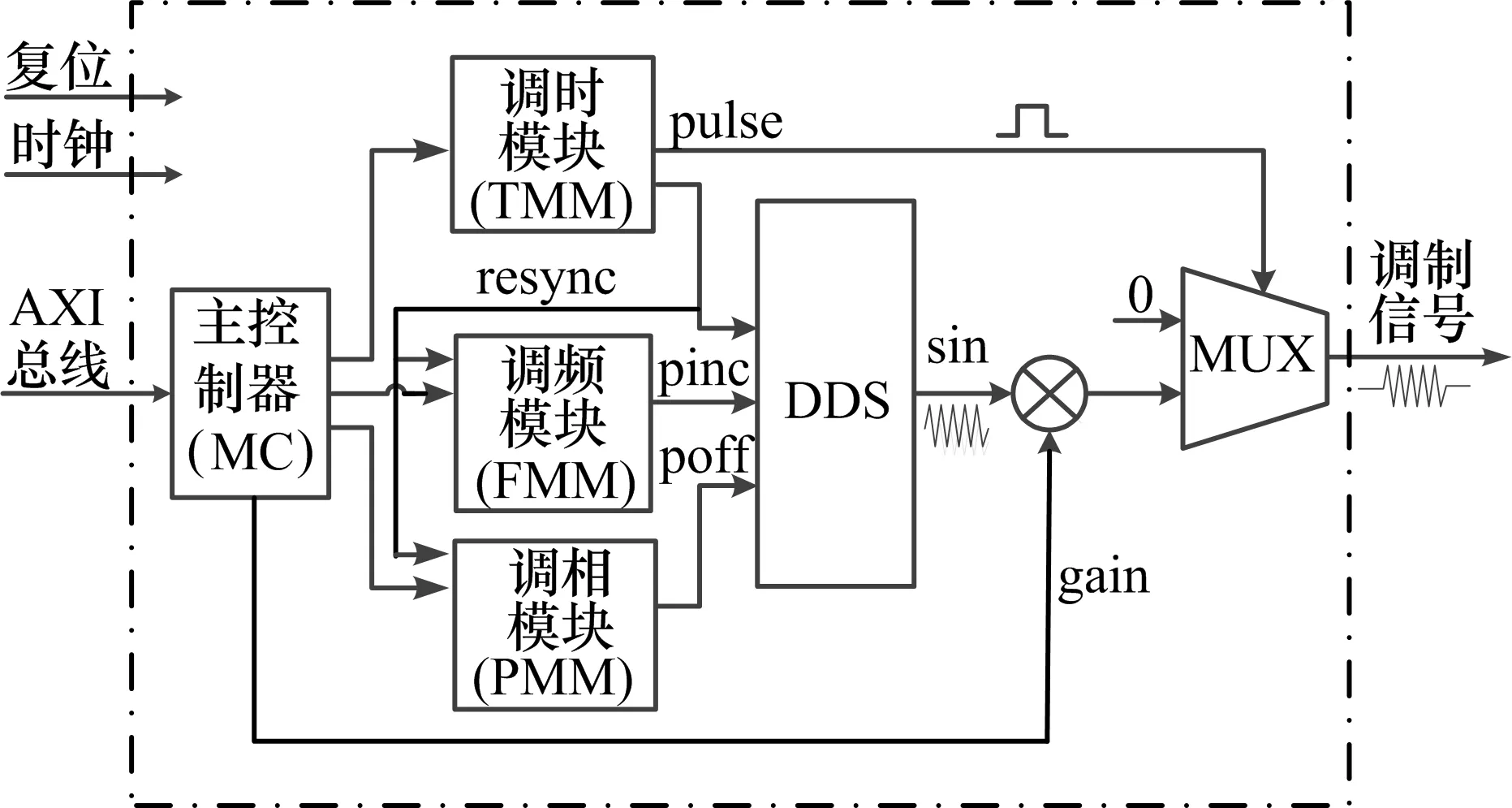

图1 DDS 模块结构原理框图

从表达式(1)中可以看出,雷达信号的调制方式不外乎幅度调制、频率调制、相位调制、时间调制这四种或这四种调制方式的组合,幅度调制常见的是矩形脉冲调制。本文中将设计的信号源划分为时间调制模块(TMM)、频率调制模块(FMM)和相位调制模块(PMM)这3个模块,每个模块分别负责产生时域调制控制信号、频域调制控制信号和相位调制控制信号。通过这3个子模块来控制DDS IP核以输出各种调制类型的信号,并将该顶层模块再次封装为AXI总线结构的IP核。该信号产生单元IP核的顶层结构如图2所示。

图2 信号产生单元IP核的结构框图

1.2信号源的工作原理

为了使雷达系统达到极高的距离分辨力和很强的抗干扰性能,要求基带雷达信号源的输出信号具备大带宽,本设计要求输出信号的瞬时带宽1000 MHz,输出频率范围介于50~1000MHz之间。这就要求DA芯片的采样速率至少在2000MHz以上,设计中选用了ADI公司具有14位DAC量化的高性能数模转换芯片AD9129,其实时采样率可高达2.8GHz。但FPGA无法在如此高的频率下工作,故采用8个信号产生单元IP核来产生一路基带雷达信号,这样每个信号产生单元的工作时钟便降低为350MHz。以宽带线性调频信号(WLFM)为例,假设需要输出的WLFM信号脉宽为τ,带宽为Β,重复周期为T,起始频率为f0,初相为φ0,调频斜率k为B/τ。则每个信号产生单元IP核的调频斜率均相等,均为k,即:

(3)

设每路信号生成单元的初始频率和初始相位分别为fn和φn:

(4)

(5)

为输出能够符合设计要求的WLFM信号,在FPGA中例化8个信号产生IP核,每个IP核的参数可根据式(3)~(5)进行配置。由8个IP核来产生信号,最后通过多通道的并串转换技术,即可得到所需要的基带雷达信号。

2 系统方案设计

2.1总体方案介绍

本文设计的基带雷达信号源的整体结构如图3所示。

整个系统由上位机软件部分和硬件部分组成,软件控制界面通过在上位机Visual Studio 2012环境中编程实现,该软件将需要生成的基带雷达信号的配置参数通过PCI-e总线传输给FPGA中的参数配置模块,该模块按照式(3)~(5)解析需要生成信号的参数,给8个信号产生单元IP核进行参数配置以产生信号,在FPGA中将8个IP核产生的信号进行并串转换,即可合成一路输出频率高达2.8GHz的信号,最后经由DAC芯片进行数模转换,可得到所需要的基带雷达信号。

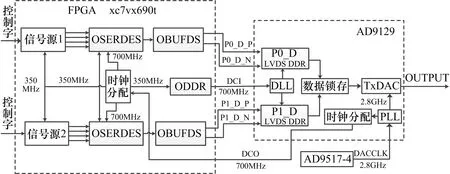

2.2硬件设计

本设计硬件系统的整体结构,由一块Xilinx公司高性能FPGA芯片xc7vx690t和一块ADI公司高速D/A芯片AD9129,再加一块时钟芯片组成。在xc7vx690t中生成了两个信号源产生模块,每个模块内含4个信号生成单元,这些单元均工作在350MHz的频率下,利用FPGA中提供的并串转换(OSERDES)资源进行多路并串转换,将8路信号合成两路并行的单端信号,两路单端信号经过单端转差分(OBUFDS)后转化为两对频率均为700MHz的差分信号。AD9129在700MHz的数据输入时钟DCI的驱动下,分别从P0_D和P1_D两个端口使用DDR模式来采集FPGA送过来的两对差分信号,采样后的信号被送至数据锁存器,在外部时钟芯片提供的2.8 GHz时钟ADCCLK的驱动下,TxDAC核最终将锁存器中的数据转换为一路模拟信号进行输出。上述工作过程如图4所示。

AD9129使用的时钟ADCCLK由ADI公司的时钟芯AD9517-4提供。由其提供的2.8 GHz的时钟经由ADCCLK输入到AD9129后,一路送至TxDAC核去驱动其进行高速数模转换,一路送至其内部的时钟管理单元[5]。时钟管理单元输出一对700 MHz的差分信号DCO到FPGA,FPGA内部再使用分频模块将DCO 2分频作为8个信号生成单元的驱动时钟,同时FPGA产生同DCO同频的DCI,DCI作为D/A的数据输入时钟,送至AD9129。

2.3主要芯片介绍

本文选用的D/A芯片是ADI公司的AD9129[6],它是一块具有14位DAC量化的高性能数模转换芯片,其具有双端口接口和双倍数据速率,以及低压差分信号接口,可支持2.85GSPS的最大转换速率。根据配置信息的不同,AD9129可工作在不同的工作方式下。其配置方式有两种,一种是通过引脚来配置,另一种是通过SPI串行接口来配置。SPI串行接口配置方式通过SPI串行总线向芯片内部寄存器写入配置信息,该方式实现虽然复杂一点,但配置灵活,便于后期修改。本文中通过SPI配置方式,将AD9129配置为双端口传输数据,且每个端口采用双倍时钟速率(DDR)来采集数据,即在DCI的上升沿和下降沿同时采集数据,这样AD9129的数据时钟的频率就降为芯片时钟的1/4,降低时钟的传输频率就意味着可以提高时钟的质量,也可以提高数据传输的正确率。

2.4软件设计

在本设计中,使用上位机软件对FPGA进行参数配置,上位机软件在Visual Studio 2012环境中使用C++语言编程实现,其通过PCI-e总线与FPGA进行通信,当启动该软件后,软件将自动接管系统控制权,在软件上对相应的参数进行配置后,点击发送按键,即可在DAC输出端得到所需要的WLFM信号。其配置界面如图5所示。

图4 硬件系统结构图

图5 上位机软件配置界面

3 验证与测试

3.1Matlab仿真验证

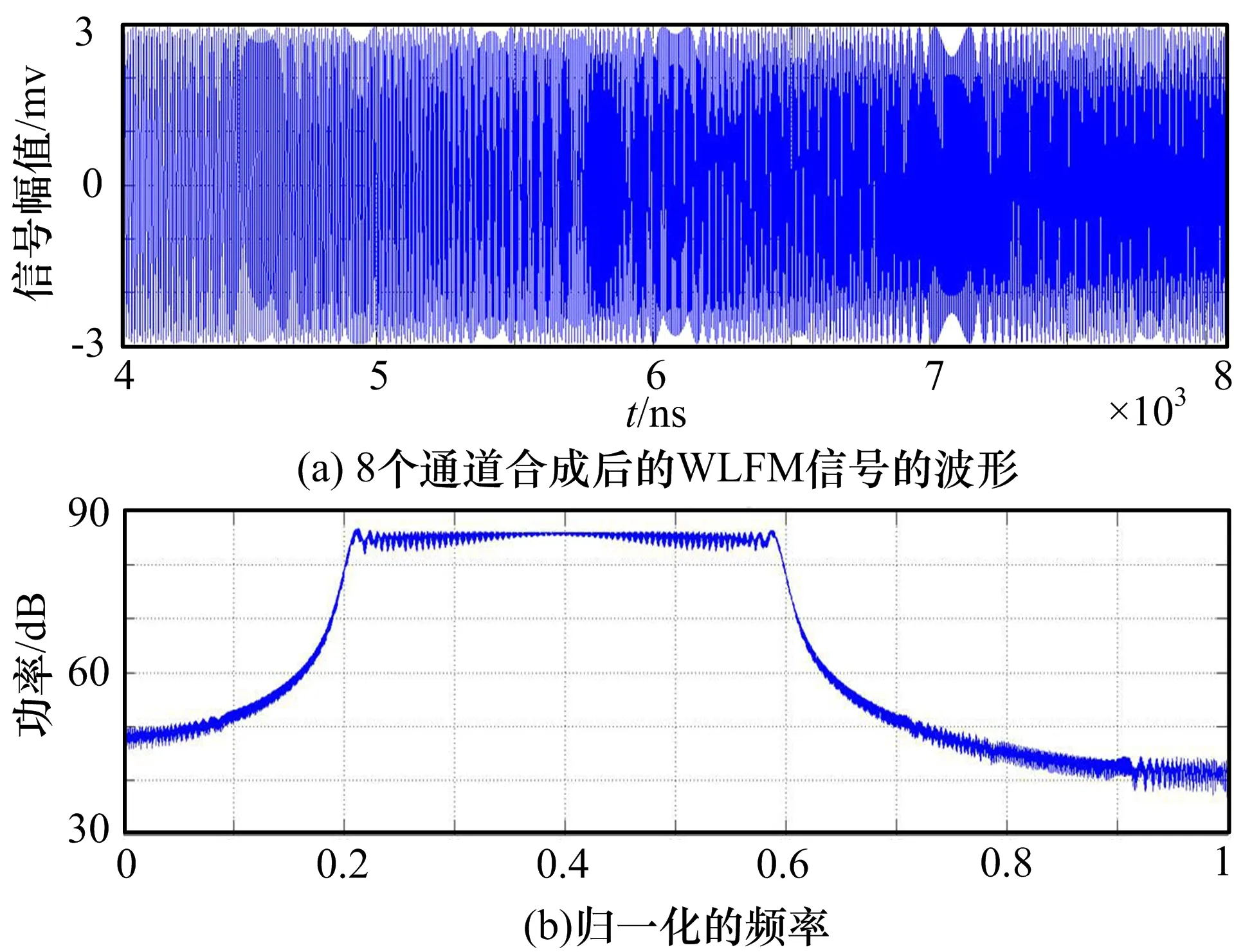

本设计提出了在FPGA中生成多个信号生成单元来产生WLFM信号。为了验证方案的可行性,使用Matlab对该方案进行了仿真验证。通过计算及仿真,得到每个信号生成单元的配置参数,具体的仿真结果如图6所示。

图6 合成后的WLFM信号及其频谱

在图6中,上部分是将8个通道的信号合成一路信号后的WLFM信号的输出波形,下部分是仿真得到的其频谱图。经对比,合成后的信号与直接使用WLFM信号公式得到的波形数据相吻合,故而本设计提出的利用8个通道的低频信号来合成一路高频信号的方案完全可行。

3.2系统测试与分析

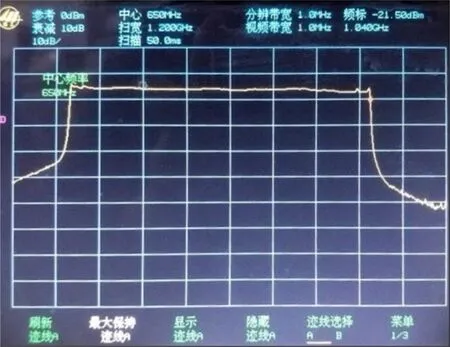

本文对设计后的系统进行了成果验证,当设置起始频率为150MHz,终止频率1050 MHz,初始相位为0Rad,重复周期为100μs,脉冲宽度为100μs时,实测得到WLFM信号的频谱如图7所示。

图7 实测LFM信号的频谱

在未滤波的情况下,从实验截图可看出,输出信号的频谱在1GHz左右,带内平坦度约为3dB。实测观察到信号源输出频率范围介于DC~1400MHz。可见,本设计实现的宽带信号源达到了设计指标要求,满足实际工程需求。

4 结束语

本文针对目前雷达发射信号带宽较窄与频率较低的问题,选用了目前最高性能FPGA芯片和最具性价比的高速D/A芯片,在FPGA中将关键的信号产生模块封装为AXI总线结构的IP核,并利用其产生信号,通过高速D/A进行数模转换,设计并实现了带宽与频率分别可达1GHz和1400 MHz的宽带基带雷达信号源。实验表明,该设计对输出信号的带宽与频率均有了较大的提升,为提高雷达发射信号的性能提供了新的思路。■

[1]Lee PS, Lee CS, Ju HL. Development of FPGA-based digital signal processing system for radiation spectroscopy[J]. Radiation Measurements, 2013,48(1):12-17.

[2]Aguirre MP, Calvino L, Valla MI. Multilevel current-source inverter withFPGA[J]. IEEE Trans. on Industrial Electronics,2013,60(1):3-10.

[3]彭昭,胡进峰. 基于FPGA的直接数字频率合成器的优化设计[J]. 电子世界, 2012,16(18):108,133.

[4]柳春,甘泉. 基于FPGA的雷达信号源设计[J]. 电子技术应用,2013,39(11):47-49.

[5]唐大伟,吴琼之. 基于高速D/A AD9739 2.5GSPS的宽带信号源[J]. 电子设计工程,2013,21(20):45-47.

[6]ADI Corporation. AD9129 datasheet[EB/OL]. [2013-03-21]http://www.analog.com.

The design of baseband radar signal source of electronic warfare

Bai Yu1, Yang Binbin1, Yang Chengzhi2, Wang Long2

(1.School of Electronic and Information,Shenyang Aerospace University,Shenyang 110136,Liaoning,China; 2.Department of Electronic Countermeasures,Aviation University of Air Force,Changchun 130022,Jilin,China)

In the modern war, the ability of information warfare capability has become a key factor to win the war, to construct a high realistic radar signal source is of great significance for the command and training of electronic warfare.A method of baseband radar signal source based on FPGA is studied. In order to configure the parameters of FPGA, a software is developed on the host computer firstly, then the principle to generate signal by DDS is studied. Meanwhile the key signal generating module is encapsulated into the IP core of the AXI bus interface which will enhance the flexibility and reusability of the design. In the end, combined with a high-speed D/A chip to do digital to analog conversion, the design of baseband radar signal source is finished. With the spectrum analyzer, the performance of the signal source is tested, the result indicates that the design can meet the applications requirements of radar.

electronic warfare;FPGA;IP core;DDS;high-speed D/A chip

2016-03-21;2016-06-23修回。

白玉(1969-),女,副教授,硕士,主要研究方向为嵌入式系统。

TN974

A