基于CH368芯片的PCIE总线控制卡设计

陈 昕,杨秋实

(装甲兵工程学院,北京,100072)

基于CH368芯片的PCIE总线控制卡设计

陈 昕,杨秋实

(装甲兵工程学院,北京,100072)

基于CH368芯片设计了PCI Express总线接口电路,将串行传输模式转换为相对简易的并行传输模式。通过动态链接库编译和上位机软件设计,为使用CH368控制PCI Express总线提供了底层技术支持。控制卡有多通道输入及输出,可以满足数字信号、模拟信号的传输检测。

PCI Express;CH368;总线;控制卡

0 引言

尽管PCI总线取得了巨大的成功,但是随着处理器主频和数据带宽等需求的不断提高,PCI总线已无法跟上发展的需求。在微机等系统中已经逐渐被第三代I/O总线PCI Express(以下简称PCIE)所取代,PCIE总线性能优良、价格低廉,PCIE1.0、2.0、3.0标准的理想传输速率分别可达2.5Gbps、5.0Gbps、8Gbps,备受广大用户关注。PCIE规范较复杂,开发PCIe总线板卡的难度较大。

目前常用的开发方案有两种: 一种是利用FPGA实现PCIe总线的时序,同时可实现其它应用功能,开发难度较大;另一种相对容易实现,是利用PCIe桥接芯片。本文以实际控制卡的部分功能为例,说明如何使用桥接芯片CH368设计PCIe总线控制卡。

1 系统总体设计

由于PCIE总线是串行总线、协议复杂,不便于与测量、控制逻辑电路直接连接,需要经过一个PCIE接口控制器作为桥梁,在此选用CH368芯片来实现。CH368是北京沁恒普华电子研制的一款连接PCI Express总线的通用接口芯片,支持I/O端口映射、存储器映射、扩展ROM以及中断。

在CH368一侧是PCIE总线,另一侧是本地并行总线。通过双向驱动芯片提高数据总线的负载能力,地址、控制总线通过译码电路后控制各数据通道进行数据传输。本控制卡设计有模拟信号和数字信号的IO接口,以满足相关信号的输入输出要求。系统原理框图如图1所示:

图1 .系统原理图

2 系统电路设计

CH368对PCIE总线的各种信号进行译码后,产生内部数据总线D31~D0,本电路仅需要其中D0~D7的8位并行数据接口,挂接数据总线进行数据交换,D8~D31数据口悬空不使用。A0~A13为地址线接口,提供地址信号。IO_RD和IO_WR分别控制I/O端口的读选通和写选通。SCL、SDA引脚和配置芯片24C02连接,用于读取控制卡的识别信息。

由于CH368负载能力有限,本设计选用74LS245作为负载芯片,提供外扩芯片足够的驱动能力。74HC574和74HC541接于74LS245后方,分别作为输出锁存和输入缓冲单元。在模拟量采集和输出部分,考虑到电路连接的方便,决定选取8位接口芯片,同时具备12位数据转换能力。

电路的译码选用GAL22V10芯片。在I/O读写操作期间,CH368的A5~A0输出I/O端口的偏移地址,GAL22V10进一步对A0~A5进行译码后产生相应控制信号,由于MAX197和AD7837均为8接口12位数据模式芯片,所以在对相应芯片进行I/O读写操作时需要按照由低位到高位的顺序进行,同时MAX197还需遵循先完成锁存器A或锁存器B的数据传输后才能对另一个锁存器进行读写操作。

3 软件设计

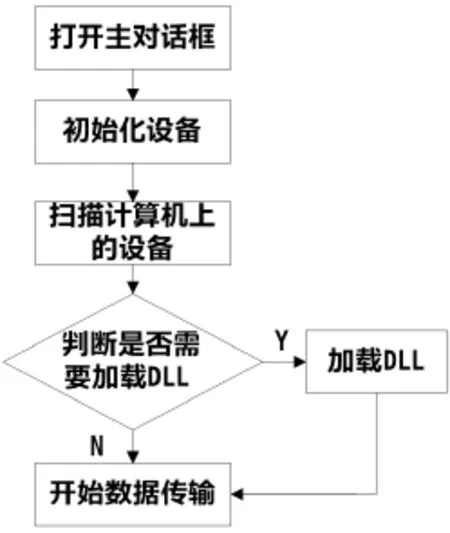

图2 .上层软件设计流程图

本设计采用动态链接库的形式,将Windows的API函数和I/O读写指令的访问和操作封装成一个DLL。该DLL包含:定义PCI Express配置空间数据结构,CH368芯片I/O空间配置,CH368芯片存储器空间配置,定义WIN32命令接口结构,寄存器的位定义,应用层接口的功能代码等。上层软件的开发流程图如图2所示:

4 结束语

PCI Express是第三代高性能IO总线,在总线结构上采取了根本性的变革,最新的PCI Express3.0接口已经达到8GB/s的传输速率,。但是PCI Express总线的开发具有一定难度,利用CH368芯片可以将其转换为简便易用的8位或32位的主动并行接口,降低了PCI Express总线的计算机板卡开发难度和成本。本控制卡支持数字信号和模拟信号的传输,具有灵活、通用、便携的特点,适应多种场合的检测。

[1]陈竞艺.谈计算机总线[J]. 邢台师范高专学报,2002(2):55-56.

[2]马鸣锦,朱剑冰,何红旗,等,PCI,PCI-X和PCI Express的原理及体系结构[M].北京:清华大学出版社,2007:29-36.

[3] 沁恒电子,CH368手册(一)[EB/OL].http://wch.cn

[4]张显才,郑庄武,张爱元等.基于PCI总线与CPLD的光栅尺细分采集系统[M].长春:长春理工大学,2009.

Design of PCIE bus control card based on CH368 chip

Chen Xin,Yang Qiushi

(Academy of Armed Force Engineering,Beijing,100072,China)

Designed PCI Express bus interface circuit based on CH368 chip and the serial transmission mode is converted to a relatively simple parallel transmission mode. Providing the underlying technical support for the use of PCI control Express CH368 bus through the dynamic link library compilering and host computer software design.The control card has multi-channel input and output, and can be used to detect the digital signals and analog signals.

PCI Express;CH368;Bus;Control Card

TN492

B

陈昕(1963-),男,河南信阳人,学士,副教授,研究方向:军用光电系统.