High Linearity Full-Differential Fourth-Order ΣΔ Interface ASIC for Micromachined Accelerometer*

LIU Yuntao,ZHAO Shuang,SHAO Lei(College of Information and Communication Engineering,Harbin Engineering University,Harbin 150001,China)

High Linearity Full-Differential Fourth-Order ΣΔ Interface ASIC for Micromachined Accelerometer*

LIU Yuntao*,ZHAO Shuang,SHAO Lei

(College of Information and Communication Engineering,Harbin Engineering University,Harbin 150001,China)

A full-differential four-order sigma-delta(ΣΔ)interface ASIC for capacitive micromachined accelerome⁃ter is presented to reduce quantization noise,switch charge injection,common mode disturbance of substrate noise and harmonic distortion.An effective simple full-bridge equilibrium architecture was brought forward to reduce the disturbance induced by the variation of common mode voltage of operational amplifier,when the driving signal alter⁃nating.To enhance the linearity of system,bilateral static force feedback was employed.Charge integrator,full-dif⁃ferential lead compensator,second-order integrator etc.were designed.The circuit was fabricated in 0.5 μm two met⁃al two poly n-well CMOS technology.The tested results indicated that the closed-loop noise density was 75 μg/Hz1/2,sensitivity was 1.32 V/gn,nonlinearity was 0.085%and the power dissipation was 40mW.All these properties met the design requirement of micromachined accelerometer.

micromachined accelerometer;high linearity;full-differentia sigma-delta

加速度计是一种可以将加速度物理信号转化成能够测量的电信号的仪器,具有μg水平高精度加速度计被广泛应用于导航、制导、空间微重力测量,以及自动化工业中[1]。当前很多惯性传感器的应用要用到计算机、微处理器和其他的一些数字器件,为了能够在数字领域处理信号,有必要将模数转换与传感器信号处理电路集成在同一个芯片上,集成的数字传感器不仅提供了更多的功能,而且降低了整个系统的成本。随着MEMS技术的发展,ΣΔ调制技术被引入到微机械加速度计设计中,微机械ΣΔ调制器结构简单,可以提供直接的数字输出,采用一位数字反馈可以大大降低静电力非线性问题[2]。微加速度计的敏感结构可以作为一个二阶ΣΔ调制器使用,然而由于敏感结构部分非常低的直流增益,使得二阶结构很难实现低的量化噪声[3]。高阶结构是降低系统量化噪声最有效的途径[4]。

由于敏感结构为三端器件,即两个固定电极和作为输出的中间可变电极,因此当前普遍采用单端检测方式对该输出信号进行处理,其优点是结构简单、控制时钟少,反馈易于实现,其缺点是零点漂移比较严重,驱动信号噪声对输出影响比较严重。事实上,也可将两个固定电极作为敏感结构的输出,采用全差分检测电路对信号进行处理,这样可以减小开关电荷注入和衬底噪声产生的共模干扰,提高电源抑制比,减小谐波失真。Lemkin M较早提出了一种差分结构的ΣΔ加速度计[5],但仅利用敏感单元自身的二阶低通特性作为积分器,量化噪声很大,无法得到高精度检测。Kulah H等提出了一种二阶ΣΔ加速度计前端电路[6],该电路中采用了固定参考电容与敏感电容一起构成平衡式全桥电路,虽然也只利用敏感单元完成ΣΔ调制,但却大大提高了系统噪声水平。但该电路的不足之处是参考电容需要外接调整,不利于批量生产。本文将介绍一种高线性度的单环全差分四阶ΣΔ微加速度计接口ASIC,采用四阶调制,降低系统噪声,同时采用本文提出的双侧反馈结构,提高系统线性度。

1 系统方案设计

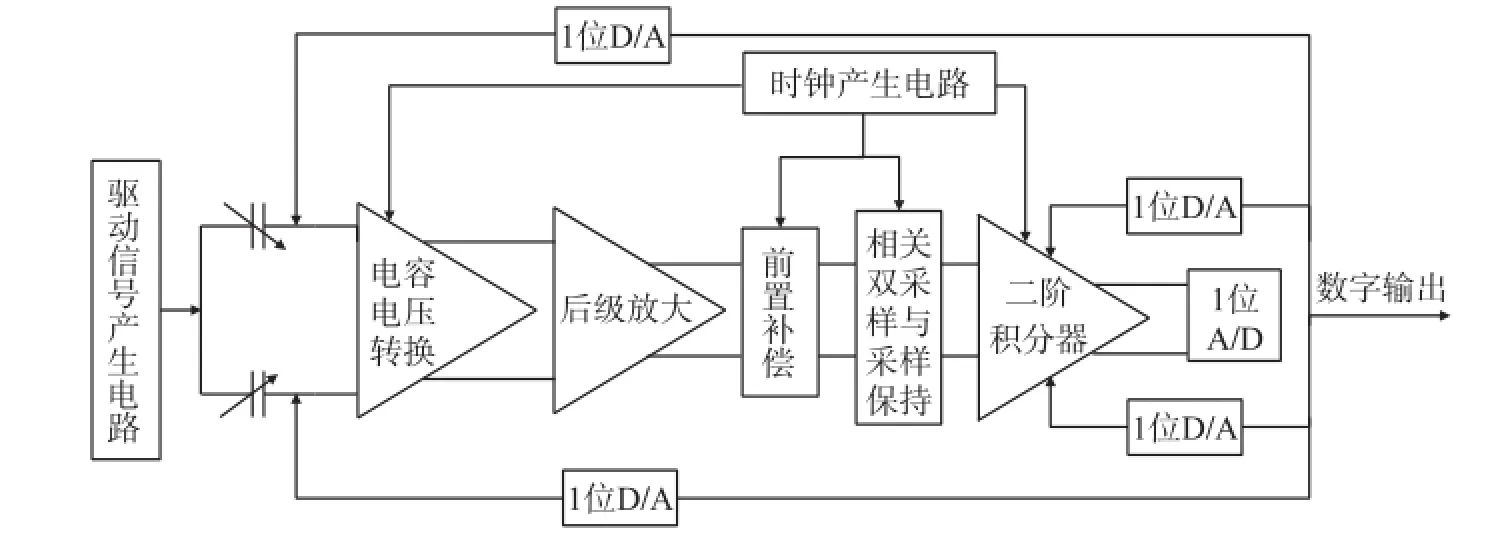

本文所设计的四阶全差分ΣΔ微机械加速度计整体结构如图1所示。该电路主要包括驱动信号产生电路、电容-电压转换电路、后级放大、前置补偿器、二阶开关电容积分器、量化器、D/A转换以及时钟信号产生电路。机械结构作为一个二阶积分器,与二阶开关电容积分器构成四阶ΣΔ微机械加速度计系统。高频驱动信号施加在敏感质量块,两固定电极既作为传感器输出也作为反馈执行器,利用全差分电荷积分器完成电容-电压转换,对该输出信号进一步放大后,送入前置补偿器,通过相关双采样滤除低频噪声及运放失调,然后通过二阶开关电容积分器提供更好的量化噪声整形,电路中存在两个反馈,一个用于电学积分器反馈,一个用于静电力反馈。

图1 全差分四阶ΣΔ加速度计整体结构

2 电路实现

2.1全差分电荷积分器

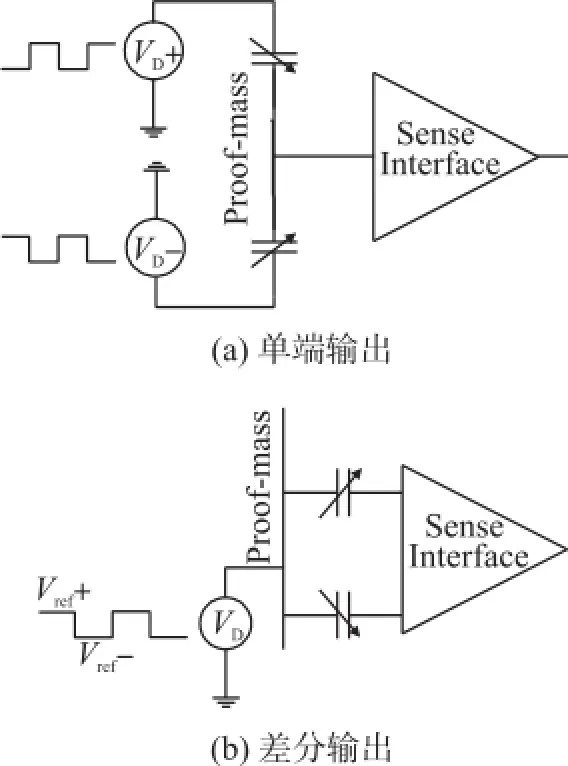

电荷积分器将敏感结构的机械变化转化为电压输出,以供后续电路处理,因此电荷积分器的性能对系统性能至关重要。电荷积分器由驱动信号产生电路和电容-电压转换电路组成,该电路与机械的敏感结构直接相连。图2为电容式加速度计敏感单元与接口电路配置方案,(a)为单端输出,高频驱动信号加载在两固定电极上,中间可变电极作为输出。通过互换固定电极与可变电极角色,该结构还可实现差分输出方式,(b)为差分输出方案,高频方波信号施加在敏感结构的中间电极,两固定电极连接在差分检测电路输入端。以上两种结构都称为半桥结构。

采用图2(b)所示配置方案的差分接口电路的一个主要问题是:驱动信号在Vref+和Vref-之间变化时,所产生的运放输入共模的变化,结果导致转移到两积分电容电荷出现误差,对输出造成影响。该电荷误差可由下式表示:

式中:ΔCS为差分电容变化量,ΔVicm为共模电压变化量。电荷误差对输出造成的影响为:

图2 敏感单元与接口电路配置方案

除此之外,输入共模变化对运放提出了更为严格的要求,运放必须具有非常宽的输入共模范围和非常高的共模抑制比,防止输入共模变化导致的输出误差。另外,高频驱动信号幅值要很小,以维持运放输入信号在其共模范围内。

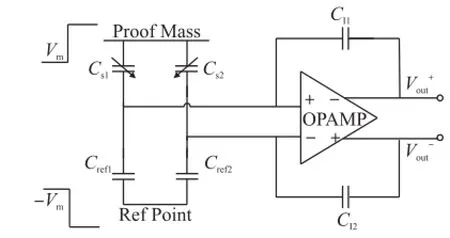

为解决输入共模变化带来的问题,可以在运放输入端加入输入共模反馈电路,通过两个固定电容反馈共模电压,构成了全桥结构的输入共模反馈方法。但该方法增加了电路复杂度、导致功耗和面积的增加。还可以通过合理配置电路工作时序,使采样相位时,输出与输入短接,利用输出共模反馈电路维持输入共模电压,避免了输入共模反馈电路的使用[7]。该方法对信号在一个周期内一次采样,不能有效地消除噪声和失调。为解决输入共模变化带来的问题,本文提出了一种更为有效,更为简单的全桥结构:直接在参考电容公共端接入与敏感质量块反相的激励电压,使得驱动信号变化对输入共模干扰相互抵消,该方法的原理如图3所示。

图3 输入共模漂移消除方案

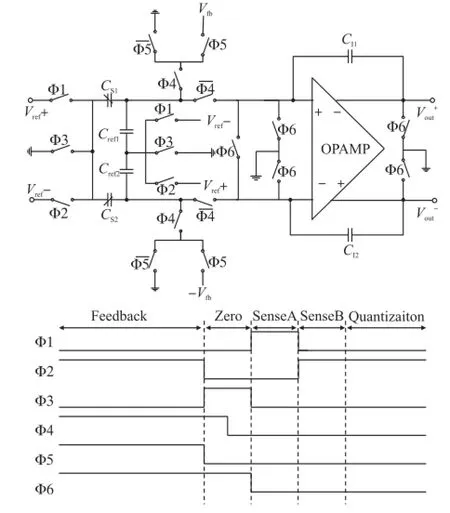

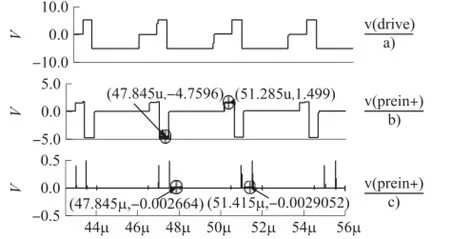

采用上述方法设计的全差分电荷积分器如图4所示,在该图中同时考虑了电路的反馈部分。一个时钟周期内电路工作分为5个相位:清零相位,感应相位A,感应相位B,量化相位,反馈相位。控制时钟及各相位关系也列于图4中。

清零相位:反馈结束后,Φ3变为高电平,敏感结构的中间电极连接在0电位,此时Φ4仍然为高电平,两固定电极也连接在0电位,两个可变电容及两个参考电容电荷都变为0。之后Φ4变为低电平,运放输入端与两固定电极连接,准备下个相位的信号检测。

感应相位A:Φ3、Φ6变为低电平,Φ1变为高电平,两个可变电容的中间电极接在Vref+,两个固定电极接在运放的输入端,两个参考电容的中间电极接Vref-。此时积分器输出包括代表加速度信号的电压及清零相位产生的误差Verror,该输出存储在后级的采样保持电路的电容CH上。

图4 全差分电荷积分器

感应相位B:Φ1变为低电平,Φ2变为高电平,参考电压Vref-施加在可变电容中间极板,输出信号与感应相位A存储在电容CH上的电压相减,由于两个相位采样的误差相等,因此误差被消除,信号变为两倍。

量化相位:输出通过量化器产生数字输出。

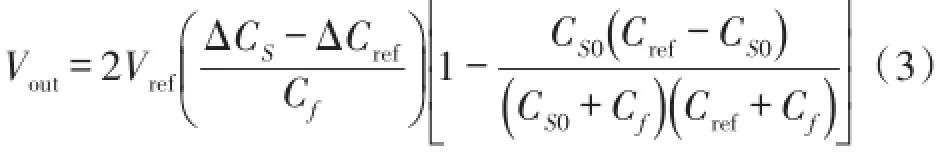

反馈相位:Φ4、Φ5变为高电平,根据量化器的输出判断施加在两固定电极反馈电压是Vfb还是-Vfb,此时由于Φ2处于高电平,活动电极连接在Vref-,在两个固定电极与活动电极之间形成了不相等的静电力,拉动质量块回到平衡位置。考虑电容之间失配,该电荷积分器的输出

由该式可知,输出电压中有两项误差:一项是由于参考电容之间的失配引起的,另一项由参考电容与敏感电容的失配引入。要消除这两个误差,需要满足Cref1=Cref2=C0,版图设计中采用共质心设计,可以实现参考电容之间的高度匹配,但微机械加工中敏感电容波动较大,很难实现参考电容与其相等[8]。该误差可以通过后级的相关双采样予以消除。全差分运算放大器是电荷积分器中最关键的部分,要求具有低噪声,较大的带宽,较高转换速率,大的输出摆幅及高的共模抑制比(CMRR)[9]。

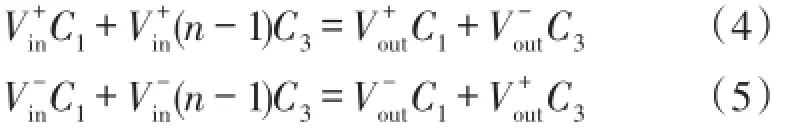

2.2全差分前置补偿器

采用两个单端前置补偿电路可以构成差分补偿器,但作为差分形式,这种结构有两个问题,首先是两个补偿电路分别对输出Vout+和Vout-处理造成的共模变化,其次是电路对称性差,容易造成输出误差[10]。因此本文采用了文献6中的全差分前置补偿电路,如图5所示,对应的工作时序也列于图中。

根据电荷守恒原理,由图中第一和第二采样与电荷转移相电荷分别相等可得式(4)和(5)。

以上两式相减可得

该电路具有与前置补偿一样的传输函数,补偿系数由电容C3与C1比例决定。

图5 全差分前置补偿器

2.3高线性静电力反馈

单端结构中,根据量化器的输出判断反馈回活动电极的电压时Vfb还是-Vfb,在正负驱动信号作用下,形成与惯性力相反的静电合力[11-12]。与单端结构不同,差分结构中,驱动信号施加在活动电极,因此只能将反馈电压加载在固定电极。通常采用的方式如图6(a)所示,反馈时,活动电极接地,两固定极板一个接反馈电压Vfb,另一个也接在0电位,形成与惯性力相反的静电力Ffb

由上式可知,活动电极所受静电合力与反馈电压为二次方关系,降低了系统线性度。为改善上述问题,本文设计了一种双侧静电力反馈方式,如图6(b)所示。反馈时,活动电极接负电源电压VSS,在两极板上分别施加反馈电压Vfb和-Vfb,因此,质量块所受静电合力为:

由此可见,该方式提高了系统线性度。反馈时,也可将活动电极连接在正电源电压VCC上,此时,只要将反馈回固定电极的电压互换即可。

3 结果与讨论

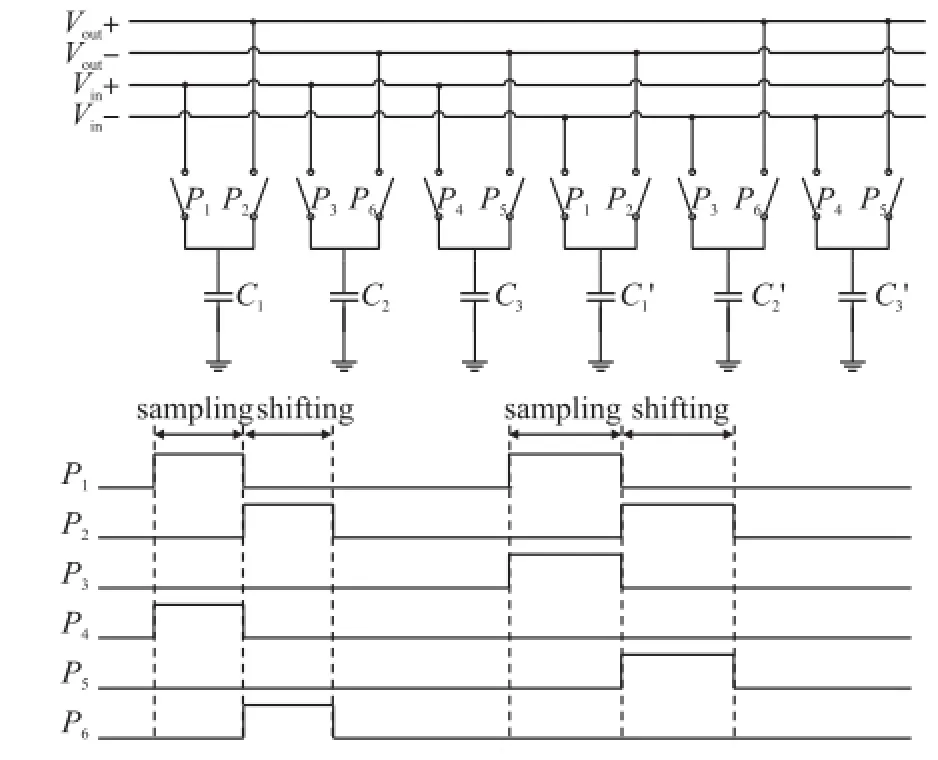

使用Hspice工具对整体电路进行仿真,图7为加入全桥平衡电路模块前后运放输入端的仿真结果,图7(a)为加载在活动质量块上的驱动信号,图7(b)为半桥结构的运放输入波形,图7(c)为引入本文所采用的全桥平衡模块后的运放输入波形。由该结果可见,在半桥结构中,随着驱动信号的变化,运放的输入共模电压发生了严重的跳变,而引入全桥模块后,输入共模变化小于3 mV,保持了输入共模的稳定。图7(c)中的尖峰信号,是由于平衡电桥控制开关电荷注入和平衡电桥对应两两之间的延迟造成的,这些尖峰比较小,并不影响电路功能。

图7 前级运放输入电压仿真结果

该电路采用0.5 μm两层金属两层多晶n阱CMOS工艺流片,芯片照片如图8所示,芯片面积为4.7 mm×3.7 mm,共包含43个Pad点,一部分为电路的输入输出端点,另一部分为电路中各模块测试所需,电路工作在±5V电源电压下,功耗为40 mW。将传感器敏感结构单元与信号处理ASIC芯片双片集成在PCB板上,构成双片集成的微加速度计系统。通过超声压焊法,以硅铝丝作为外引线,将芯片和敏感结构与PCB板上的Pad点相连接,通过PCB板的引脚连接外部测试设备,对传感器进行测试。

图8 ASIC芯片照片

为测试微加速度计的闭环噪声特性,在0 gn状态下,利用数据采集卡对输出数据进行采样,采样过程由比较器的时钟信号触发。并利用Matlab对采样数据进行后处理,图9为65 536点FFT分析结果。由该结果可以看到,在信号带宽内噪声水平约为-80 dBV/Hz1/2,等效噪声为100 μV/Hz1/2。在1位数字输出后接模拟滤波器,得到模拟输出量,并对传感器进行1 gn翻滚实验,可得闭环加速度计的灵敏度为1.32 V/gn,因此,该加速度计的闭环噪声为75 μg/Hz1/2。

图9 数字输出的频谱图

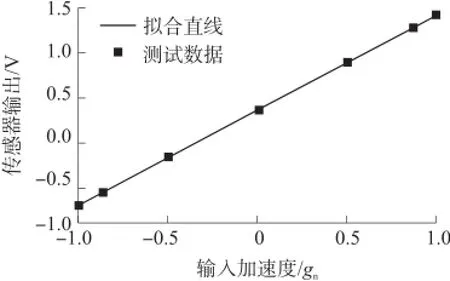

在±1 gn输入范围内,通过翻滚实验,改变输入信号幅值,得到差分输出的测试结果及采用最小二乘法拟合的直线如图10所示,计算系统非线性度为0.085%,因此该差分电路具有优良的线性度。四阶全差分ΣΔ微加速度计的性能列于表1中,结果显示,本文中所设计的加速度计具有低噪声、功耗适中,高线性度的优点,但量程较小,可应用于高精度、小量程的加速度测量中。

表1 加速度计系统测试结果

4 结论

本文设计实现了一个全差分四阶ΣΔ闭环微机械加速度计接口ASIC电路。采用全桥平衡电路解决了驱动信号的变化引起运放的输入共模电压的严重跳变,采用双侧静电力反馈方式大大提高了系统线性度。芯片采用0.5 μm CMOS工艺实现,测试结果表明,采用该芯片所构成的微加速度计灵敏度为1.32 V/gn,闭环噪声密度为75 μg/Hz1/2,系统非线性度为0.085%,功耗为40 mW。该芯片具有低噪声、高线性度、功耗适中等优点,可广泛应用在地震检测,导航、制导以及自动化工业等需要小量程、高精度的测量领域中。

[1]Liu H,Li M R.Self-Oscillation Loop Design and Measurement for an MEMS Resonant Accelerometer[J].International Journal of Adaptive Control and Signal Processing,2013,17(10):859-872.

[2]郑长勇,陈军宁.一种新型MEMS加速度计温度补偿方法研究[J].传感技术学报,2015,28(1):39-42.

[3]Aaltonen L,Halonen K.Continous-Time Interface for a Microma⁃chined Capacitive Accelerometer with NEA of 4 μg and Band⁃width of 300 Hz[J].Sensors and Actuators A,2009,154:46-56.

[4]Kimura H,Nakamura M,Inou N.Identification Method of Sensor Directions and Sensitivities in Multi-Axis Accelerometer[J]J Rob Mechatronics,2013,25(2):408-416.

[5]Lemkin M,Boser B E.A Three-Axis Micromachined Accelerome⁃ter with a CMOS Position-Sense Interface and Digital Offset-Trim Electronics[J].IEEE Journal of Solid-State Circuits,1999,34(4):456-468.

[6]Kulah H,Chae J.Noise Analysis and Characterization of a Sigma-Delta Capacitive Micraaccelerometer[J].IEEE J of Solid-State Circuits,2006,41(2):352-361.

[7]Amini B V,Ayazi F.A 2.5-V 14-bit ΣΔ CMOS SOI Capacitive Accelerometer[J].IEEE Journal of Solid-State Circuits,2004,39(12):2467-2476.

[8]Pedram L,Vladimir P P,Boris M.A ΣΔ Interface for MEMS Ac⁃celerometers Using Electrostatic Spring Constant Modulation for Cancellation of Bondwire Capacitance Drift[J].IEEE Journal of Solid-State Circuits,2013,48(1):265-275.

[9]Alireza N,David A J.A Low-Power Delta-Sigma Modulator Using a Charge-Pump Integrator[J].IEEE Transactions on Circuitsand Systems,2013,60(5):1310-1321.

[10]Rosana A D,Edmond C,Reinoud W.Pull-in-Basedμg-Resolution Accelerometer:Characterization and Noise Analysis[J].Sensors and Actuators A:Physical,2011,172(1):47-53.

[11]LIU Yuntao,YIN Liang,CHEN W P.Design of Interface Circuit of Closed-loop Accelerometer with Self-Test Function[J].Optics and Precision Engineering,2009,17(6):1379-1384.

[12]孙凤鸣,傅星,朱振宇,等.基于MEMS的微位移传感器及其应用研究[J].传感技术学报,2013,26(2):292-296.

刘云涛(1980-),男,黑龙江人,工学博士,副教授,2006年于西安交通大学获工学硕士学位,2010年于哈尔滨工业大学获工学博士学位,2011-2013年在中国科学院微电子研究所做博士后研究。现为哈尔滨工程大学副教授,主要从事传感器接口电路研究,summer924@sina.com;

赵双(1992-),女,吉林人,硕士研究生。研究方向为模拟集成电路设计;

邵雷(1974-),男,黑龙江人,工学硕士,讲师,2005年毕业于北京理工大学微电子与固体电子学专业,获工学硕士学位。至今在哈尔滨工程大学信息与通信工程学院担任讲师,研究方向为MEMS传感器,shaolei@hrbeu.edu.cn。

EEACC:723010.3969/j.issn.1004-1699.2016.06.015

高线性度全差分四阶ΣΔ微加速度计接口ASIC*

刘云涛*,赵双,邵雷

(哈尔滨工程大学信息与通信工程学院,哈尔滨150001)

为了降低电容式Sigma-Delta(ΣΔ)微机械(MEMS)加速度计的量化噪声,减小开关电荷注入和衬底噪声共模干扰,减小谐波失真,设计了一种全差分四阶ΣΔ加速度计的接口专用集成电路(ASIC)。提出了一种简单、有效的全桥平衡结构,减小了驱动信号变化时,运放输入共模的变化对电路的干扰;提出了双侧反馈结构,大大提高了系统线性度。设计完成了电荷积分器、全差分前置补偿电路、二阶积分器等电路。采用0.5 μm两层金属两层多晶n阱CMOS工艺流片,测试结果显示:闭环系统噪声密度为75 μg/Hz1/2,系统灵敏度为1.32 V/gn,非线性度0.085%,功耗40 mW。结果显示本次设计满足微加速度计接口电路的设计要求。

微加速度计;高线性度;全差分;sigma-delta

TP824

A

1004-1699(2016)06-0880-06

2015-12-21修改日期:2016-02-06

项目来源:国家自然科学基金项目(61306142);黑龙江省自然科学基金项目(QC2014068)

- 传感技术学报的其它文章

- Construction of a Cell Impedance Biosensor Based on Graphene Oxide/Polypyrrole-Indium Tin Oxide Micro-Electrode for Detecting Cell Adhesion and Proliferation*

- Acetone Gas Sensor Based on Al-Doped ZnO and Influence of Ultraviolet Excitation on Gas-Sensing Properties*

- Research of Fusion Classification of EEG Features for Multi-Class Motor Imagery*

- An Improved Method for Noninvasive Detection of Blood Glucose of Conservation of Energy Metabolism*

- Genetic Algorithms of Electromagnet in Longitudinal Wave Electromagnetic Utrasonic Dtection for Auminum Pate*

- Simulation and Experimental Investigation of Thickness Measurement Using Pulsed Eddy Current Technique*