先进射频封装技术发展面临的挑战

夏雨楠,陈宇宁,许丽清,戴 洲,李华新,程 凯

(南京电子器件研究所,南京210016)

先进射频封装技术发展面临的挑战

夏雨楠,陈宇宁,许丽清,戴洲,李华新,程凯

(南京电子器件研究所,南京210016)

随着射频技术的广泛应用和发展,射频封装已经呈现出更高密度功能集成、更高功率、更高频率和更低成本的发展要求。在这些要求下,3D封装、大功率射频器件集成、多种信号混合集成、硅中道工艺顺应而出。相对于传统射频封装,基于硅中道工艺的先进射频封装面临结构、热管理、信号完整性和工艺等多方面的挑战。

射频;中介层;3D封装;氮化镓

1 引言

在国际半导体技术路线图组织(ITRS)发布的延续摩尔(More Moore)和超越摩尔(More Than Moore)发展路线图中,射频属于超越摩尔方向的首位技术,已经是当今通信、雷达探测、电子战乃至定向能的主要信号频域。

民用方面,移动通信成为射频器件最大的应用市场,硅、锗硅、砷化镓、氮化镓等多种射频器件各得其所,目前的工作频率基本在C波段以下。市场增长刺激并加速了硅射频技术的成熟,硅和锗硅器件已经具备与砷化镓器件竞争的综合能力。在一些大规模应用上,如手机的射频前端,硅和锗硅的市场份额已经超过砷化镓;在移动基站应用市场,氮化镓射频功率器件已经具备与硅LD-MOS等综合竞争的能力,突出的表现为每瓦功率价格的趋同。

军用方面,由于应用需求相对于民用的特殊性,如更高的频率、更高的功率、更大的带宽等,砷化镓、氮化镓、磷化铟等器件优势依然突出,有些已经具备扩展到太赫兹的能力。

近年来,射频技术已经呈现出融合多种技术的平台化发展态势,趋向射频微系统。对于民用,主要的发展背景是尺寸和体积持续缩微的要求下,载频聚合和多种射频应用综合集成需求;对于军用,是多种功能综合提出的智能射频前端这一平台化发展需求。因此,作为近阶段射频微系统主要的集成技术,射频微系统封装在多个层面代表了先进射频封装。

2 先进射频封装技术的发展要求

综合军民两方面应用看,先进射频封装发展的提出主要出自于更高密度功能集成、更高功率应用、更高频率应用和更低成本的要求。这些应用要求在先进射频封装技术上演绎为如下4方面的发展。

2.1技术平台——3D封装

从先进射频封装集成发展看,功能集成是主题。其集成的主要功能模块是收发天线、双工、接收通道、发射通道等4大块,这4大块在不同的产品中由不同的元器件组成。在更多功能集成要求下,如数字处理功能块的嵌入等,集成的器件越来越多,同时器件品种也越来越复杂,传统封装集成的平面二维布局由于更长的信号互联和更大的封装面积等因素,已经显现出难以满足需求的技术弱势,突出的表现为信号延迟、损耗和完整性问题。

另一方面,先进射频器件工作频率快速跃升,如提升至毫米波和亚太赫兹,在加剧上述信号问题的同时,从工作原理上进一步提出了大幅缩小阵列中封装单元的中心距要求,如毫米波阵列,两个射频阵元中心距(1/2波长)随频率大幅度缩减至毫米量级。

综上,更多功能集成和工作频率大幅提升,从根本上提出了先进射频封装从2D向3D的发展诉求。2020年之后的5G移动基站相控阵天线阵列以及毫米波段雷达探测、电子战和通信等都已经提出了技术上一致的要求。

2.2封装集成:大功率信号发射器件

传统上,由于收发间信号串扰,着眼于性能、可靠性以及成本等方面的考虑,以功率放大器为核心的发射通道与接收通道一般是板级集成,功率放大器在更高密度、更小节距封装中的集成较少,即使有,也大都是小功率放大器,比如2.4 GHz蓝牙信号放大器。板级集成通常属于组装工艺,取平面布局,大功率放大器加入后,加上必要的热管理机构和外围电路,通常占用的PCB板面积和射频端体积较大。

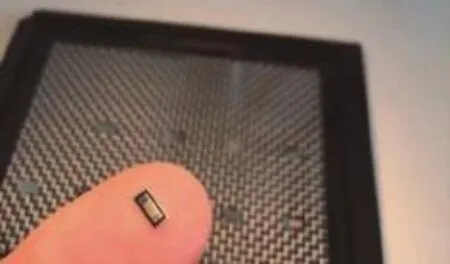

在3D封装集成的大势下,加之超高频阵列中射频封装SWaP(Size,Weight and Performance,即尺寸、重量和性能)的综合要求,包括收发天线、接收通道和发射通道的完整射频前端(RF Front End)的封装集成发展需求迫切,一体化集成趋势显著。从典型应用看,如毫米波面阵的瓷片式(共形)射频前端子阵,收、发通道的小信号和大信号器件在3D微纳封装结构中的集成是大势所趋。这意味着大信号放大器在射频3D封装的微纳结构中与小信号器件共存,彼此物理间距将达到100 nm量级或以下。现在,已经出现包含有移相器、低噪声放大器和功率放大器的完整3D集成瓦级射频前端单元,其尺寸已经达到2.5mm×2mm×0.46mm,质量是12.9 mg[1]。

2.3信号:多种信号混合集成

面向未来应用的多功能综合集成要求,如移动通信的载频聚合和MIMO(多输入、多输出),雷达探测、电子战、通信以及定向能的综合等,必然会引发和推动射频封装中多种信号的混合集成。

以应用环境和功能集成看,完整的射频前端封装集成同时也是多种信号的混合集成。以频率分,有低频信号(如电源信号)、高频信号(微波、毫米波、太赫兹)乃至光信号;以功率分,有多种器件的小功率、中功率和大功率信号;以信号属性分,有模拟信号和数字信号(模数混合信号,如A/D、D/A);以物理场分,主要有电磁场、热场和应力场。

与传统、平面和单一射频器件封装集成不同的是,不同功率、不同频率和不同属性的多种信号与多种强度不一的物理场,在射频封装3D空间中混合作用。

2.4工艺:硅中道工艺(MIDDLE END)

2013年,国际半导体技术路线图组织针对超越摩尔和延续摩尔的发展格局,对融合系统芯片(SoC)和系统封装(SiP)的更高价值系统做了技术概述,其物理架构是:

·结构:2.5D;

·集成内容:在硅中介层上集成处理器、射频器件、存储器和MEMS。

·集成基板:硅中介层(Interposer)[2]。

以其集成的器件功能看,2.5D结构中集成了传感(射频接收)、信号处理和执行(射频信号发射),这实际上是广泛意义上的射频微系统,已经在诸如移动终端和物联网(IOT)等移动射频前端上有广泛应用。

2.5D结构在当前技术基础上比较实际可行,技术手段可以支撑并实现,对比完全3D,尽管过渡性质比较明显,但是面向比传统射频封装更高的SWaP要求,是向完全3D结构演进的必经之路或曰起点。

从目前工艺技术发展对2.5D的支撑看,圆片级封装(WLP)是比较实际可行的主流技术,可以支撑封装结构从2.5D向3D的演进。与传统射频封装技术相比,WLP工艺绝大部分属前道工艺(Front End)范畴,而其任务属性却属于传统意义上的后道(Back End)封装,这也是目前国际上正在形成的中道工艺(Middle End)的区划。

对于射频封装,中道工艺是与传统射频封装工艺相比最具差异性的分水岭。从最朴素的技术要求看,如超短节距、超高互联精度等,以LTCC丝网印刷为特征工艺的传统射频封装,演进或者跃升到以圆片前道工艺为主的中道工艺(如圆片级封装)已经是趋势所在。

3 先进射频封装技术面临的挑战

3.1结构性挑战

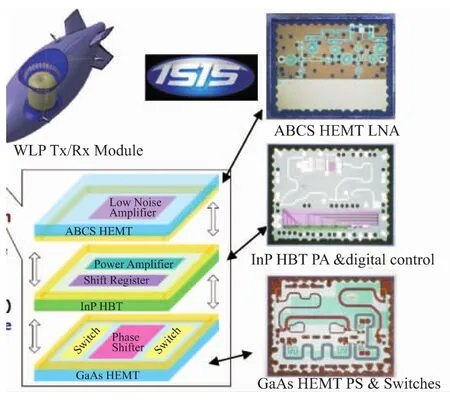

尽管现在超过20层直接堆叠大容量存储器已成为现实,但毕竟是同质堆叠,以目前技术能力看,构建射频前端多种芯片直接异构堆叠已经出现(见图1,为演示验证目的),但大规模生产技术尚未成熟,因此,从2.5D逐步演进至完全3D较为实际可行。从技术现状和发展看,这两种结构都存在普遍的技术挑战——结构稳定性。

相对于同质堆叠,影响异构2.5D和3D结构稳定性的因素较复杂,以来源归类,基本可概括为材料、器件和工艺,统一表现为对结构的应力作用。

在材料层面,砷化镓、氮化镓、磷化铟等材料与硅(主要是硅中介层,即Interposer)相互之间存在不同程度的热膨胀系数(CTE)失配,这是目前限制这些器件直接堆叠的一大原因。而且,由此导致的热应力威胁了结构稳定,在超薄芯片集成和大功率器件工作时,后果更为恶劣,可能导致结构解体。因此,在难以直接堆叠的前提下,基于硅中介层的多种芯片封装集成将会长期存在和发展[3]。尽管如此,由不同材料CTE失配导致的结构不稳定性因素依然存在,只不过是首先作用于中介层,然后通过中介层作用于整个结构。值得注意的是,CTE失配产生的作用是双向的,一方面影响到结构,另一方面也反作用于器件,如在较为典型的射频圆片级封装中,失配造成硅中介层中所埋置的磷化铟芯片的过应力损毁。

美国诺格公司基于完全3D圆片级封装集成技术的射频T/R模块见图1,分别由锑基化合物HEMT低噪声放大器+磷化铟HBT功率放大器与数字控制电路+砷化镓HEMT移相器和开关等3个功能层堆叠。从图示可以看出,层与层之间加入了应力匹配环(黄色部分,兼键合接合材料)[1]。

图1 基于完全3D圆片级封装技术的射频T/R模块(美国诺格公司)

在器件层面,功率器件是结构性影响的主要因素,其工作时的高热引发热应力冲击造成结构缺陷、失效和损毁。在热管理技术尚未实现重大突破的技术条件下,这一问题对于先进射频封装的影响力是最大的。从实际应用看,射频功率器件的功率附加效率(PAE)其实并不高,即使是氮化镓功率管,在实际工作时PAE一般是40%以下,这也就意味着有超过50%的直流功耗将变成热功耗。因此,若没有非常高效的热管理机制,先进射频封装微纳结构中的功率器件对结构的影响将是致命的。

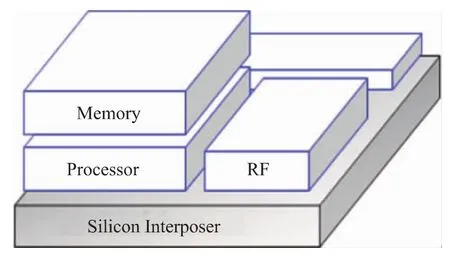

图2 基于硅中介层的2.5D射频封装

图2为基于硅中介层的2.5D射频封装[4]。从产业角度看,基于射频功能器件材料属性、频率特性和热特性等原因,2.5D构架是现阶段技术可支撑并实现的,且具备商业应用可接受的成本预算。

在工艺层面,以WLP技术为代表看,工艺对结构产生的影响主要作用于两个层面,一是硅中介层,二是整体结构。中介层是组成整体结构的功能单元层,因此,中介层结构的稳定程度会影响到整个封装结构。中介层工艺中的多种工艺,如集成无源器件(IPD)的内埋、多种功能器件埋置和嵌入、传输线的电镀加厚、介质和钝化层生长以及光波导介质生长等,本质上都是异构的,在中介层中引发了多种结构性物理参数的失配。如果没有有效的匹配和缓冲机制,这些失配除直接导致中介层工艺半途终结外,也同时会在中介层中产生并留存结构性隐患,在过应力时破坏中介层和整体结构。中介层对于整体结构的作用主要通过层-层键合界面和TSV互联施加,在3D结构成型过程中首先表现,并在工作时加剧。由于不同功能中介层的工艺不同,如高温工艺的有无,因此,也存在层-层之间多种结构性物理参数的失配问题。另外,与存储器堆叠不同的是,TSV在3D结构中还需传输和传导大信号和热,工艺要求与常规区别较大,如填孔材料、孔径、密度等,这些也将直接影响到整体结构的稳定,如在强热障存在时,破坏性作用突出,甚至会引发中介层开裂和整体封装结构裂解。在超薄圆片工艺发展要求下,中介层和功能芯片超薄化都将激化和恶化上述失配,在多强场环境下,对整体结构的影响更甚。

3.2热管理挑战

从完整的射频前端发展要求看,接收通道和发射通道的一体化封装集成是必然,相对于传统板级集成,发射通道上功率器件的集成是其完整性表征,是对封装严酷的技术挑战。

对于小功率射频前端的封装,比如移动终端射频前端,其发射通道的功率通常在2~3 W左右,在封装热管理能力方面,QFN这类塑料封装能力足够,LGA则更强。但是,中大功率器件的封装集成,特别是大功率器件,高热引发的热管理问题对小型化和微型化的封装更为严酷,已经成为世界性的技术难题。一方面,功率芯片中的热若不能快速导出,沟道及附近将形成热点(Hot Spot)导致芯片烧毁;另一方面,封装结构中热的累积,将迅速激发热应力生成,进而毁坏整体封装结构。

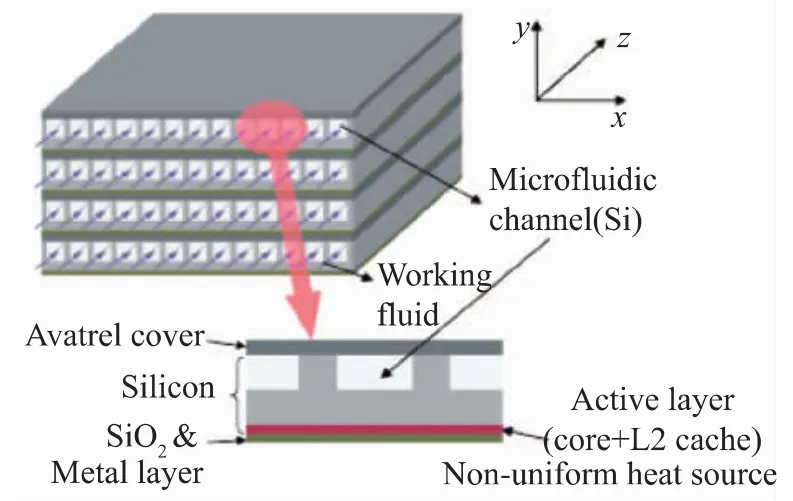

目前,比较一致的热管理链路是芯片级—封装级—(子)阵列级,分别对应导热—散热—热转化等热管理任务节点,已知的代表性目标是在射频封装这一级达到1 kW/cm2的散热能力[5]。尽管芯片级热管理技术已经在局部领域取得突破,比如金刚石衬底与氮化镓功率器件的结合已经提升输出功率超过3倍[6],但这仅仅预示着芯片级导热能力有所提升,实际上进一步强化了对封装散热能力的要求。从目前的发展看,基于微电子机械系统(MEMS)技术的微流体(Microfluidic)获得较为普遍的认同(见图3),测试证明已经具备高达1 kW/cm2热流密度[7]的散热能力。但是,以目前的技术能力看,相对于高功率芯片热点30kW/cm2热流密度[8]的更高散热要求,尤其是在高可靠微纳尺度MEMS微流体技术尚处于研究阶段下,中大功率射频功率器件的集成所带来的封装热管理挑战将在较长时期内存在,并在一定程度上能产生类似“一票否决”的副作用。

图3 基于硅工艺的典型微流体

图3为基于硅工艺的典型微流体示意图:聚合物盖板(Avatrell 2000 P)+硅流体沟道+底板(二氧化硅+金属层)[9]。在此结构中,热源层已经包含其中,并作一体化集成,体现出散热结构与热源的直接作用机制。

图4洛克希德马丁公司研制成功的微流体实物图

图4为美国洛克希德马丁公司于2016年3月公开报道其研制成功的微流体[10]。尺寸为长5 mm,宽2.5 mm,厚250 μm,已经可以满足大功率器件在器件级和封装级集成的尺度要求和散热能力要求。

3.3信号完整性挑战

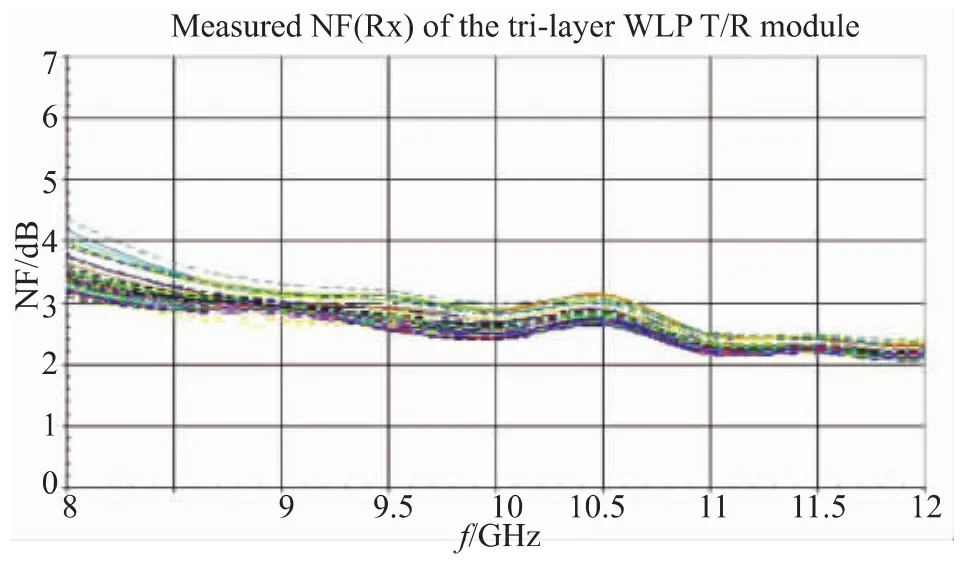

在先进射频封装的3D结构中,电信号类别多且复杂,信号的平面互联主要由中介层上的RDL层(Re-Distribution Layer,再分布层)实现,信号的垂直互联主要由TSV担当,多种电信号在3D微纳结构中形成较为复杂的电磁环境,由于三维结构中多个层面物理尺寸的缩微、大功率射频信号的存在和数字信号处理芯片信号的低电平化,信号串扰(Crosstalk)引发的信号完整性问题较常规板级集成更为突出。

一方面,典型数字信号处理系统芯片(SoC)的工作电压已经降至0.5 V量级,而氮化镓功率芯片的工作电压通常在28 V、48 V甚至65 V,在射频封装3D微纳结构中,若没有良好的隔离机制,高达65 V的偏置电压和工作电路足以形成对0.5 V工作的数字芯片和信号电平的强电场干扰,产生误工作和噪声干扰(见图5)以及信号乱码。

图5 美国诺格公司3层结构圆片级封装T/R模块噪声[11]

另一方面,如果没有良好的隔离和屏蔽机制,大功率射频放大器工作时所产生的微波辐射,尤其是在微纳尺度结构中,也是导致信号串扰的主要来源,对于低电平的数字信号或者存储器,所产生的强微波辐射作用将导致信号的误操作,在数字电路芯片进一步低电压、低信号电平工作、大功率器件必须高电压工作的冲突下,这一挑战将变得更加严峻并将长期存在。

3.4工艺挑战

以圆片级封装为典型,先进3D射频封装工艺平台主要由中介层、TSV和键合三大工艺模块组成。相对于常规射频封装工艺,比如LTCC,先进3D射频封装工艺平台代表了射频封装工艺平台的大幅度跃升,最为突出的特征是封装的前道工艺化,也即上述的中道工艺。对于以LTCC为代表的传统平台,这种跃升是颠覆性的,形成了对传统平台的最大挑战:丝网印刷—步进光刻;50 μm特征尺寸—0.5 μm特征尺寸;共烧—键合;贴片/烧结—埋植/键合;平行缝焊—硅帽键合。从射频要求出发,上述三大工艺模块也存在挑战。

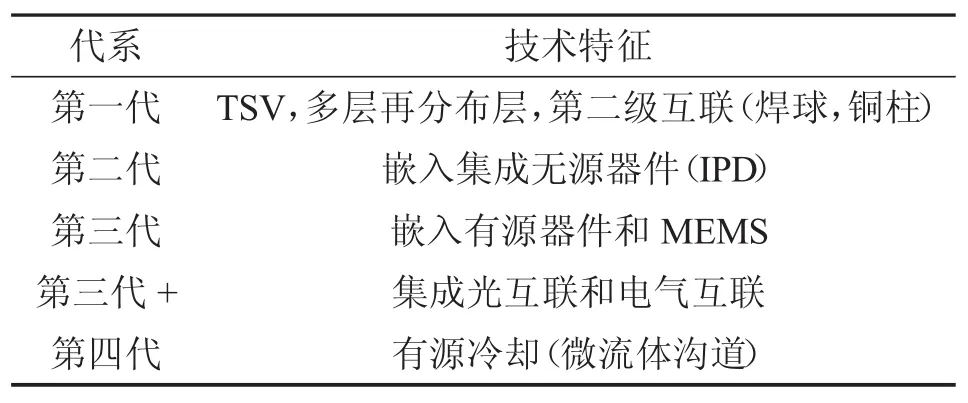

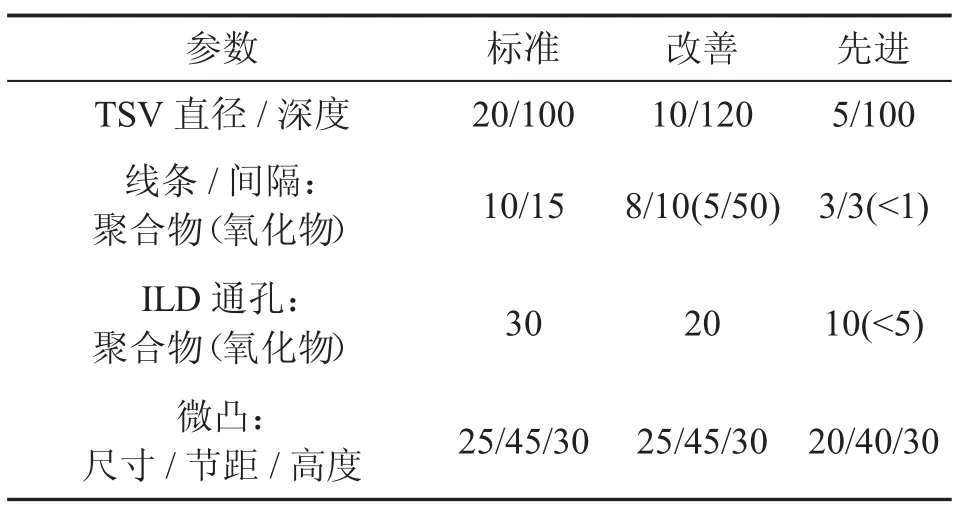

中介层工艺:中介层材质目前主要有硅和玻璃,玻璃在局部射频性能方面较硅稍好,但在工艺可移植性、技术成熟度和制造成熟度方面则是硅胜出。目前,以集成的内容划分,中介层技术已经初步形成四代(见表1),以特征尺寸分,基本上可以分为3个特征工艺:标准、改善、先进(见表2)。中介层大部分工艺与现有的硅前道工艺一致,但由于多种器件集成要求,如砷化镓、氮化镓、磷化铟、IPD等,因此异构工艺的挑战突出。一方面,多种芯片在中介层中埋置/置放精度提高是一大困难,且同时影响到与RDL的互联对准精度,对于微波传输线性能影响突出;另一方面,上述化合物半导体芯片的互联通常是金体系的,以电镀加厚,如传输线等,这与硅中介层互联铜体系、硅锗芯片铝系等存在工艺兼容和匹配问题,甚至还存在金属系不同引发的可靠性问题。

表1 中介层代系划分[12]

表2 基于TSV中介层技术特征(单位/μm)[13]

TSV工艺:TSV工艺是3D射频封装的特征工艺,尽管在诸如大容量存储器堆叠工艺中应用广泛且成熟,但是,一般的TSV在大功率信号和热等强物理场作用下,电过应力和机械过应力问题突出,加之恶劣和极端环境工作要求,气密性等可靠性挑战突出,因此,对射频封装的TSV工艺,应用适应性增强且优化技术难度较高。

键合工艺:键合工艺目前已经有多种形式,圆片-圆片键合是目前可见到的大规模键合形式。对于基于圆片级封装平台的3D射频封装,圆片键合是在圆片级形成真正3D结构的成型工艺。限于工艺能力,键合工艺目前对准精度在微米量级,相对于步进光刻工艺所达到的纳米精度,无论是芯片与圆片还是圆片与圆片键合,键合工艺在2D方向上的对准精度提升有些滞后,影响了3D结构精度;此外,硅帽键合在强热场和极端恶劣工作环境“内外夹击”下的气密性还是一项综合性的挑战,对键合界面提出更高要求,况且,如果要求在硅帽上表面制备天线和穿过硅帽的TSV,工艺及可靠性挑战则更为严酷。

4 结束语

传统LTCC技术的管壳到以硅基中道工艺为平台的先进射频封装的跃升,是先进射频封装多功能集成和更高密度信号集成的需要。在这一过程中,挑战是多方面的。从应用和先进射频技术发展要求来看,在较长一段时期,基于圆片级封装的2.5D和完全3D封装集成是先进射频技术发展的平台支柱,而分析和应对挑战是平台发展的必经过程。

[1]Patty Chang-Chien.Northrop Grumman Aerospace Systems,Wafer-scaleAssembly&HeterogeneousIntegration Technologies for MMICs[C].IMS 2012 3D Integrated Circuit Workshop,16.

[2]Paolo Gargini.Challenges and Options for the Semiconductor Industry in the 21st[C].Semicon,Japan,2013.54.

[3]Paolo Gargini.Challenges and Options for the Semiconductor Industry in the 21st[C].Semicon,Japan,2013.62.

[4]Ho-Ming Tong.3D ICs:The Next Revolution[R].GM& Chief R&D Office Group R&D December,ASE GROUP,2009.22.

[5]Defense Advanced Research Projects Agency[R].Department of Defense Fiscal Year(FY)2017 President's Budget,Defense-WideJustificationBookVolume1of1,Submission February 2016.188-189.

[6]Submission February 2016,Defense Advanced Research Projects Agency[R].Department of Defense Fiscal Year (FY)2017 President's Budget,Defense-Wide Justification Book Volume 1 of 1.189.

[7]m.lockheedmartin.com/us/innovations/030716-webt-ice-cooldarpa.html[EB/OL].

[8]Defense Advanced Research Projects Agency[R].Department of Defense Fiscal Year(FY)2017 President's Budget,Defense-WideJustificationBookVolume1of1,Submission February 2016.189.

[9]Yoon Jo Kim,Yogendra K Joshi,Andrei G Fedorov,Young-Joon Lee,Sung-Kyu Lim.Thermal Characterization of Interlayer Microfluidic Cooling of Three-Dimensional Integrated Circuits With Nonuniform Heat Flux[J].Journal of Heat Transfer,2010,132(4):2.

[10]M lockheedmartin.com/us/innovations/030716-webt-icecool-darpa.html[EB/OL].

[11]PattyChang-Chien.NorthropGrummanAerospaceSystems,Wafer-scaleAssembly&HeterogeneousIntegration TechnologiesforMMICs[C].IMS 2012 3D Integrated Circuit Workshop.17.

[12]M Juergen Wolf Fraunhofer IZM.European 3D TSV Summit[C].Grenoble,January 22-23,2013 3D Integration Technologies Enabling System in Package Solutions.13.

[13]M Juergen Wolf Fraunhofer IZM.European 3D TSV Summit[C].Grenoble,January 22-23,2013 3D Integration Technologies Enabling System in Package Solutions.12.

The Challenges Confronting the Development of Advanced RF Packaging Technology

XIA Yunan,CHEN Yuning,XU Liqing,DAI Zhou,LI Huaxin,CHENG Kai

(Nanjing Electronic Devices Institute,Nanjing 210016,China)

With rapid development and wide application of RF technology,requirements of higher functional integration,higher RF power and frequency,lower cost are now pushing the RF packaging technology to involve 3D packaging,high power RF devices integration,multi-signal hybrid integration and middle-end process platform.Thus emerging out are challenges such as package structure,thermal management,signal integrity and process.

RF;interposer;3D package;GaN

TN305.94

A

1681-1070(2016)05-0001-06

2016-3-22

夏雨楠(1966—),女,重庆人,工程师,主要研究方向为射频器件封装,现在南京电子器件研究所从事射频器件封装工艺研发工作。