寄生电阻对DC-DC变换器性能影响的研究

苑 红,丁新平,王伯荣,牟 伟,杨 超

(青岛理工大学自动化工程学院,青岛266520)

DOI:10.13234/j.issn.2095-2805.2016.1.80中图分类号:TM302.1文献标志码:A

寄生电阻对DC-DC变换器性能影响的研究

苑红,丁新平,王伯荣,牟伟,杨超

(青岛理工大学自动化工程学院,青岛266520)

研究了DC-DC变换器电压增益、工作效率和元器件、电路板(PCB)寄生电阻之间的数量关系。以Zeta变换器为例运用状态空间平均法研究了电路增益、效率的影响因素,推导出增益和效率与电路参数(包括寄生电阻)的关系式;分析DC-DC电路电压增益跌落和效率下降的根源,分别研究各元器件寄生电阻、PCB环路寄生电阻对电压增益及效率造成的影响,推导出各寄生电阻对电压增益、效率影响的比重,为电路设计及有选择地进行优化提供了理论依据;最后,实验室搭建2台50 W的电路样机进行仿真及实验。实验结果验证理论分析的正确性。

DC-DC变换器;电压增益;工作效率;寄生电阻

Project Supported by Natural Science Foundation of China(51477079);China Postdoctoral Science Foundation (2013M531598)

引言

DC-DC变换器作为一种基本变换器因其结构简单、效率高而被广泛应用于工业仪器仪表、办公自动化、医疗设备、军事、航天等领域,但实际工程中由于设计不当,容易出现电压增益跌落、效率下降等现象,这不仅影响了DC-DC变换器的工作质量,而且限制了其应用范围。变换器设计过程中存在的缺陷,如元器件、PCB环路存在寄生电阻,均是造成上述不良现象的直接因素。寄生电阻对DC-DC变换器增益、效率影响方面的研究相对较少,大部分均以工程经验为依据,相关理论分析依然成为亟待解决的问题。

本文以状态空间平均法推导了Zeta变换器电压增益、效率数学表达式。分析元器件、PCB环路寄生电阻对变换器性能影响,探究电压增益跌落和工作效率下降的根源所在,为电路的优化设计及参数选型给出定量化理论依据及指导性建议。通过仿真和样机实验验证理论分析的正确性。

1 Zeta电路工作原理

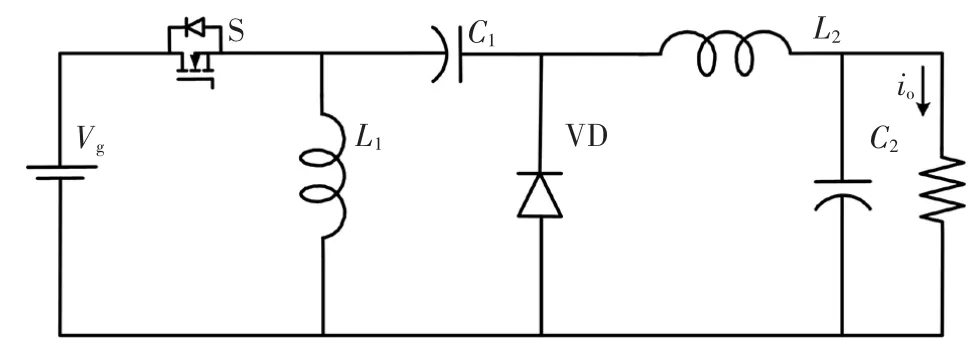

本文以Zeta变换器为例探究变换器电压增益、效率的影响因素,定量分析各部分寄生电阻对电路性能造成的影响。图1所示为Zeta变换器原理。

图1 Zeta DC-DC变换器Fig.1 Converter of chopper Zeta

Zeta变换器存在CCM和DCM2种工作模式,本文主要研究基于CCM模式的Zeta变换器电路电压增益、效率与各元器件、PCB环路的寄生电阻的关系。图2为CCM模式下2种工作状态等效电路。

图2 变换器等效电路Fig.2 Equivalent circuit of converter

状态1:如图2(a),开关管S导通时,电源Vg向L1充电,经C1、L2向负载供电,L1、L2储能,二极管VD反向截止。

状态2:如图2(b),开关管S关断时,L1经VD 向C1充电,L2经VD续流[1]。

稳态时由电感伏秒平衡定理可推出理想情况下变换器的电压增益B为

式中:D为开关管S的占空比,通过调节D,可实现输出电压的任意可调;Vg为输入电压;Vo为输出电压。

2 寄生电阻对电压增益、效率的影响

考虑电感、电容和环路寄生电阻情况下,分析寄生电阻对Zeta变换器电压增益、效率的影响,由状态空间平均法建立其数学模型推导电压增益、效率的表达式。

2.1元件寄生电阻对变换器影响

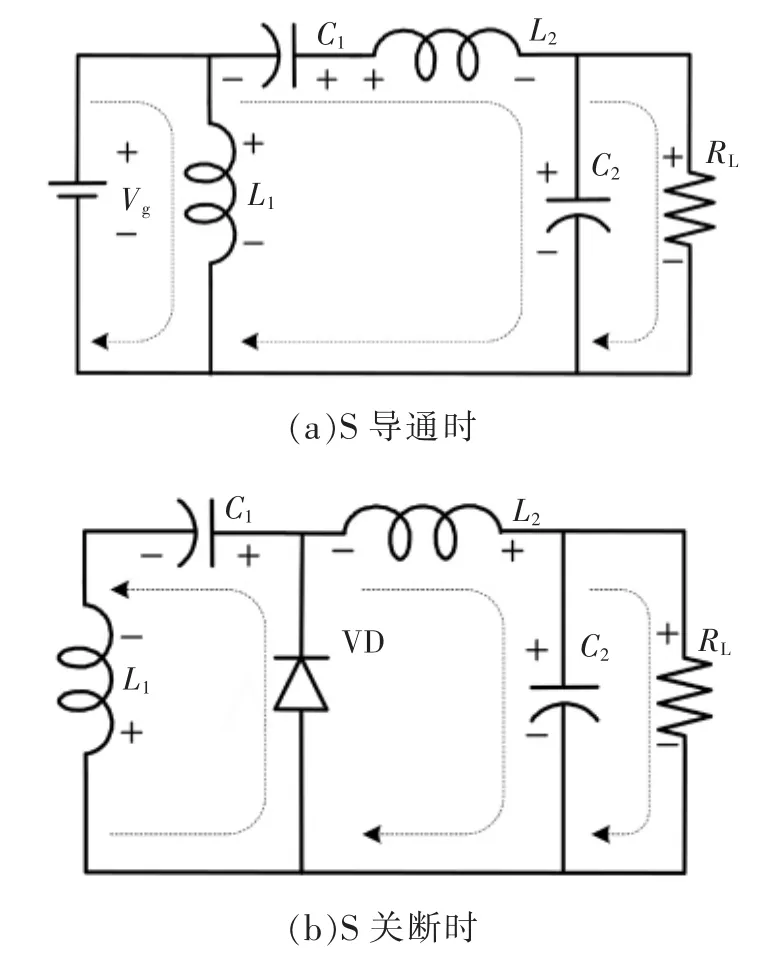

模型中考虑电感、电容的寄生电阻r1、r2、R1、R2。选取电感电流iL1、iL2和电容电压vC1、vC2为状态变量,输入电压Vg、二极管管压降Vd、负载电流io、开关管占空比D为模型的输入信号,负载电阻为RL。图3为Zeta变换器不同状态的等效电路。

图3 Zeta变换器等效电路Fig.3 Equivalent circuit of Zeta converter

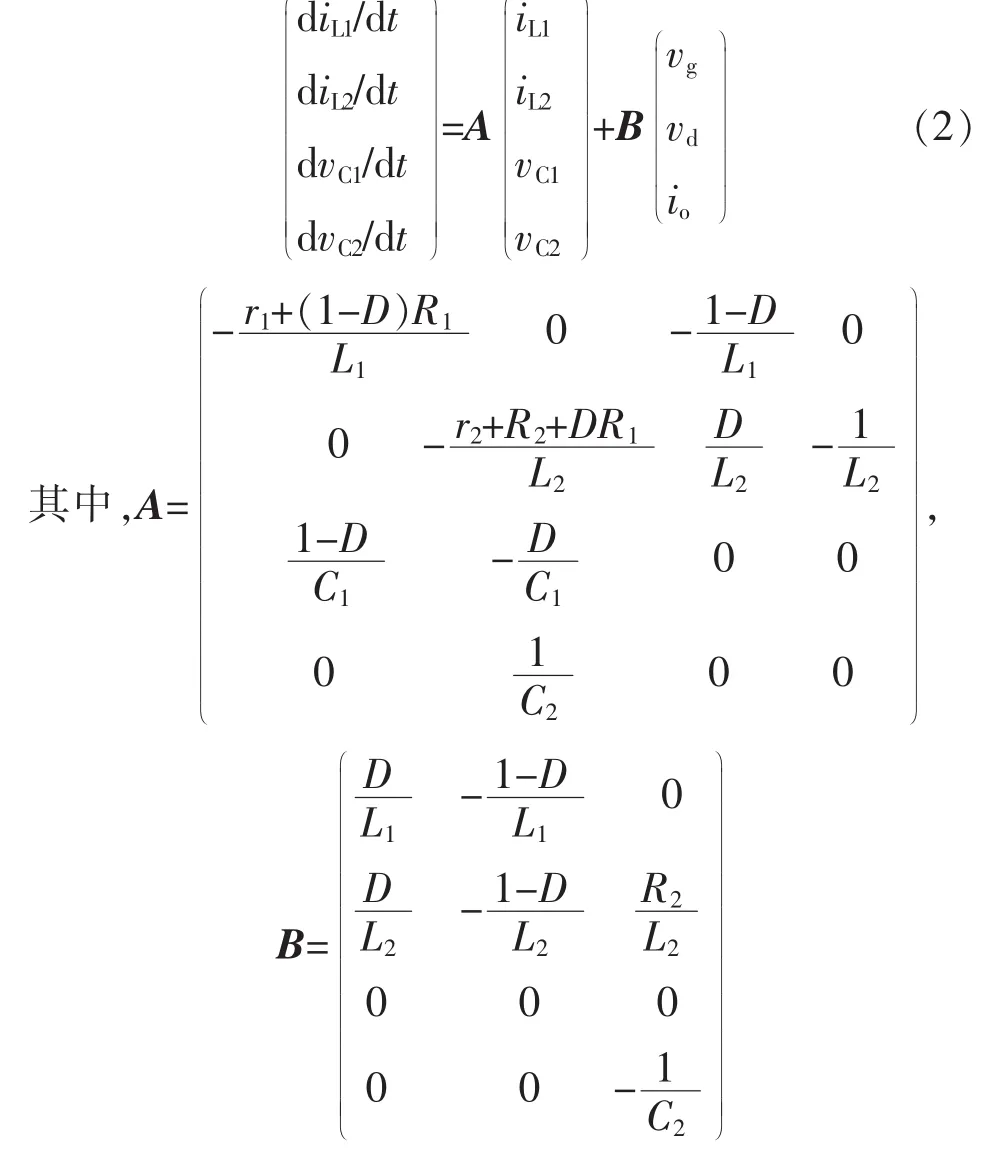

综合2种状态的环路方程,由状态空间平均法可得Zeta等效电路状态方程为

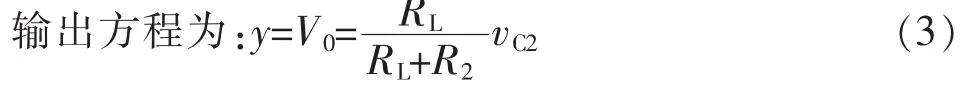

系统稳态时,可由系统静态工作点AX+BU=0求得系统稳态工作时的变换器的电压增益B,即

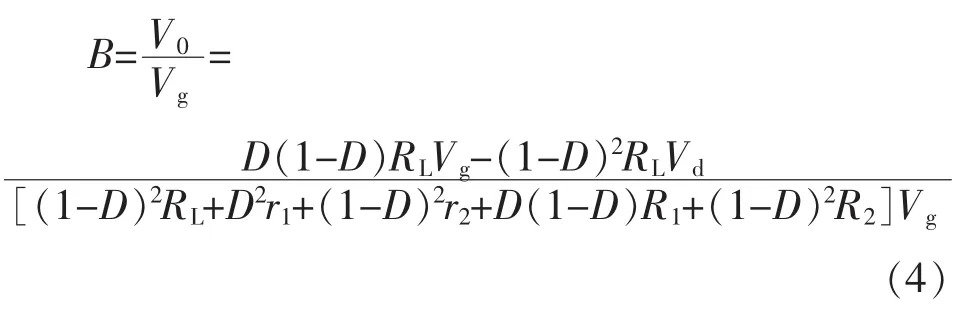

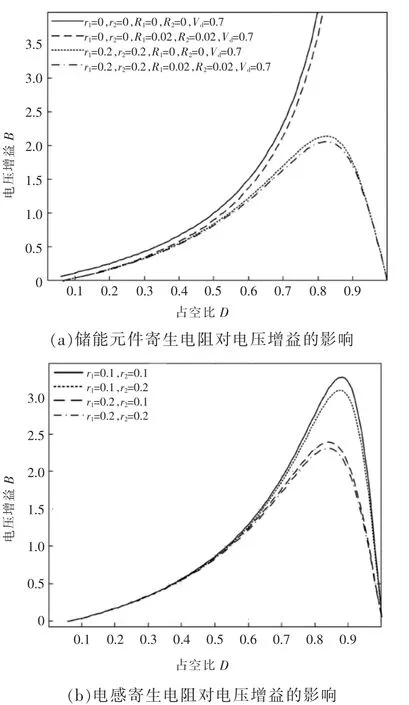

由式(4)可知,变换器升压增益与Vd、r1、r2、R1、R2有关,取Vg=9 V,Vd=0.7 V,RL=10 Ω,得储能元件寄生电阻对电压增益的影响曲线如图4所示。图4中寄生电阻取值由双臂电桥测量所得。

由图4(a)曲线可知,与理想状态相比,考虑元器件寄生电阻时,变换器的电压增益出现下降。当r1、r2取0时,电压增益改善,接近理想状态;当R1、R2=0时,电压增益提升小。和电容寄生电阻相比较,电感寄生电阻对电路电压增益和效率影响较大,这与电容寄生电阻值数量级小相吻合,电感元件的寄生电阻较之电容元件的寄生电阻对电路影响更明显。图4(b)为仅考虑电感寄生电阻时电压增益曲线,综合式(4)知,当D>0.5时,即变换器在

图4 储能元件寄生电阻对电压增益的影响Fig.4 Influence of parasitic resistance to voltage gain

升压模式下,电感L1的寄生电阻对电压增益影响大;反之,当D<0.5时,变换器工作在降压模式时,电感L2的寄生电阻对其影响大。

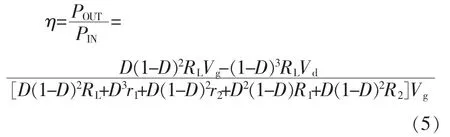

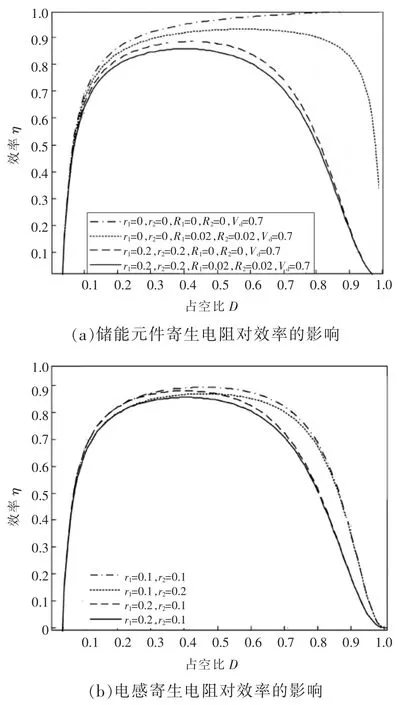

稳态工作时,变换器工作效率η为

式中:Pout为变换器输出功率;Pin为变换器输入功率。储能元件寄生电阻对变换器工作效率的影响如图5所示。

图5(a)为考虑不同元器件寄生电阻时变换器效率对比曲线,由此可见,电感寄生电阻相比电容寄生电阻对效率影响更大。图5(b)为仅考虑电感寄生电阻时效率曲线,分析可知在D>0.5时,减小r1,对效率提升明显;反之D<0.5,减小r2,对变换器效率提升明显。变换器效率曲线和电压增益曲线完全吻合,对电路的优化设计具有一定的理论指导意义。

图5 储能元件寄生电阻对变换器工作效率的影响Fig.5 influence of parasitic resistance to work efficiency

变换器中,应尽量减少电感、电容寄生电阻,以改善电压增益跌落、减少功率损耗。相比于电容寄生电阻,电感寄生电阻对电路性能影响大,设计电路时,电感的选择直接影响到电路性能的优劣。在不影响电路正常工作的情况下,选择高磁导率磁性材料,减少绕线匝数、双线并饶等优化措施减小电感的寄生电阻。在Zeta变换器中,首先确定其额定工作环境(升压或降压),然后有针对性地优化电感L1或L2以最大限度地发挥变换器性能。其他变换器分析过程与此类同。

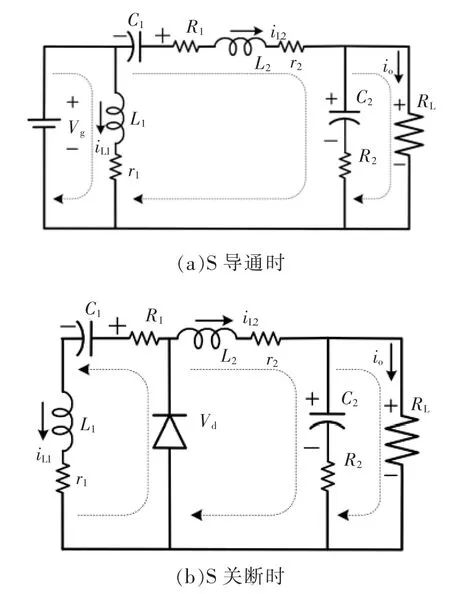

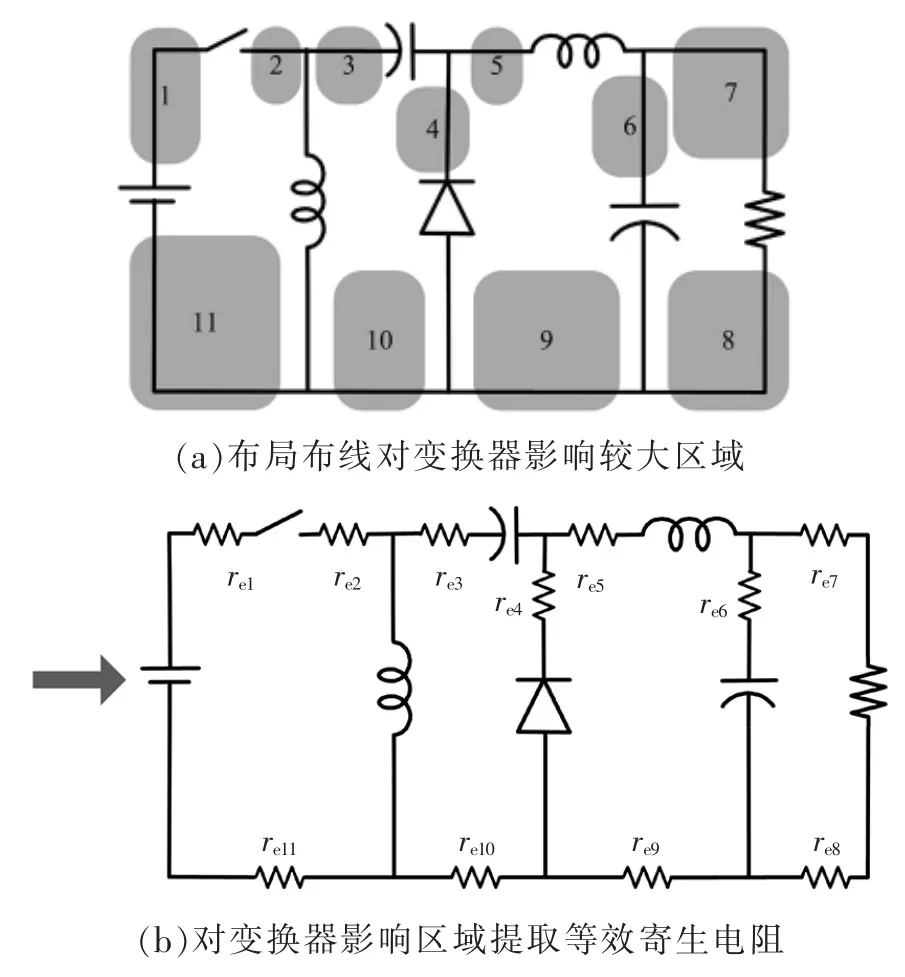

2.2环路电阻对变换器性能影响

绘制PCB电路板时,变换器的环路大小、布线状况将影响变换器的电压增益与效率。环路寄生电阻等效电路如图6所示。提取对变换器较大影响的布线区域寄生电阻re,分析其对变换器电压增益、效率的影响。为了分析问题的方便,先不考虑元器件寄生电阻,只考虑布局布线的寄生电阻。

图6 环路寄生电阻等效电路Fig.6 Equivalent circuit of the loop parasitic resistance

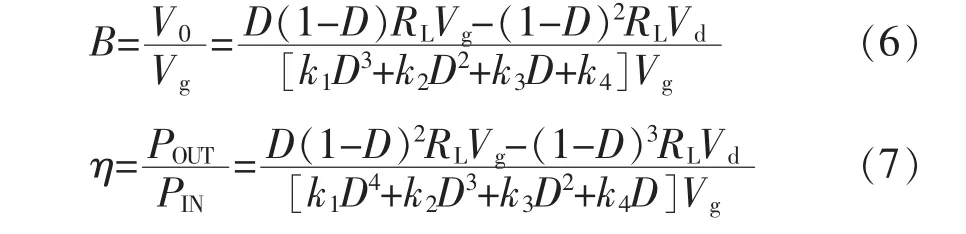

图6(a)所示为考虑线路寄生电阻的电路图,图6(b)为其集总参数模型。同第2.1节运用状态空间平均法建立变换器数学模型,推导出电压增益、工作效率表达式为

其中:

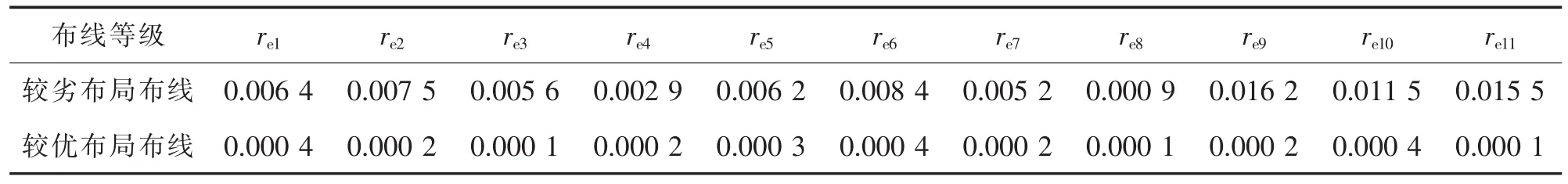

由式(6)、式(7)可知,PCB环路的寄生电阻亦能够对电压增益、效率产生影响。为了更直观地研究环路寄生电阻对变换器的影响,分别绘制了2块PCB板,通过提取2电路板寄生电阻参数,得到Zeta变换器环路寄生参数如表1所示。

表1 PCB布线寄生电阻值Tab.1 The parameters value of PCB wiring

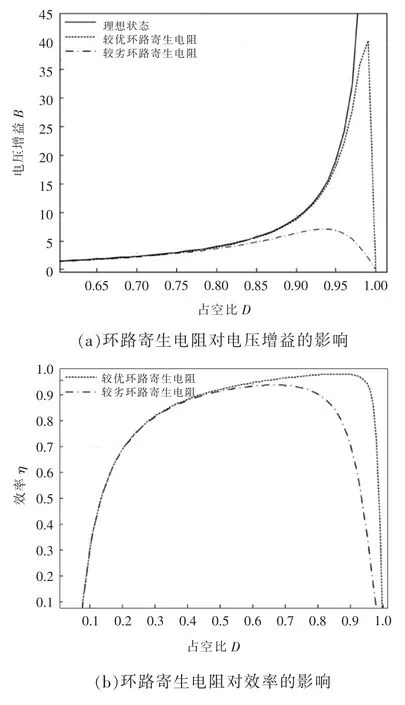

图7 环路寄生电阻对电压增益、效率的影响Fig.7 Influence of parasitic resistance to voltage gain and work efficiency

根据表1并结合式(4)绘制变换器电压增益曲线及效率曲线,如图7所示。

图7(a)可见,环路寄生电阻re在开关管占空比D较小时对电压增益影响较小。当D>0.8时,较劣环路的电路板电压增益出现跌落,而较优环路的电路板则基本没有影响;当D>0.9时,较劣环路寄生电阻可导致电压增益明显跌落。由图(b)可见,占空比D<0.5时,环路寄生电阻re对变换器工作效率影响不明显;当D>0.5时,环路寄生电阻愈发影响变换器效率;而当D>0.8时,PCB环路布局的优劣可造成变换器效率相差5%之多。

PCB布局时应尽可能地减小变换器中大电流、高频电流环路,使PCB中的功率线路粗且短,以减小环路寄生电阻,改善电压增益、提高工作效率。PCB布局布线时,环路寄生电感等对电路EMI影响的研究不在本文研究范围之内,本文重点研究寄生电阻对变换器电压增益以及效率的影响。

3 仿真和实验

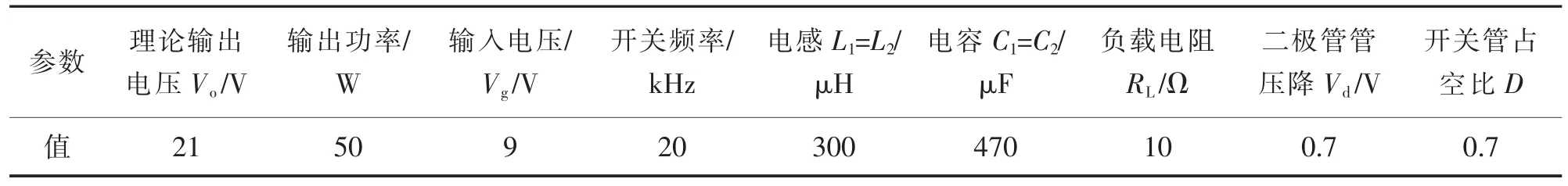

为验证上述公式推导及理论分析的正确性,通过仿真软件和样机实验对其进行验证。仿真和实验电路参数如表2。

表2 仿真和实验参数Tab.2 Parameters of simulation and experiment

3.1仿真结果

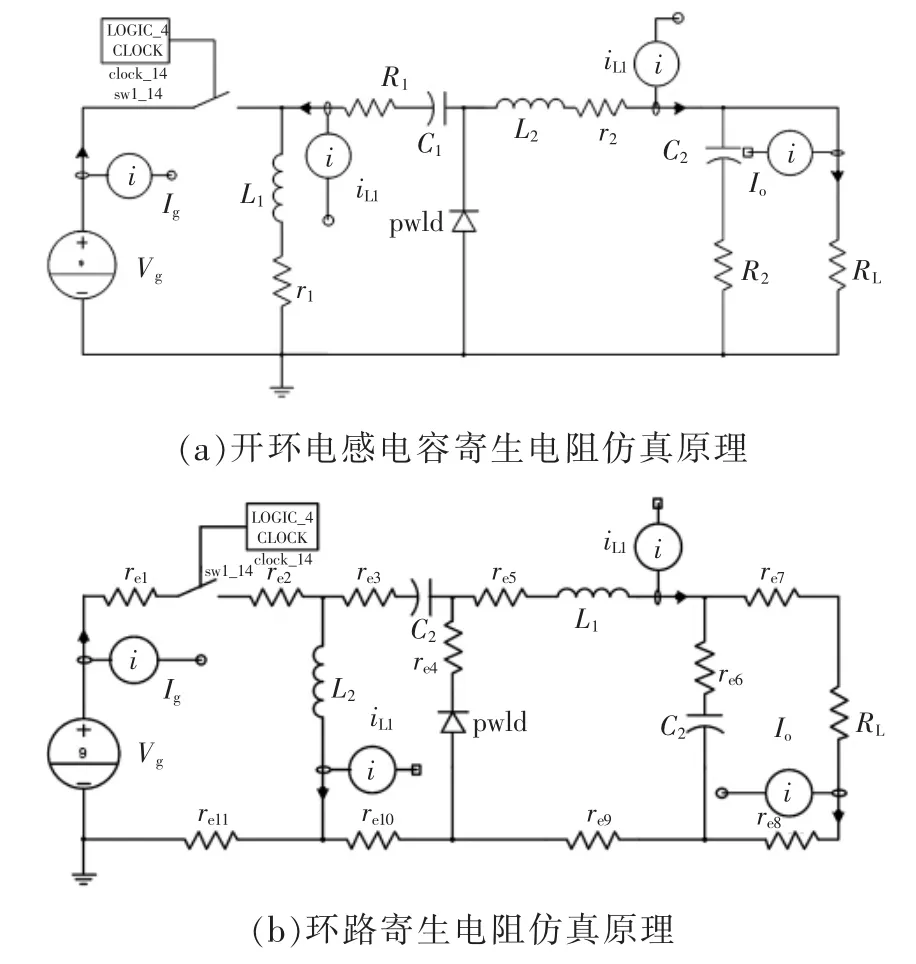

如图8所示为仿真原理示意,图9、图10为D= 0.7时开环仿真波形(D=0.7理想状态时电压增益应为B=2.333)。

图8 仿真原理示意Fig.8 Schematic diagram of simulation Principle

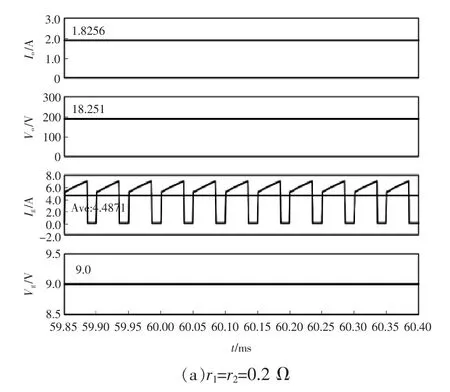

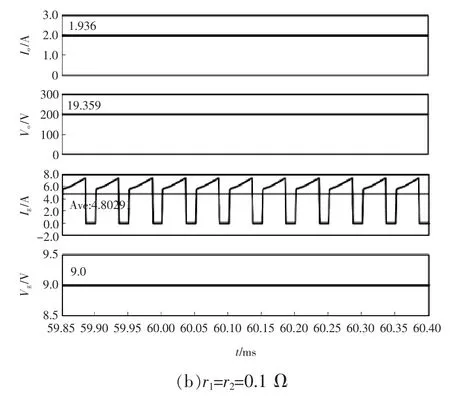

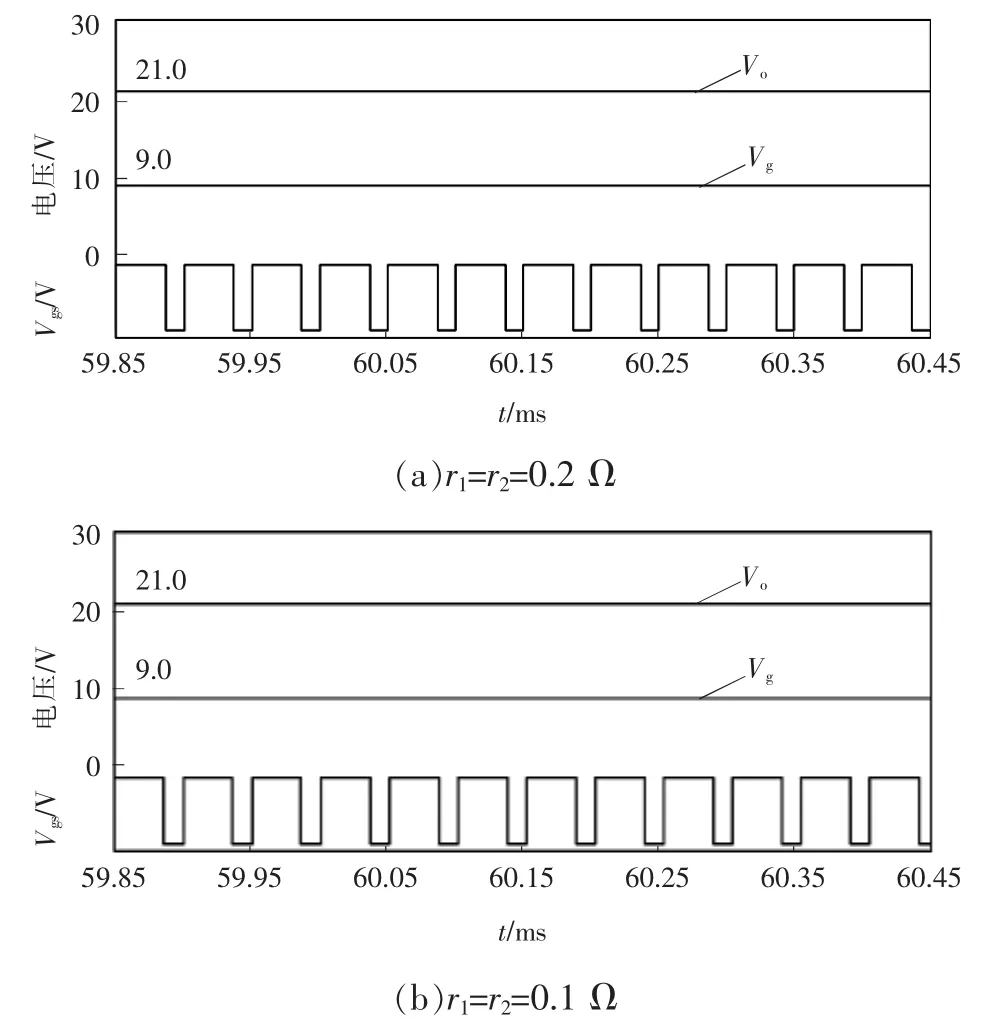

仿真时,电容寄生电阻R1、R2对电路影响较小,这里主要仿真分析电感寄生电阻r1、r2对电路的影响,图9分别是r1=r2=0.2 Ω和r1=r2=0.1 Ω的仿真波形。

图9 改变电感寄生电阻仿真结果Fig.9 Simulation results of changing inductance parasitic resistance

由图9(a)的仿真结果可知,电压增益B=2.028;效率η=82.5%,图9(b)中降低电感L1、L2寄生电阻,电压增益B=2.151;效率η=86.7%。由此可见,降低电感寄生电阻能够改善电压增益、提高工作效率,与理论分析基本相符。

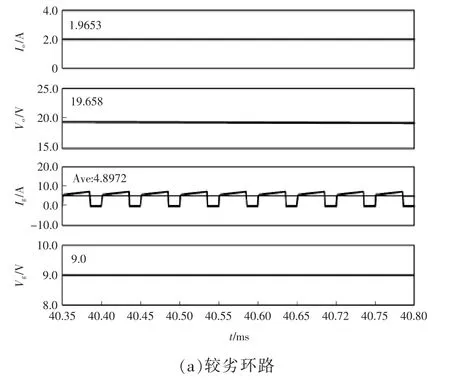

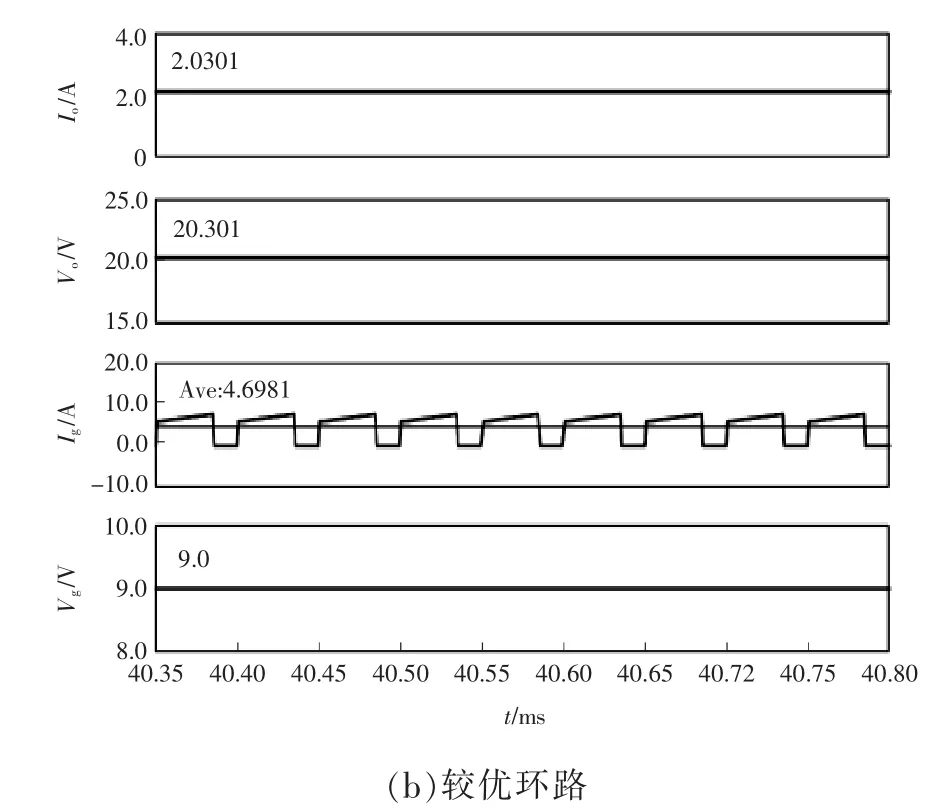

图10为忽略电感、电容寄生电阻对电路的影响,只研究PCB环路寄生电阻对电压增益、效率影响的仿真波形图,由图10(a)较劣环路仿真波形得,电压增益B=2.184;效率η=87.7%。图10(b)为较优环路仿真波形得,电压增益B=2.256;效率η=94.4%。通过对比可知,降低环路寄生电阻可改善变换器电压增益、提高工作效率,与理论分析基本相吻合。

图10 改变环路寄生电阻仿真结果Fig.10 Simulation results of changing loop parasitic resistance

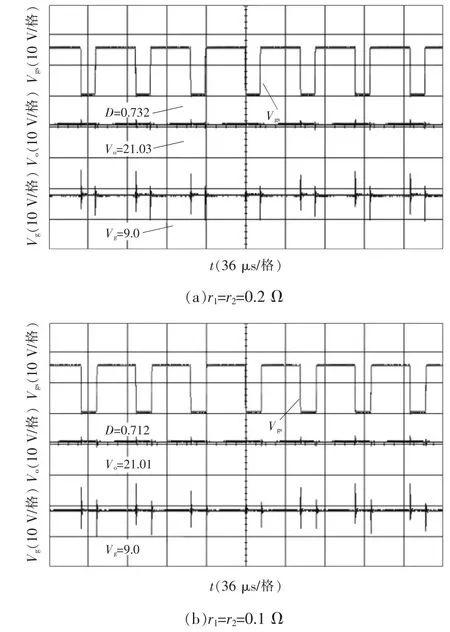

图11为r1=r2=0.2 Ω和r1=r2=0.1 Ω的仿真波形。当输入电压Vg为9 V时,同样稳压输出21 V。电感寄生电阻为0.2 Ω时,占空比D需要达到0.736 3才能满足输出,电感寄生电阻为0.1 Ω时,D= 0.718 6就可以达到稳压输出21 V。

图11 输入、输出电压与占空比的闭环仿真波形Fig.11 Closed loop simulation curves of input voltage,output voltage with duty

3.2实验结果

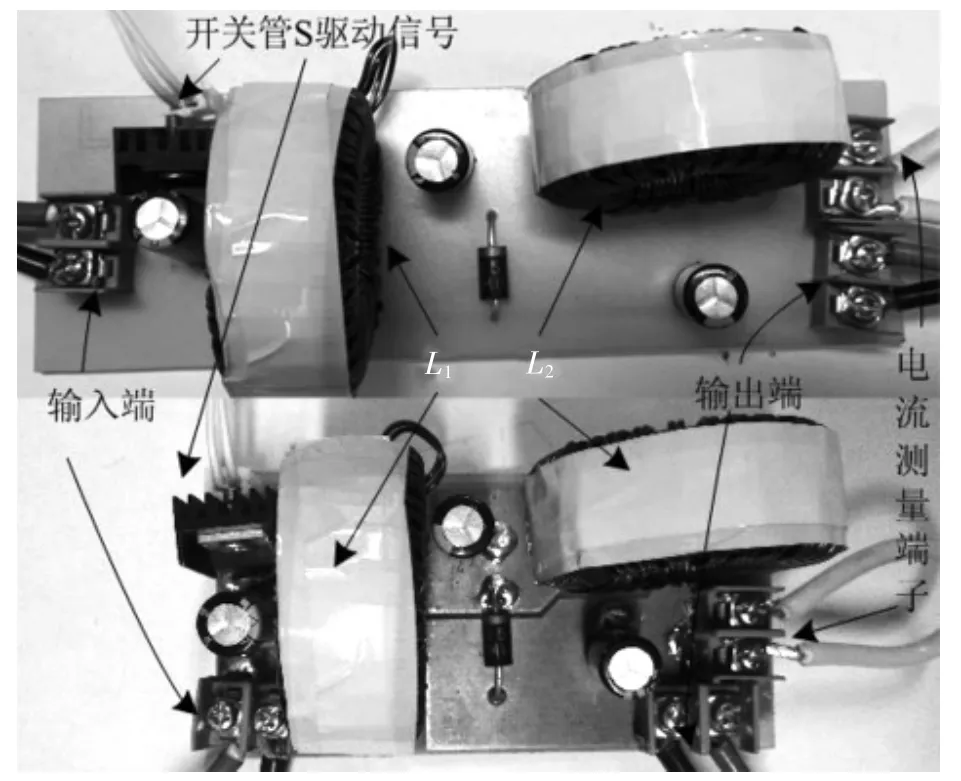

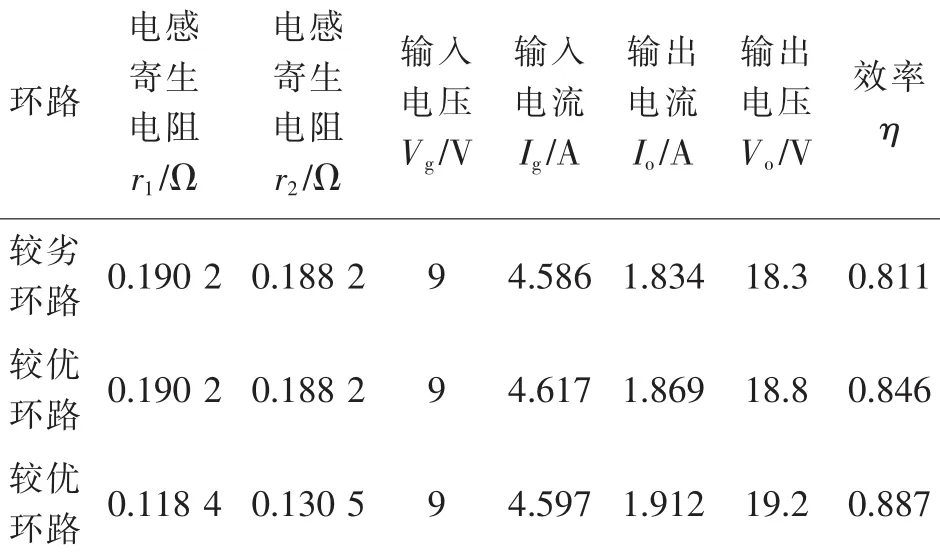

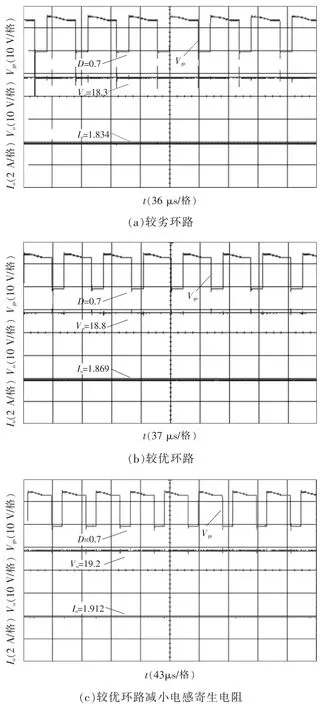

2台50W实验样机如图12所示。图中上侧为较劣PCB环路,单面板绘制,下侧为较优PCB环路,双面板绘制,对两台样机进行对比验证,并在较优环路下,比较了r1、r2对变换器性能的影响。电路参数如表2所示,相关实验数据如表3所示。开环实验波形如图13所示,输入、输出电压与占空比的闭环实验波形如图14所示。

图12 实验样机Fig.12 Experimental prototype

表3 实验数据Tab.3 The experimental data

由表3可知,优化环路与减小电感寄生电阻可改善变换器电压增益、提高工作效率,由图14可知,相同的输入电压,寄生参数较大的样机需要更多的占空比输出才能达到相同的输出电压。与之前理论分析及仿真结果基本相符。

由此,设计变换器时应尽可能优化电路板布局布线,减小高频环路,使功率线粗且短,减小环路寄生电阻,选择较小寄生电阻的电感等储能元器件,如电感绕线可采用高磁导率、低电阻率材料或是双匝绕线绕制。改善变换器电压增益、提高工作效率,减少变换器损耗。

图13 实验波形Fig.13 Experimental waveforms

图14 输入、输出电压与占空比的闭环实验波形Fig.14 Closed loop experimental waveforms of input voltage,output voltage with duty

4 结语

本文以Zeta变换器为例研究元器件及PCB环路寄生电阻对DC-DC变换器电压增益、效率的影响,由状态空间平均法建立其数学模型,定量分析变换器电压增益和效率的表达式,对电路设计及参数选型给出指导性建议,分析了各寄生电阻对电压增益、效率造成的影响,推导出各个元器件寄生电阻对变换器电压增益、效率影响的比重,为设计变换器时,有选择地进行电路优化提供了理论依据。最后进行仿真与样机实验验证理论分析正确性。

[1]王兆安,刘进军.电力电子技术[M]. 5版.北京:机械工业出版社,2009:5.

[2]沈健,刘鸿鹏,王卫.高升压比DC-DC变换器的研究[J].电源学报,2014,12(5)∶1-6. Shen Jian,Liu Hong-peng,Wang Wei. Resesrch on high step-up ratio DC-DC converter[J]. Journal of Power Supply,2014,12(5)∶1-6(in Chinese).

[3]左龙,廖勇.车用双向DC/DC控制策略研究及参数选择[J].电源学报,2014,12(2)∶62-68. Zuo Long,Liao Yong. Control strategy study and control parameter selection forBi-DC/DC converter of electric vehicle[J]. Journal of Power Supply,2014,12(2)∶62-68(in Chinese).

[4]Tseng K C,Liang T J. Novel high-efficiency step-up converter[J]. IEEE Trans. IEE Proc. -Electr. Power Appl,2004,151(2):182-190.

[5]Li Y,Jiang S,Cintron-Rivera J G,et al. Modeling and control of quasi-Z-source inverter for distributed generation applications[J]. IEEE Trans. on Industrial Electronics,2013,60(4)∶1532-1541.

[6]Johnson H,Graham M.High-Speed Digital Design[M]. Prentice Hall PTR,1993.

[7]Brooks D. Signal Integrity Issues and Printed Circuit Board Design[M]. Prentice Hall PTR,2003.

[8]李建兵,胡长超,朱忠义.平面变压器寄生参数分析[C].中国电工技术学会电力电子学会第十一届学术年会,2008. Li Jianbin,Hu Changchao,Zhu Zhongyi. Planar Transformer Parasitic Parameter Analysis[C]. the 11th Academic Annual Meeting on China Electrotechnical Society(CES),2008(in Chinese).

[9]L B Gravelle and P F Wilson. EMI/EMC in print circuit boards A literature review[J].IEEE Transactions on Electromagnetic Compatibility,1992,34(2)∶109-116.

Research on Effect on DC-DC Converter Caused by Parasitic Resistance

YUAN Hong,DING Xinping,WANG Borong,MOU Wei,YANG Chao

(College of Automation Engineering,Qingdao Technological University,Qingdao 266520,China)

This paper discusses numerical quantitative relation ship among voltage gain,work efficiency and components and circuit board parasitic of DC-DC converter. Firstly it uses Zeta converter as an example to discover influence factors on voltage gain and work efficiency using state space averaging method and establishe expressions regarding gain,efficiency with circuit parameters including parasitic resistance. Then,the reasons why voltage gain drops and efficiency declines are investigated. The impacts on voltage gain and efficiency of components and PCB loop parasitic resistance are studied to get the ratio of impacts of each parasitic resistance on voltage gain and efficiency. Thus,the ratio can provide theoretical basis for circuit design and selecting optimal circuits. Finally,two circuit prototypes of 50 W are built in the lab,and the combining simulation and experimental results verify the accuracy of theoretical analysis.

DC-DC converter;voltage gain;work efficiency;parasitic resistance

苑红

2015-07-30

国家自然科学基金资助项目(51477079);中国博士后科学基金资助项目(2013M531598)

苑红(1990-),男,硕士研究生,研究方向为电力电子拓扑结构及新型单级可升压逆变电路研究,E-mail∶yuanhong6075 @163.com。

丁新平(1975-),男,通信作者,博士,副教授,研究方向为新能源发电电能转换、DC-DC高效转换电路及新型单级可升压逆变电路研究,E-mail∶dxinping@126. com。

王伯荣(1989-),男,硕士研究生,研究方向为新型单级可升压逆变电路研究,E-mail∶wbr6ts@163.com。

牟伟(1989-),男,硕士研究生,研究方向为新型单级可升压逆变电路研究,E-mail∶mouwei6666@126.com。

杨超(1990-),男,硕士研究生,研究方向为新型单级可升压逆变电路研究,E-mail∶xinqijiayu@163.com。