基于流水线法的新型EDA优化技术的研究

赵建飞,张 悦

(青海师范大学, 青海 西宁 810008)

基于流水线法的新型EDA优化技术的研究

赵建飞,张悦

(青海师范大学, 青海 西宁810008)

摘 要:EDA代表了当今电子设计技巧的最新发展方向,利用EDA工具,电子设计师可以从概念、算法、协议等开端设计电子系统,大批工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设出IC版图或PCB版图的全部过程在汁算机上主动处理完成。但EDA技术在优化方式上,却存在着一定的弱势,本文提出的流水线法新型优化方式,是指把耗时较长、单时钟周期内难以完成的并行执行的逻辑块分割开,提取出相同的逻辑模块,在时间上复用该模块,用多个时钟完成相同的功能,然后对耗时较长的模块进行分解,分解的原则为各个子模块逻辑延时大致相当,从而能够大幅度的提升物理电路性能,能在一定程度上解决EDA技术优化不足的问题。

关键词:EDA;流水线;优化;延时;时钟频率

1EDA技术概述

EDA[1]是电子设计自动化(Electronic Design Automation)的缩写,在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译[2]、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。引入一种新型的流水线优化方式,可以使通过EDA工具进行的电子设计在一定程度上,占用的芯片面积不变的情况下,速度能够大幅度提升。

2.流水线原理

流水线[3](pipeline)技术是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。流水线是Intel首次在486芯片中开始使用的。流水线的工作方式就象工业生产上的装配流水线。在CPU中由5~6个不同功能的电路单元组成一条指令处理流水线,然后将一条X86指令分成5~6步后再由这些电路单元分别执行,这样就能实现在一个CPU时钟周期完成一条指令,因此提高CPU的运算速度。经典奔腾每条整数流水线都分为四级流水,即取指令、译码、执行、写回结果,浮点流水又分为八级流水。

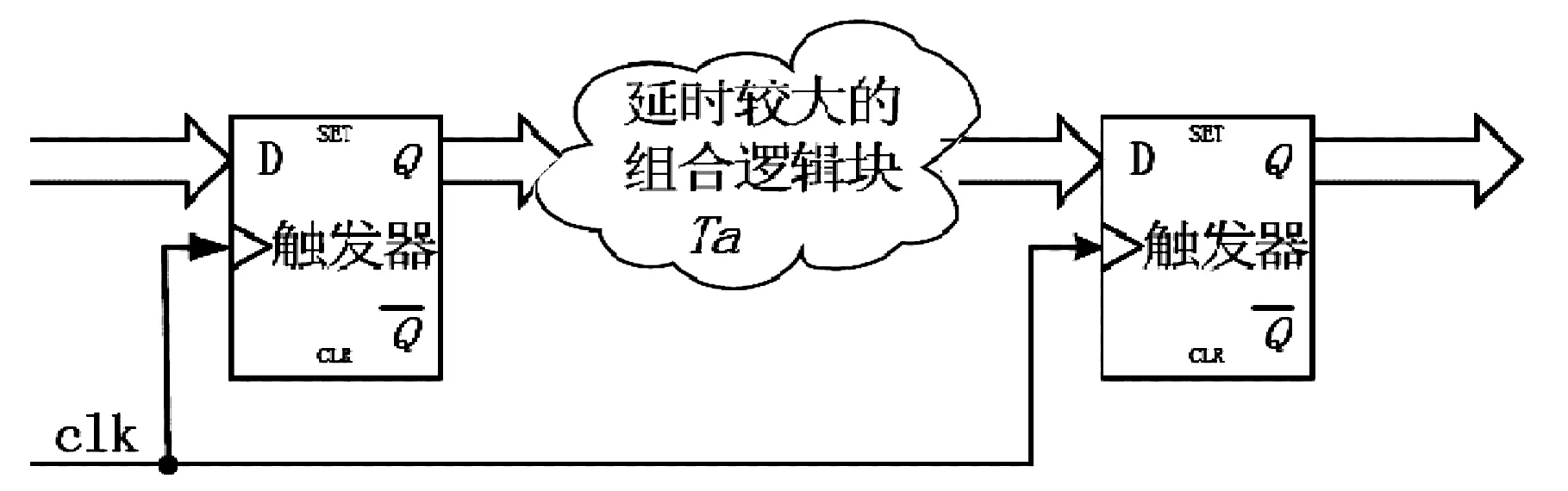

借鉴流水线技术,从代码的角度对耗时较长的模块,进行逻辑分割,分解成耗时相当的子逻辑模块[4],图1为未优化逻辑模块,其理论最高时钟频率为1/Ta(Mhz)。由此可见逻辑模块延时越大,其时钟频率越低,电路的性能也就越差。

图1 未优化逻辑模块

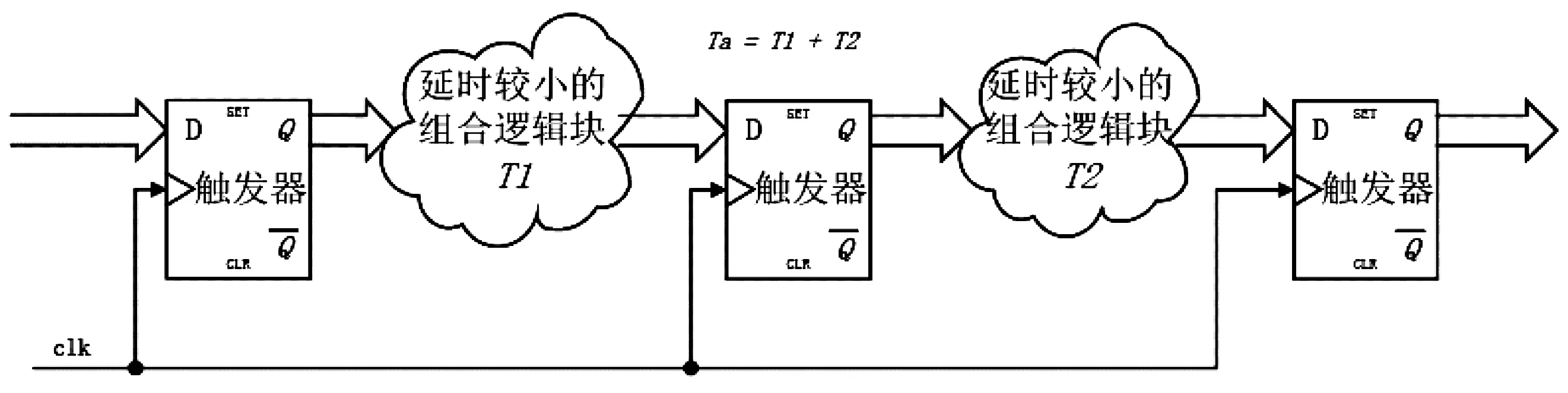

图2为优化原理图,将Ta延时进行分解为T1和T2两个延时子模块,其理论最高时钟频率为2/Ta(Mhz),当分解为N个延时子模块时,其理论最高时钟频率[5]为N/Ta(Mhz),因此流水线对于提高电路的时钟频率来说是非常有效的。

图2 优化逻辑模块

3未优化代码分析[1]

3.1部分代码

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entity adder4 is

port(clk:in std_logic;

a0,a1,a2,a3:instd_logic_vector (7 downto 0);

yout:outstd_logic_vector ( 9 downto 0));

endadder4;

architecturea of adder4 is

signal t0,t1,t2,t3:std_logic_vector (7 downto 0);

signal addtmp0,addtmp1:std_logic_vector (8 downto 0);

begin

process (clk ) begin

ifclk'eventand clk='1'then

t0<=a0;t1<=a1;t2<=a2;t3<=a3;

end if;

end process;

addtmp0<='0'&t0+t1;

addtmp1<='0'&t2+t3;

process (clk ) begin

ifclk'eventand clk='1'then

yout<='0'&addtmp0+addtmp1;

end if;

end process;

end a;

3.2实验结果

综合结果:适配至EPM712884-15

用67个逻辑单元,

资源占用率52%。

时序逻辑性能分析:

最小时钟周期65ns

最高时钟频率15.38 MHz

4优化代码分析

4.1部分代码

libraryieee;

useieee .std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

architecturea of lsadder4 is

signal t0,t1,t2,t3:std_logic_vector (7 downto 0);

signal addtmp0,addtmp1:std_logic_vector (8 downto 0);

begin

process (clk )

begin

ifclk'eventand clk='1'then

t0<=a0;t1<=a1;t2<=a2;t3<=a3;

end if;

end process;

process (clk )

begin

ifclk'eventand clk='1'then

addtmp0<='0'&t0+t1;

addtmp1<='0'&t2+t3;

end if;

end process;

process (clk )

begin

ifclk'eventand clk='1'then

yout<='0'&addtmp0+addtmp1;

end if;

end process;

end a;

4.2生产电路

综合结果:适配至EPM712884-15

用67个逻辑单元,

资源占用率52%。

时序逻辑性能分析:

最小时钟周期39ns

最高时钟频率25.64 Mhz

5总结及其展望

由上述分析可以看出,通过新型流水线法的优化方式,可以很大程度上提高芯片面积的使用效率,如:未优化时,适配[6]至EPF10K20TC144-15用67个逻辑单元,资源占用率52%,最小时钟周期65ns,最高时钟频率15.38 MHz;而优化以后,适配至EPF10K20TC144-15用67个逻辑单元,资源占用率52%,最小时钟周期39ns,最高时钟频率25.64 Mhz;显而易见,通过流水线法的方式进行优化,原芯片使用面积不变的情况,芯片的速度提升比为25.64Mhz/15.38Mhz=1.667,总体优化效果非常好。随着时钟频率的不断提高,流水线法优化带来的硬件运行速度的提升是非常明显的,因此,流水线法优化方式将会成为未来一种非常有实际意义的新型优化方式。

参考文献:

[1]谭汇生,张昌凡.编著.EDA技术及应用[J].苏州大学出版社,2001.

[2]潘松,黄继业.编著 EDA技术使用教程[J].科技出版社,2002.

[3]王锁萍.编著.电子设计自动化(EDA)教程[J].电子科技大学出版社,2000.

[4]IEEE Standard VHDLLanuage Reference Manual.IEEE Press,1987.

[5]VHDL Language ReferenceGuide,Alde Inc.Henderson NV USA,1999.

[6]赵建飞.基于串行法的新型EDA优化技术的研究[J].现代电子技术,2015,15:110-111.

EDA Optimization Techniques Based Serial Method

ZHAO Jian-fei,ZHANG Yue

(Qinghai Normal University,Qinghai Xining 810008)

Abstract:EDA represent the latest development of today's electronic design skills,the use of EDA tools,electronic designers can design concept from the beginning,algorithms,protocols and other electronic systems,a large number of work can be done by computer and electronic products can be from the circuit design,performance analysis to set up the whole process of IC layout or PCB layout on the computer initiative juice processing is completed.But EDA technology in the optimization of the way,but there are some weak pipeline of new optimization method presented herein,refers to the time-consuming,difficult to complete a single clock cycle logic block parallel execution split open to extract the same the logic module,in time multiplexing principle of the module,with multiple clock accomplish the same function,and then lengthy modules the decomposition of each sub-module logic delay roughly,thereby greatly enhance physical circuit performance,can solve the problem of insufficient EDA technology to optimize certain extent.

Key words:EDA;pipeline;optimization;delay;clock frequency

收稿日期:2015-11-11

基金项目:东乡族文献资料数据库建设研究(15XTQ007)

文章编号:1007-2934(2016)02-0097-03

中图分类号:O 4-39

文献标志码:A

DOI:10.14139/j.cnki.cn22-1228.2016.002.026