存储式弹丸破片速度测试装置设计及应用

钱礼华,陈亚奇,申晓敏,朱轶龙,白 蕾

(中国兵器工业试验测试研究院,陕西 华阴 714200)

存储式弹丸破片速度测试装置设计及应用

钱礼华,陈亚奇,申晓敏,朱轶龙,白蕾

(中国兵器工业试验测试研究院,陕西 华阴714200)

摘要:对目前常用的3种弹丸破片速度测试方法包括梳状靶、断靶和光电靶进行了比较分析,针对原有测试方法的缺陷和不足,研制了存储式弹丸破片速度测试装置,并对其设计方法及实际应用情况进行了分析。该测试方法提高了试验的可靠性,减少了测试工作量,取得了较好的使用效果。

关键词:弹丸破片;速度测试;存储记录

弹丸破片速度是考核弹丸杀伤能力与破片动能的主要依据。目前常用的弹丸破片速度测试方法主要有以下3种。第1种采用通靶(如梳状靶)、信号调理器和数据采集系统组成;第2种采用断靶(如网靶)和测时仪组成;第3种采用非接触的光电靶和数据采集装置等组成。

目前在30~155 mm弹丸和导弹战斗部静爆试验中测试预制破片和自然破片速度测试采用通靶、信号调理器和数据采集系统的应用最为广泛。通过靶场多次采用该类测试系统,其不足主要表现:

1) 梳状靶、信号调理和数据采集系统间需要较长的信号电缆,现场电缆在爆炸和弹片集中区域防护困难;

2) 破片信号记录采用数据采集系统,目前主要采用220 V 交流供电,还需要配置发电机和防护钢壳掩体。试验中还出现过因爆炸振动大发电机熄火引起掉电导致数据未记录等问题。

针对以上不足,综合考虑目前存储技术发展,进行存储式弹丸破片速度测试装置设计。

1测试系统组成和工作原理

1.1系统主要技术指标

存储式弹丸破片速度测试装置主要技术指标如下:

1) 通道数:8

2) 时间分辨率:1 μs

3) 计时范围: 2 s

4) 工作时间:不小于8 h

5) 供电方式:内部电源

6) 抗电磁干扰:2 000 V

1.2测试系统组成

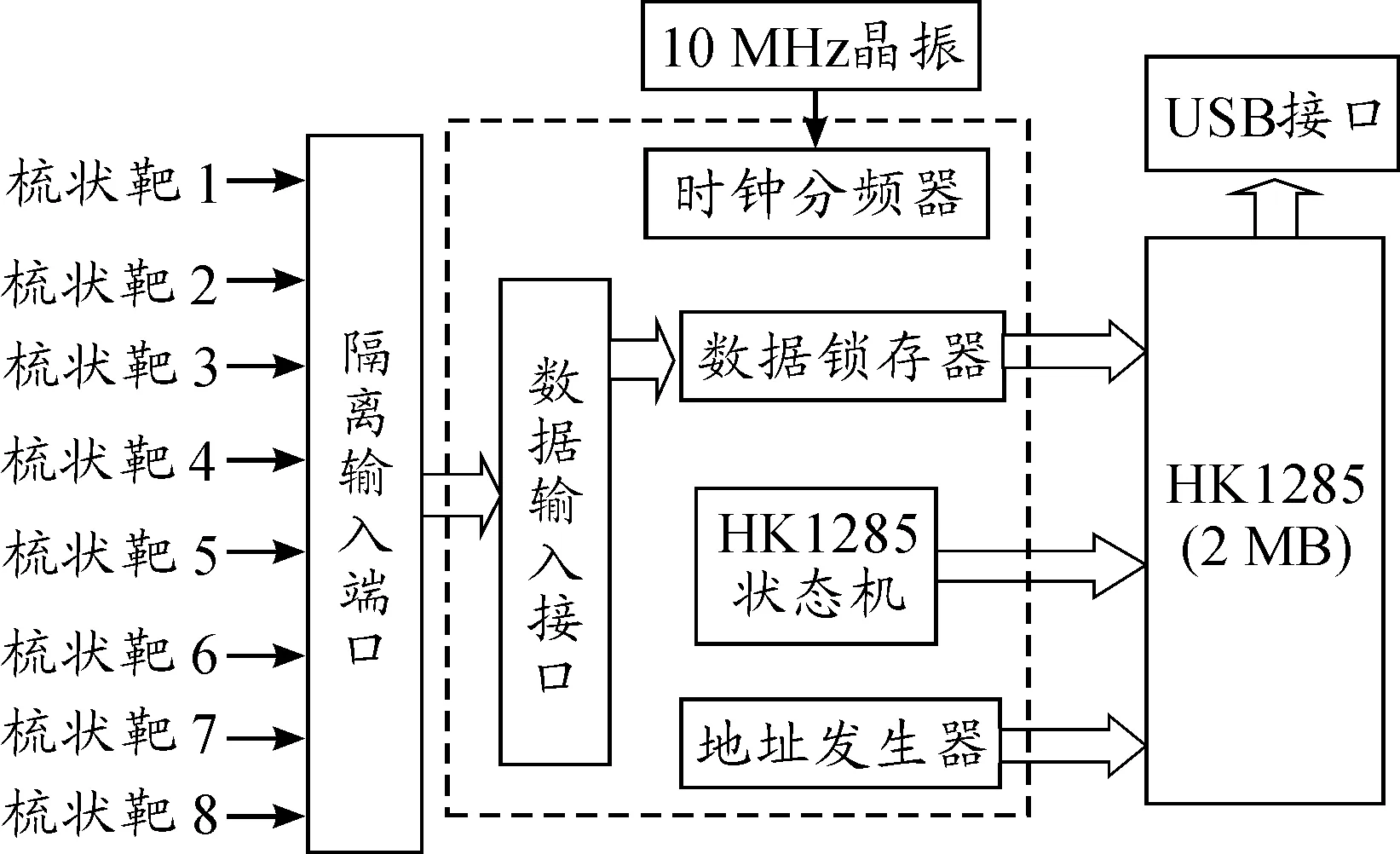

存储式弹丸破片速度测试装置由梳状靶(通靶)信号调理电路、数据存储、USB数据接口和电源等部分组成,其原理框图如图1。

图1 存储测试装置原理框图

1.3工作原理

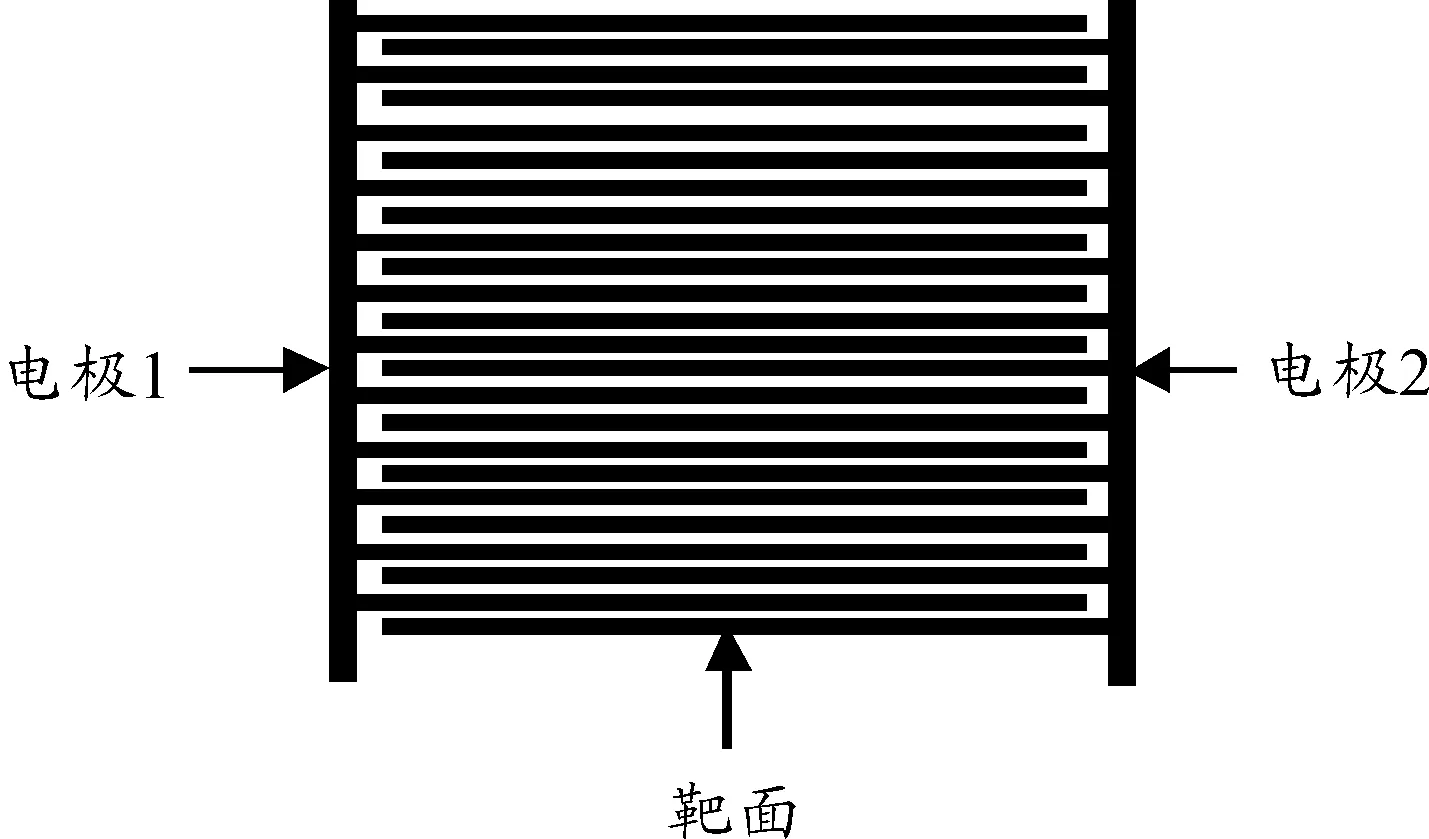

梳状靶作为一种典型的通靶,采用印刷电路板工艺制作,通常为开路状态(图2)。破片速度试验中,通常在距爆心6 m、8 m、10 m和12 m距离分别架设一块梳状靶,每路梳状靶的信号通过信号线连接至靶附近的存储式弹丸破片速度测试装置的输入端,同时在弹丸起爆位置布设断靶线。弹丸起爆后,断靶线断开,存储测试装置接收到启动信号开始记录,金属弹片穿过梳状靶靶面时将其两相邻电极接通,此刻为短路状态,装置可以将8路信号分别调理成为从低到高的阶跃电压信号进入后续信号存储电路进行记录,可得到弹片起爆到经过各个架设点的时刻,通过时刻与距离计算出破片到靶面的平均速度,通过破片到达不同距离梳状靶的速度可以推算出破片初始速度。

图2 梳状靶示意图

电路由CPLD器件作为主控,其完成信号锁存、时钟分频、数据存储、数据输出等一系列时序和信号控制[1-3]。

工作流程为:首先设定为采集状态工作;接通内部电源,进行准备采集状态,加电时进行上电复位,将内部计数器和地址发生器清零;弹丸爆炸后触发电路开始进行数据记录,此时存储地址线按照采集时钟进行推进,当地址达到预设值时,产生结束信号完成采集。试验结束后采用计算机的USB接口进行数据读取。

2系统设计

2.1梳状靶信号调理电路设计

试验中梳状靶架设在爆心附近,战斗部爆炸时会产生大量的“火花”,继而产生的电磁信号会通过梳妆靶上的信号线进入测试装置,引起强烈的电磁干扰,在数据采集时测试系统经常可以采集的大量干扰信号。如果不采取信号隔离,杂乱的干扰信号会影响有效信号的分析。因此在梳状靶信号调理时需要进行信号隔离电路设计。

电路隔离主要有:模拟电路的隔离、数字电路的隔离、数字电路与模拟电路之间的隔离。所使用的隔离方法有:变压器隔离法、继电器隔离法、光电耦合器隔离法、线性隔离放大器隔离法、光纤隔离法等[4-5]。

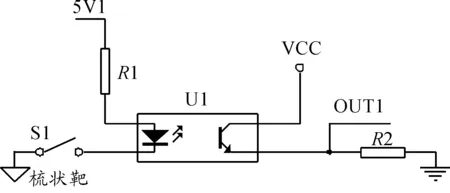

本次设计采用简单有效的光耦隔离方式,使信号输入端与采集端两部分电路之间没有电的直接连接,使隔离两端分别采用不同的接地点,切断了“地”干扰的传播途径,使干扰信号无法进入后续电路,有效地抑制了尖脉冲和各种噪声干扰。

如图3所示,实际测试中通过信号电缆线将梳状靶输出端连接至S1的两端,当弹片通过梳状靶面时瞬间接通S1,光耦输出从低至高的阶跃电压信号,这样就将通靶(断通信号)转换为上升沿信号。

图3 梳状靶信号调理电路

2.2数据存储电路设计

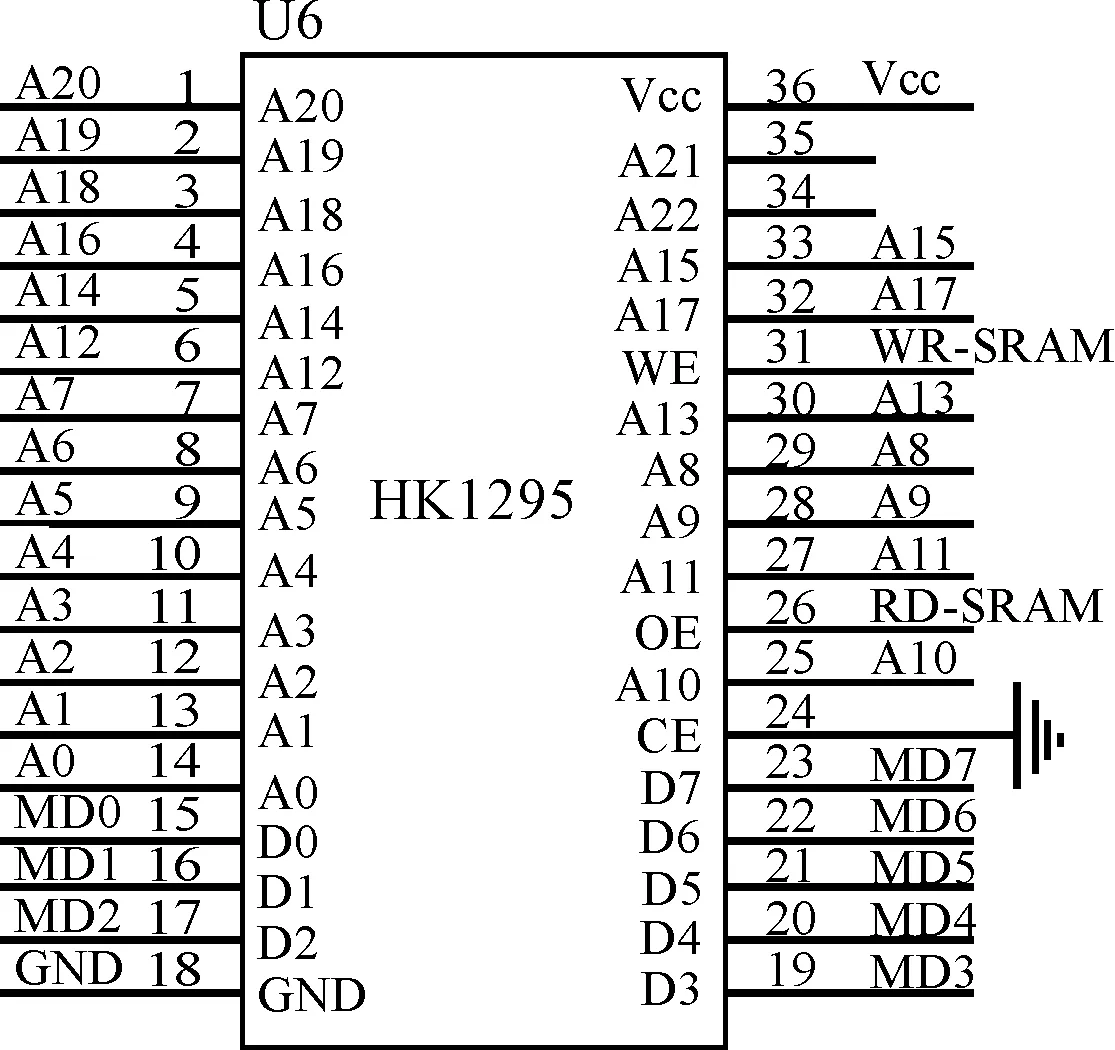

在数据采集存储电路中,目前主要有FLASH、SRAM、SDRAM等存储方案可供选择。在本次设计中综合考虑整体电路的体积、功耗、存储速度和容量等因素,尤其考虑实际中的电路瞬间掉电等极端情况下数据存储的可靠性,因此选取非易失芯片(NVRAM),其在数据记录后掉电数据不会丢失(理论保持20年),就减小了因电源不稳定造成数据丢失的可能性。在设计中选取2MB存储器HK1285。其为HongKong公司的2M×8位的NVSRAM,包括21位地址总线,8位数据线。电路图4所示。

HK1285的写模式时序如图5所示。地址输入稳定后,HK1285 在WE和CE信号处于激活(低电平)状态为写模式。最后出现的CE或WE下降沿将决定写循环的开始,循环终止于CE或WE前边的上升边沿。在写循环内所有地址输入必须保持有效。在下一个循环能被初始化前,WE写信号必须将高电平保持最少记录时间(tSA)。写循环期间OE控制信号应当保持失效(高电平)。避免总线冲突,如果输出总线已经有效(CE和OE激活),则写信号可以在tPWE时序内从下降边沿开始禁止输出。

图4 NVRAM HK1285

图5 HK1285写模式时序

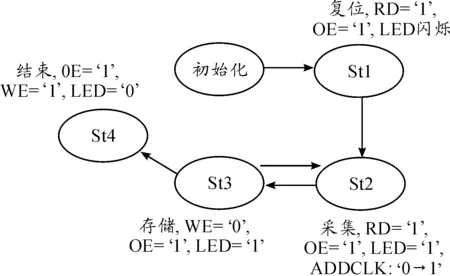

2.3状态机设计

梳状靶信号的采集和存储控制主要有5个状态,状态机如图6。首先是初始化状态St0,分别设置内部寄存器和读写控制端,WE=‘1’、OE=‘1’;状态St1时,对内部计数器和地址发生器进行自动复位, RD=‘1’、OE=‘1’、状态指示的LED闪烁; St2为数据采集状态,判断触发信号到来时,对数据进行锁存,产生地址推进脉冲,RD=‘1’、OE=‘0’、状态指示的LED常亮;St3为数据存储状态。St3时首先判断地址状态,如果未到上限则进行数据存储,WE=‘0’、OE=‘1’、 状态指示的LED常亮;St3完成后在St2和St3间循环,如果达到地址上限则进入St4,其为结束状态,WE=‘1’、OE=‘1’、 状态指示的LED熄灭。

图6 采集存储状态机

2.4软件设计

采集的梳状靶数据每帧为8位数字量,每位表示一路梳状靶的通和断状态,高电平表示接通状态、低电平表示断开状态。数据处理时首先将要数据的8个位分离开,形成8个独立的数据文件。分析时,根据判断每路曲线的高低电平和对应时间关系,可得到弹片经过对应梳状靶的时间序列。

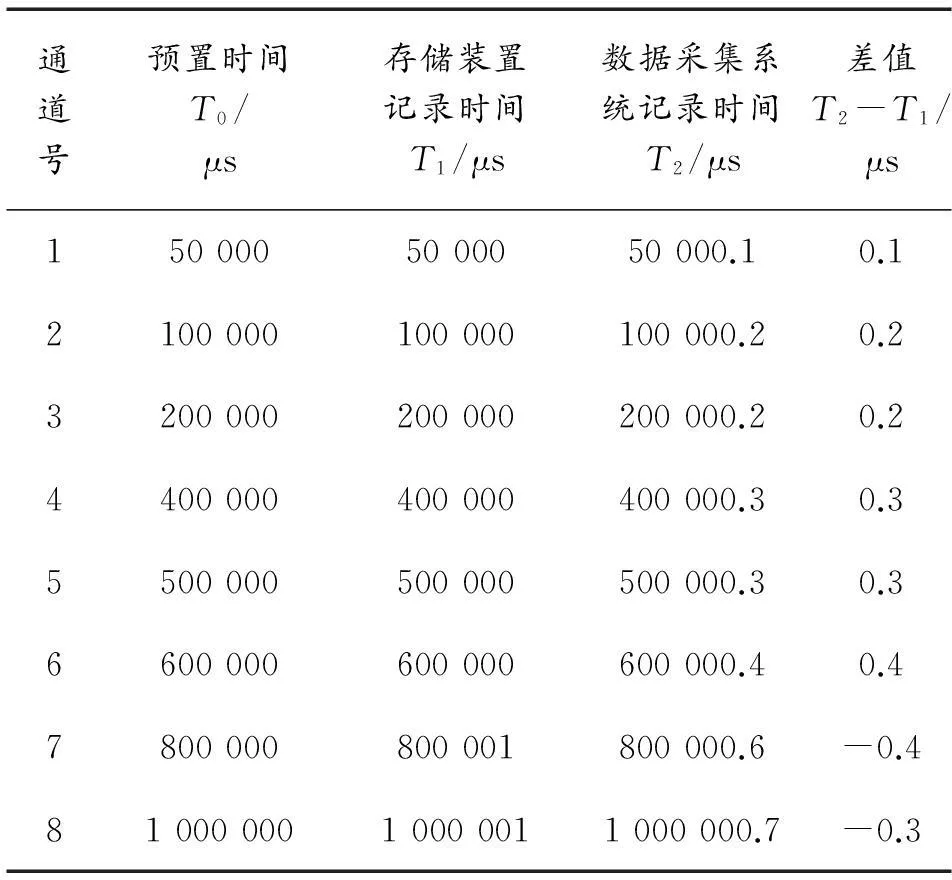

3实验室检测

实验室对存储装置进行检测采用专用的时间序列发生器进行脉冲输出,数据同时采用采样率为10 Msps的数据采集系统检测,其原理示意图如图7。检测结果如表1所示。

通过检测结果可看到,数据采集系统记录时间和存储装置记录时间差值均小于1 μs,其满足设计需求。

图7 检测原理示意图

通道号预置时间T0/μs存储装置记录时间T1/μs数据采集系统记录时间T2/μs差值T2-T1/μs1500005000050000.10.12100000100000100000.20.23200000200000200000.20.24400000400000400000.30.35500000500000500000.30.36600000600000600000.40.47800000800001800000.6-0.48100000010000011000000.7-0.3

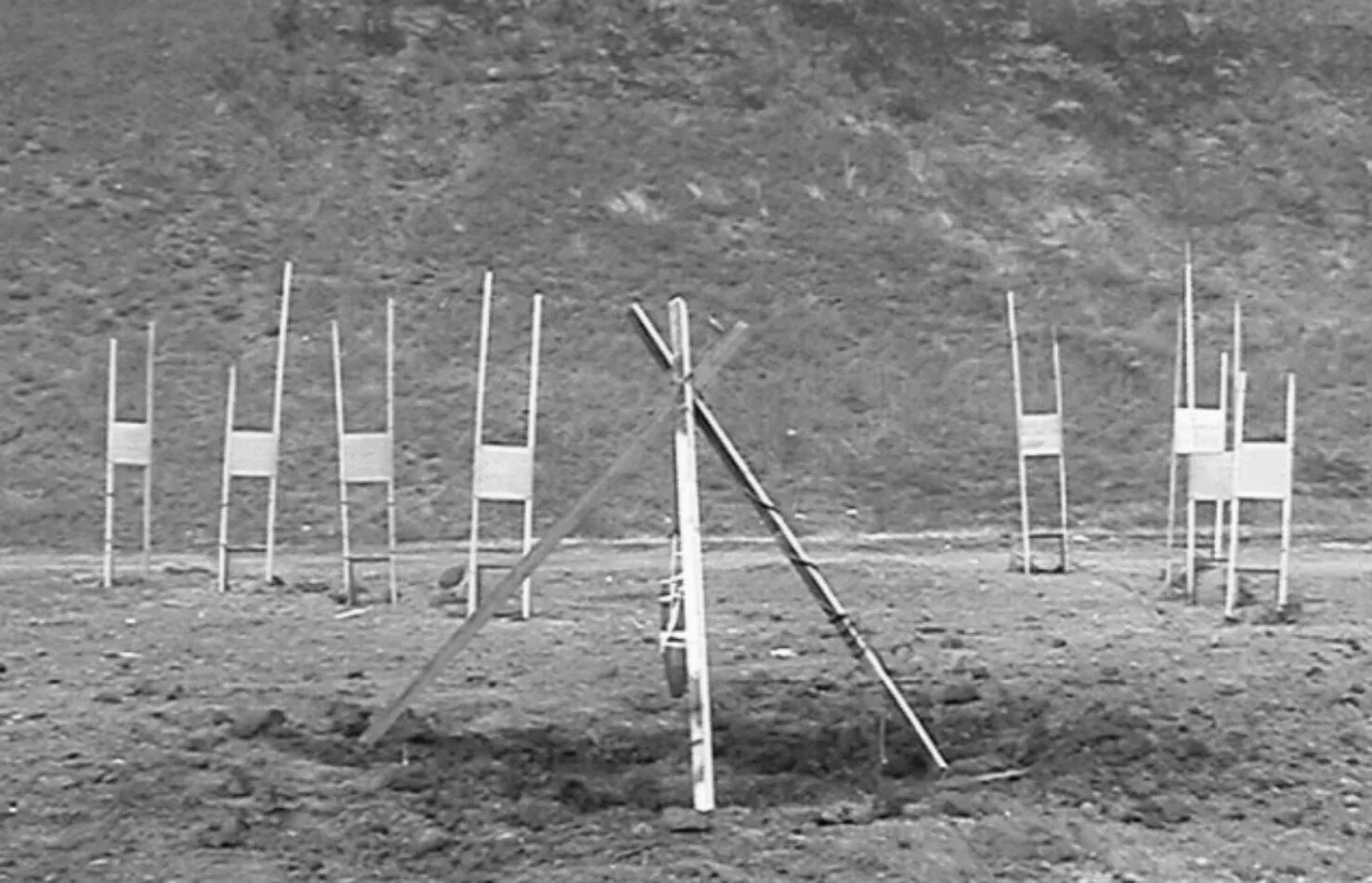

4实际应用

通过在多次火箭橇试验断靶和静爆试验中应用,存储式弹丸破片速度测试装置的抗强电磁干扰能力、测试精度和可靠性均满足实际测试需求。存储式弹丸破片速度测试装置实物如表8所示,试验现场图如图9所示。

图8 存储式弹丸破片速度测试装置

图9 试验现场场景

5结论

本研究采用信号调理电路和CPLD芯片,设计了存储式弹丸破片速度测试装置,通过实验室检测和实际应用,证明该装置可以取代原有的大型数据采集系统加长信号线的测试方式。该测试装置体积小,使用方便灵活,给测试带来了较大便利。同时由于该装置不需要长信号线,减小了信号干扰,提高了测试可靠性。

参考文献:

[1]王芳.CPLD/FPGA技术应用[M].北京:电子工业出版社,2011.

[2]姜付鹏.电磁兼容的电路板设计[M].北京:机械工业出版社,2011.

[3]王海福.爆炸冲击波存储测试系统研究[D].北京:北京理工大学,2002.

[4]张文栋.存储测试系统的设计理论及其应用[M].北京:高等教育出版社,2002.

[5]李杨,斩鸿,张志杰.CPLD在飞行体加速度测量中的应用[J].仪器仪表学报,2006(S3):2400-2401.

(责任编辑杨继森)

本文引用格式:钱礼华,陈亚奇,申晓敏,等.存储式弹丸破片速度测试装置设计及应用[J].兵器装备工程学报,2016(4):114-117.

Citation format:QIAN Li-hua,CHEN Ya-qi,SHEN Xiao-min,et al.Design and Application of the Storage-Type Speed Test Device for Fragment[J].Journal of Ordnance Equipment Engineering,2016(4):114-117.

Design and Application of the Storage-Type Speed Test Device for Fragment

QIAN Li-hua,CHEN Ya-qi,SHEN Xiao-min,ZHU Yi-long,BAI Lei

(Test and Measuring Academy of Norinco. Group,Huayin 714200, China)

Abstract:Three common fragment test methods,including comb target,broken target and photoelectric target during speed test for fragment, were compared and analyzed. We developed the storage-type speed test device for fragment aiming at defects and deficiencies of original test methods,as well as described its design method and actual application in details. Such test method improves test reliability,and reduces test quantity and obtains better use effect.

Key words:projectile fragment; speed test; storage record

文章编号:1006-0707(2016)04-0114-04

中图分类号:TJ011.+2

文献标识码:A