FPGA与PCM—9575嵌入式计算机异步通信的设计与实现

摘 要:短波发射机自动调谐系统采用FPGA与嵌入式计算机来实现各自的功能,其中他们之间的异步通信的设计是很重要的环节,其实用性、可靠性是需要考虑的主要方面,文章介绍利用ISE设计平台采用层次化设计方式实现二者之间的通信,取得了良好的效果。

关键词:异步通信嵌入式主板;FPGA;RS232;HDLC;FIFO

1 概述

短波(3.9MHZ-26.1MHZ)发射机更换工作频率时为了保证发射机能正常工作在所需的频率值,必须使高频回路各个调谐器件在步进电机的带动下转动到相应的频率的位置上。TBH522型150KW短波发射机数字化自动调谐系统采用XC2S200设计实现对8路步进电机位置的采集、转动控制、及其他逻辑控制功能;使用台湾生产的PCM-9575嵌入式主板实现与上位机通信、调谐频率数据库的存储、发射机模拟量采集、人机对话界面等功能。由于该嵌入式主板有现成的RS232接口,我们对FPGA设计异步通信宏模块,实现其与嵌入式主板通信,通信方式采用国际标准电子工业联合会(EIA)定制的RS232标准,通信协议采用的是高级数据链路控制协议(HDLC)协议,负责传送步进电机的预置位置、实际位置、键盘数据、频率以及一些控制命令等数据。

2 FPGA异步通信总的设计思想

RRI和TRO为异步通信输入输出引脚,嵌入式计算机COM口设置为9600波特率、1位奇偶校验位、1位停止位。CLK为系统时钟16MHz。

LOAD信号只在接收到实际位置的时候维持大约4us的高电平,在其他状态为低电平,在高电平时将步进电机实际位置计数器置数,低电平时步进电机实际位置计数器计数。

发送程序启动时,不断扫描8路地址的总线,从第1路到第8路连续发送8帧数据,然后再重新扫描。

接收程序接收到数据后将数据锁存到总线上,内部设有差错处理功能,当帧结构不正确或一帧数据不完整将不会把数据送到总线上。

2.1 层次化设计

异步通信模块涉及到的RS232通信标准和HDLC协议控制都比较复杂,从通信的层次来说,RS232数据底层的通信协议,HDLC协议控制数据高层协议控制,当完成了底层的RS232通信的设计后,高层协议HDLC只需要按照其协议规定的数据格式调用底层的通信协议将一帧数据发送出去即可。在接收时,接受完一帧数据后,在按照协议规定的数据格式将数据“剥离”开,在按照数据的地址分配到相应的总线上即可。

2.2 数据处理的要求

从本设计的需求来说,异步通信模块与嵌入式计算机通信的数据量并不是很高,与嵌入式计算机通信所定义的HDLC协议也十分简单,没有规定过多的应答数据;硬件上也采用SPI的3根线,即接收、发送和地线,没有其它的应答信号。异步通信模块与嵌入式计算机通信是一个被动的过程,在这种情况下,可以想象,嵌入式计算机向FPGA发送数据在时间上具有一定的随机性,可以发完一帧数据后马上发送下一帧数据,或者等待一段时间后再发送一帧数据,而FPGA接收数据是以帧为单位进行接受,即每次接受一帧数据送入缓存器中,然后将缓存器中的数据进行处理,处理完毕后再接收下一帧数据,而对于这种被动的接收势必对处理的速度有很高的要求,即接收到一帧数据后,迅速将数据读出,清空缓冲区,等待下一帧数据的到来。

在发送上也采取这种策略,将所要发送的数据迅速装入缓冲区,做到不影响发送数据的连贯性。

为了提高读写速度,缓冲区采用同步先入先出堆栈(fifo),不用送地址,只要将读、写信号有效,然后送时钟信号即可进行数据的高速度写。

为了保持数据的可靠性,在接收上要做一定的差错控制。

3 内部模块设计与实现

异步通信模块主要由发送部分和接收部分组成,设计利用ISE平台实现,全部采用VHDL语言完成每个子模块的设计。

3.1 发送部分

发送模块功能是将8路步进电机实际位置的总线上的数据按照HDLC协议通过串行通信发送到嵌入式计算机中。主要包括复位电路模块(reset_core)、发送控制模块(transtmit_ctrl)、波特率分频模块(fen)、HDLC协议控制时钟分频模块(FEN_HDLC)、先入先出堆栈(FIFO_T)、HDLC协议控制模块(TX_HDLC)、异步通信发送模块(UART_T)等7个模块。

3.1.1 reset_core模块

该模块负责在上电后维持1μs的高电平,将内部工作的所有模块中的状态机复位,然后维持低电平,让内部模块开始工作。

3.1.2 transtmit_ctrl模块

此模块的功能是将8路步进电机的实际位置循环扫描写入到FIFO_T堆栈中,特点是:(1)快速写入数据,采用系统时钟16MHz,用5个周期完成一个数据的写入。相对于9600波特率的异步通信来说,此速度能够保持发送数据的连贯性,保证系统的实时性。(2)写入FIFO_T中的数据格式按照先后为:地址位——数据位高字节——数据位低字节。(3)利用状态机控制,并且在控制上采用控制信号和数据传输与处理分开,利用状态机组合进程产生控制信号,在其它进程利用前者产生的控制信号控制数据的传输与处理,确保数据传送有足够的建立时间和保持时间,保证数据的稳定和可靠。此状态机充分考虑了和其他模块之间信号的通信,数据稳定的建立、保持时间。完成后的状态机将要发送的数据送到了深度为3个字节的FIFO模块中,并且控制HDLC模块将数据读出发送出去。(4)状态机组合逻辑进程,该进程在各个控制信号定义是尽量保持控制信号只在一个状态有效,避免状态转换过程中出现毛刺。在此进程中并没有进行数据的传输,只是通过状态的转换送出控制信号。(5)描述键盘状态缓冲器信号进程。在上一个进程中可以看到,当键盘状态缓冲器为低电平时,地址指向键盘地址,此时若模块处于向堆栈数据过程中,很容易将先前的数据覆盖,所以该信号应该保证在写堆栈到来期间无效,并且在完成后联合调试过程中发现,每次按键应该保证只向嵌入式计算机发送一次数据,多次发送将会引起嵌入式计算机的误动作。该进程的功能就是使得每次按键后在等待发送数据过程中将键值捕获,然后保证只发送一次。(6)键盘状态寄存器描述进程,该进程是用键盘到来信号缓冲器来锁存键盘状态寄存器,使得数据能够保持一个完整地写周期。(7)数据选通进程,由地址来控制,负责将各路数据送到缓冲器中。各个进程之间利用信号来传递,互相协调工作,是一个完整的统一体,由写信号作为预留,在需要时可以进行扩展和添加。

3.1.3 fifo_t模块

此模块是一个深度为3个字节的同步FIFO(先入先出堆栈),用来将地址、高字节数据、低字节数据寄存。

由于此模块为一个同步FIFO,而本设计中的读写是分开的,读写的速度也不相同,写的时候要求高速写入,不影响通信的连贯性,读的时候根据发送模块的速度来读取数据,所以读、写时钟用两个模块中的状态机产生,为了不产生冲突,两个模块在空闲状态将时钟送出低电平,然后将两个始终用一个或门连接,送入FIFO中进行控制。

3.1.4 Tx_HDLC模块

该模块主要负责以下几个功能:

(1)FIFO的读操作。将FIFO中的地址、高位字节数据、低位字节数据读出来。(2)HDLC协议的控制。包括产生帧头、帧尾数据(7E)附到数据流上,产生CRC校验多项式,将多项式的结果附到数据的尾部。(3)发送数据控制。利用状态机控制发送程序,将处理好的一帧数据发送到嵌入式计算机上。

模块特点:

(1)流水线作业,将FIFO中的数据读出来后进行并-串转换,将串行数据用流水线进行CRC运算,然后再进行串-并转换将数据发送出去。(2)利用程序计数器进行时序控制,控制流水线的操作。(3)利用状态机控制发送程序,并且控制和数据传送分开,保证数据传送有足够的建立时间和保持时间。(4)增加数据锁存语句,使得每次处理完的数据都能够稳定一段时间,增强数据的可靠性。

3.1.5 异步通信发送模块

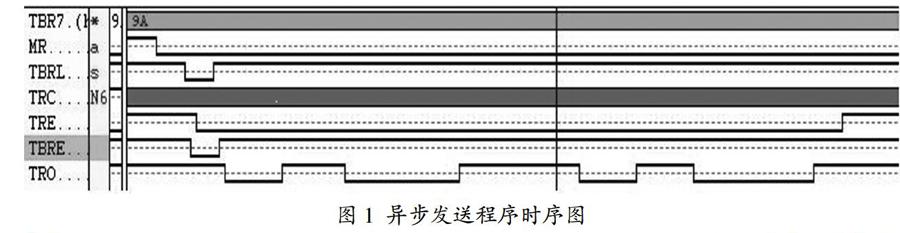

采用波特率为9600,数据为8位,偶校验方式发送数据,发送时序为:

(1)脚至为低电平,此时内部状态标志复位,将TRBL置为高电平。(2)将数据送入端口准备好,将TRBL信号置为低电平,此时TRE引脚边为低电平,装入数据,开始传送。(3)RBL置为高电平,等待数据发送完成后,输出引脚TRE变为高电平。

3.2 接收部分

接收部分实现的功能是将嵌入式计算机发送过来的步进电机预制位置、实际位置等数据送入相应的数据总线上。嵌入式计算机通过COM口发送数据,通信协按照HDLC协议,根据发送数据的格式规定,该部分主要由接收数据模块(UART_R),接收控制模块(UART_CTRL),先入先出堆栈(FIFO)模块,检错控制模块(MONITOR),数据控制模块(MCU),装载信号延时模块(LOAD_DELAY)。

接收过程将一帧数据中的有效数据按照规定送到相应的数据总线上。工作流程如下:

(1)UART_R负责接收上位及发送过来的数据,每次接受一个字节。(2)接收过程受UART_CTRL控制,由UART_CTRL内部的状态机形成的时序来控制UART_R模块,然后将接收到的1帧数据写入FIFO。(3)MCU模块负责协调整个系统的工作,包括所有模块的初始化,数据控制,当检测到FIFO中的数据被写满,则将一帧数据从FIFO高速读出,高速读出是为了不影响数据的接收,然后按照地址将数据分配到相应的总线上。(4)数据接收需要差错控制,帧数据不完整和不同步都视为错误数据,由内部逻辑和MONITOR产生控制信号。

3.2.1 接收数据模块(UART_R)

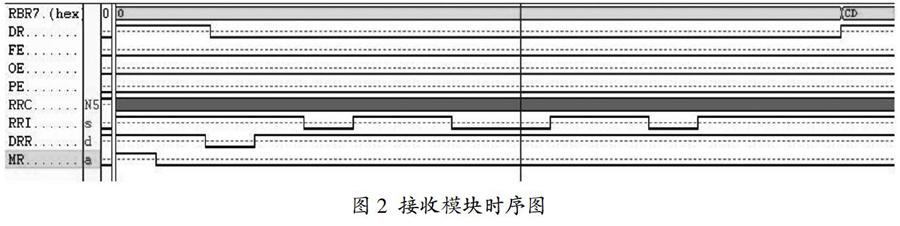

MR为高电平时,将模块内部寄存器复位;MR为低电平时,启动整个模块,此时应将DRR置成低电平,将输出引脚DR置为低电平,然后再将DRR置为高电平,开始接收数据。接收数据按照9600的波特率,数据接收完毕后DR送出高电平,RBR[7..0]输出接收到的数据。时序图如图2所示。

3.2.2 接收控制模块(UART_CTRL)

接收控制模块负责启动接收模块接收嵌入式计算机发送过来的数据,并将数据写入FIFO堆栈中。该模块受MCU模块控制,并和器协调工作,主要操作即是对FIFO的读写。该模块没有任何的总线传输,只是靠状态机控制一些输入输出信号控制接收模块和先入先出堆栈之间的数据通信。

3.2.3 检错控制模块(MONITOR)

在接收模块工作期间,MCU读FIFO是采用16M时钟控制,高速读取是为了不影响数据的接收,每来一帧数据,MCU模块会迅速将FIFO中的数据读空,使得FIFO的外部信号EMPTY,迅速处于高电平,也就是说,在接收到完整的一帧数据的情况下,EMPTY信号会形成一个短暂的高电平,当通信出现问题,上位机还为发送完一帧数据就停止数据的发送,这时UARTR_CTRL将会继续等待数据的到来,FIFO输出的EMPTY信号也一直维持低电平,造成通信恶化,解决办法即是加入了此模块进行控制。

此模块相当于一个看门狗定时器,外部信号只有3个,EMPTY,CLK为输入信号。CLK为计数时钟,引自波特率时钟分频器,EMPTY每来一个高脉冲(喂狗)将内部计数器清零,视为数据正确,ERROR送出低电平,当EMPTY长时间处于低电平,计数器计到2000后将ERROR自成一个高电平,将系统复位,再回到低电平。

3.2.4 数据控制模块(MCU)

数据控制模块负责将FIFO中的一帧数据读出来,然后按照数据格式中规定的数据格式,将数据送入相应的数据总线上。该模块主要特点:

(1)数据的高速读取,采用16MHz时钟控制,不影响通信的速度。(2)数据的锁存,由内部状态机产生控制信号,使得接收到的数据稳定的锁存到数据总线上。(3)差错控制,配有简单的差错控制,当帧数据不同步将总模块重新复位,不会将错误的数据送到总线上。(4)状态机控制时序清晰,每一部数据的传输都有足够的建立/保持时间。

4 异步通信模块设计综述

该异步通信模块实现了预期的设计功能,数据传送较为可靠,但由于起初对设计需求分析不够,系统中很多高级功能未被采用,例如HDLC协议中的插零,CRC校验位没有被采用,接收部分也没有对接收到的CRC校验位作处理,但是对于短波发射机自动调谐系统来说,由于通信数据量不大该设计已经够用,该通信模块已经使用8年,没有出现任何问题,说明该设计是成功的,确保了我局安全传输发射工作。

参考文献

[1]黄晓兵.TBH522型150KW短波发射机维护手册[M].中国书籍出版社.

[2]汤永福.TBH522型150KW短波发射机自动调谐控制系统[Z].内部使用.

作者简介:林大桥(1973-),男,汉族,福建龙岩人,国家新闻出版广电总局七三一台,工程硕士,本科,高级工程师。