GaN基垂直结构LED的n型电极结构设计及芯片制备

刘 丽, 胡晓龙, 王 洪

(华南理工大学 广东省光电工程技术研究中心, 物理与光电学院, 广东 广州 510640)

GaN基垂直结构LED的n型电极结构设计及芯片制备

刘 丽, 胡晓龙, 王 洪*

(华南理工大学 广东省光电工程技术研究中心, 物理与光电学院, 广东 广州 510640)

首先利用电流路径模型分析n型电极尺寸及间距等对垂直结构发光二极管(VS-LEDs)电流分布均匀性的影响,依此设计出一种螺旋状环形结构电极。其次,通过建立有限元分析软件Comsol仿真模型模拟VS-LEDs有源层的电流密度分布,发现螺旋状环形结构电极的环间距越小,电流密度分布越均匀。最后,利用VS-LEDs芯片制备技术实现具有螺旋状环形电极的垂直结构LED芯片。实验结果显示,在350 mA电流驱动下,电极环间距为146.25 μm的芯片具有最大的功能转换效率,达到26.8%。

氮化镓; 垂直结构发光二极管; 电流分布; 螺旋状环形结构电极

1 引 言

氮化镓(GaN)基发光二极管(LED)自问世以来,得到了飞速的发展,广泛应用于交通信号、建筑装饰、全彩显示、背光源、汽车前照灯以及室内外照明等领域[1-2]。传统结构GaN基LED芯片通常是指在蓝宝石衬底上制备的n型和p型电极分布于同侧的一种芯片[3]。由于蓝宝石衬底的电绝缘特性,电流在p-GaN和n-GaN间发生横向流通,LEDs在大电流注入下将发生电流拥挤效应,影响LED芯片的发光效率[4-5]。而垂直结构发光二极管(Vertical structure light emitting diodes,VS-LEDs)则利用键合(或电镀)和激光剥离技术将外延层从蓝宝石衬底上转移到导电及散热性能良好的衬底上,电极分布在有源区两侧,使得电流扩展更加均匀,从而有效缓解电流拥挤问题,是非常适合用于制备大功率LED的一种芯片结构[6-8]。然而,大功率VS-LEDs的尺寸较大,并且一般需要在较大电流注入下工作,因而仍然存在电流分布不均的问题,如电流在n电极底部集聚,这将使电极部位结温升高,严重影响着芯片的发光效率及使用寿命等[9]。n型电极形状及尺寸与上述问题有直接关联,因此,可以通过优化芯片n型电极结构来改善器件中电流分布均匀性,提高芯片发光效率,并且相对于增加透明导电电流扩展层[10]、电流阻挡层[11]等提高LED芯片光效的方法而言,因其具有操作简单、实施容易以及生产成本相同下性能更高的特点,对n型电极结构优化来实现对器件效率的提高是一个重要的研究方向。目前已经有一些与GaN基VS-LEDs芯片的n型电极结构优化的研究报道。Tu等[12]结合三维数字模拟与实验,分析了不同间距和分支数的目字形电极结构对VS-LEDs电学和光学特性的影响。Kim等[13]研究了不同覆盖面积的方块形电极对VS-LEDs光电性能的影响,明确了在n电极设计中,垂直电流最小化、扩展电流最大化的方向。Chu等以传统圆形电极为基础,依次加上十字、单框、环框,形成4种n电极结构,采用相同工艺制成VS-LEDs芯片并对比其发光特性,发现在大电流注入下,4种n电极结构依次显现出更优的光学特性[14]。

本文提出一种螺旋状环形结构电极用于制备GaN基VS-LEDs芯片,通过建立有限元分析软件Comsol仿真模型,对具有不同环间距的螺旋状环形结构电极的VS-LEDs的有源层电流密度分布进行模拟,得出螺旋状环形电极的环间距与电流均匀性的关系。进一步地,利用高反射率p型欧姆接触电极、电镀金属铜基板、激光剥离及表面粗化等技术制备出具有表面螺旋状环形电极的垂直结构LED芯片。结合电流密度分布及LED性能测试结果得出螺旋状环形电极结构对VS-LEDs芯片的性能影响,发现当螺旋状环形电极的环间距在92.5~146.25 μm的范围内时,垂直结构LED芯片具有较低的工作电压、较高的光输出功率和功能转换效率。

2 理论分析与仿真模型

图1所示为VS-LEDs在二维平面内的电流路径图。从图中可知,电流传播路径主要有两类:一类是在p与n电极间的垂直传播路径,如图1中标记1所示;另一类是横向传播的路径,如图1中标记2所示。明显地,电流在从p电极流向n电极的过程中,路径2需要比路径1克服更多的电阻。而电流更倾向于选择电阻小的路径,这种电流对电阻更小路径的自发选择,导致电流极易在n电极下方集聚[15]。

图1 VS-LEDs二维电流路径示意图

电流分别流过路径1、2产生的压降由如下公式给出:

V1=J(ρp-contact+ρptp+ρntn+ρn-contact)+Va,

(1)

V2=J(ρp-contact+ρptp+pntn+ρnl+ρn-contact)+Va,

(2)

其中,J是电流密度,ρp-contact和ρn-contact分别为p型和n型欧姆接触电阻率,ρp和ρn分别为p-GaN和n-GaN的电阻率,tp和tn分别为p-GaN和n-GaN的厚度,l为电流在n-GaN中的横向扩展距离,Va为有源层的驱动电压。

为使电流均匀传播,应满足下面的等式:

V1=V2,

(3)

可得Jpnl=0.

(4)

实现上述等式有三种方法:一是J尽可能小,但要实现大功率VS-LEDs芯片,一般需要在大电流密度下工作;二是ρn尽可能小,提高n-GaN的掺杂浓度可以降低其电阻率,但同时会加重光子吸收,降低光效;三是l尽可能小,大功率VS-LEDs芯片的尺寸一般较大,因而电极结构的合理设计就成为缓解电流在n电极底下聚集的一个重要突破点。

本研究中,电流密度仿真采用多物理场耦合仿真软件Comsol Multiphysics,在稳恒电流场下建立三维有限元电学分析模型,将芯片结构做以下等效[16]:

(1)多量子阱(Multiple quantum wells,MQWs)有源层等效为一个二极管,电学特性用肖克利方程描述:

(5)

其电流密度符合连续性方程:

(6)

在大电流注入下,二极管的I-V特性呈线性,其关系可简化为

Vi=ρadaJ(r)+Vb,

(7)

其中,ρa、da、Vb分别为有源层的电阻率、厚度和电阻接触造成的正向匹配常数。

(2)其他材料层忽略内部载流子复合,电学特性符合欧姆定律:

J(r)=-σ·φ,

(8)

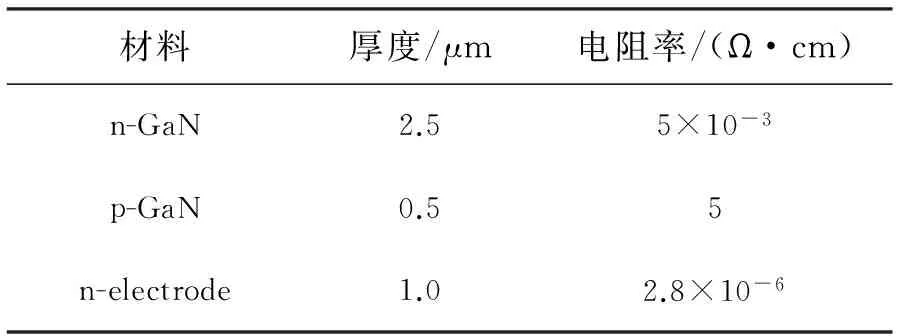

仿真采用的注入电流为350mA,芯片结构参数如表1所示。

一般情况下,在p-GaN表面作为反射层的Ag镜厚度不超过0.15μm,而Ag金属的电阻率低至1.5×10-6Ω·cm,并且Ag镜是整面覆盖在p-GaN表面,故Ag反射层对VS-LEDs的电流密度均匀性影响较小。另外,VS-LEDs一般工作在大电流下,如前所述,此时MQWs层的I-V特性呈近线性,与其他材料层电性相似。由于MQWs厚度极薄,且根据前面对VS-LEDs电流路径的分析,造成电流拥挤现象的原因主要是在n-GaN层存在电流的横向扩展,故MQWs对VS-LEDs的电流密度均匀性影响也较小。为了降低Comsol对VS-LEDs芯片模型的几何分割和有限元分析难度,本模拟中省略Ag镜层和MQWs层。

表1 Comsol电学模型中所用到的各层的厚度及电阻率参数

Tab.1 Thickness and electrical resistivity of the used layer for Comsol electrical model

材料厚度/μm电阻率/(Ω·cm)n-GaN2.55×10-3p-GaN0.55n-electrode1.02.8×10-6

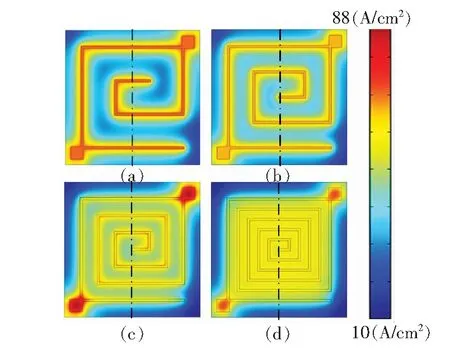

在芯片尺寸及各层导电率、厚度等参数确定的情况下,VS-LEDs的电流密度分布主要取决于电极结构和尺寸。本文设计了4种不同环间距的螺旋状环形结构电极的VS-LEDs模型,如图2所示。芯片尺寸大小设计为860 μm×860 μm,n型电极焊点尺寸统一设置为80 μm×80 μm,焊点距芯片边缘的距离为35 μm,n型电极线条宽为15 μm,结构a、b、c、d的电极线条长度如表2所示,4种螺旋状环形结构电极的环间距分别为200.0,146.25,92.5,49.5 μm。

图2 4种不同环间距螺旋状环形结构电极的俯视图

Fig.2 Top view of the annulospiral electrodes with different ring spacings

表2 4种不同环间距的电极长度

注:参数n从小到大取值对应电极由外而内分布,相应于n取值1的组成电极条数为3,其余为2。

3 芯片制备实验

本实验采用金属有机化学气相沉积(Metal organic chemical vapor deposition,MOCVD)系统进行外延生长。首先在c面(0001)图形化蓝宝石衬底上低温生长一层厚度为20 nm的成核层,然后在高温下生长一层厚度为3.5 μm的非掺杂u-GaN层和4 μm的Si掺杂n-GaN,接着生长InGaN/GaN多量子阱层有源层,最后生长Mg掺杂p-AlGaN电子阻挡层和p-GaN层。

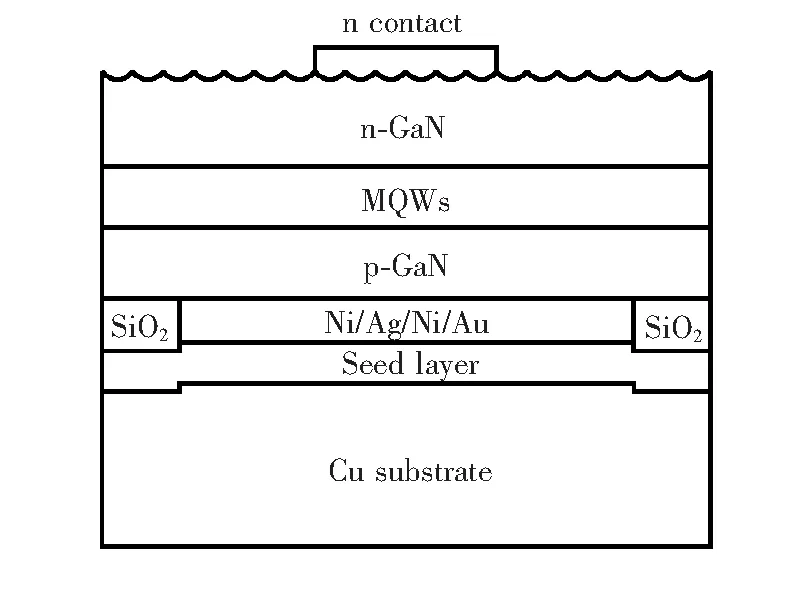

具有不同环间距的螺旋状环形结构电极VS-LED芯片的制备工艺如下:首先采用电感耦合等离子体(Inductively coupled plasma,ICP)刻蚀技术刻蚀出900 μm×900 μm的台面,分开各芯粒单元;再利用等离子体增强化学气相沉积(Plasma enhanced chemical vapor deposition,PECVD)生长1 μm厚的SiO2作为侧壁保护层;然后,利用电子束蒸镀技术生长Ni/Ag/Ni/Au(0.5/150/200/200 nm)作为反射电极,该反射镜退火后的反射率达到92.3%[17],反射电极大小为860 μm×860 μm;接着蒸镀Cr/Pt/Au作为电镀种子层,在种子层上电镀一层厚度为120 μm的Cu作为金属基板;然后通过激光剥离(Laser lift-off,LLO)技术移除蓝宝石衬底;通过ICP刻蚀激光剥离后的u-GaN表面至n-GaN,接着在95 ℃水浴条件下在浓度为2mol/L的KOH溶液中浸泡6 min做表面粗化;最后在n-GaN表面电子束蒸镀Cr/Al/Ti/Au(2/400/100/500 nm),形成螺旋状环形结构电极。制成的VS-LEDs芯片的截面结构如图3所示。

图3 VS-LEDs芯片的截面示意图

4 结果与讨论

图4所示为利用Comsol软件计算的VS-LEDs有源层电流密度分布图,通过VS-LEDs有源层的电流密度分布可知VS-LEDs电流扩展情况。判断电流分布均匀性一般可以采用电流密度的最大、最小值的比值,而本文将计算整个范围的电流密度分布,这样更能准确分析芯片各个位置电流密度的扩展情况[18]。从图4中可以看出,随着n型电极环间距的减小,电流在n电极下方的聚集逐渐减弱。这是因为在n-GaN上电流横向传播所需的路径长度l在减小。对于n型电极间距较大的芯片,由于电流横向路径长度l较大,其电流不能从n电极下方扩展开,易导致芯片局部过热,影响光萃取效率。图5所示为在350 mA电流注入下的4种芯片模型在x=430 μm截线处的电流密度分布情况。可以清楚地看出,环间距越小的VS-LEDs芯片的电流分布越均匀。这是因为电流横向扩展所需距离l越短,电流流经n电极下方以外的路径时要克服的电阻与p、n电极间垂直传播所要克服的电阻越接近。

图4 具有不同环间距的螺旋环状结构电极的VS-LEDs芯片有源层中的电流密度分布

Fig.4 Current density distribution of VS-LEDs with different annulospiral electrodes

图5 电流密度沿图4中参考线(x=430 μm)的变化

Fig.5 Change of current density along the reference line (x=430 μm) in Fig.4

我们利用高反射率p型欧姆接触电极制备、电镀金属铜基板、激光剥离和n型高反射率电极制备等技术实现具有不同环间距的螺旋状环形结构电极的垂直结构LED芯片。环形电极尺寸和结构与仿真模拟中采用的相一致。我们将环间距为200,146.25,92.5,49.5 μm的芯片分别命名为样品A、B、C、D。图6所示为样品 A、B、C、D在0.1 mA电流注入下的发光图。从图中可以看出,在小电流下,4种LED芯片的光强分布都较为均匀。样品A、B、C、D在350 mA下的相对发光强度分布如图7所示。从图中可以看出,发光强度分布的均匀性与仿真中电流分布均匀性相一致。随着环间距的减小,VS-LEDs芯片的发光强度分布更加均匀。然而我们也发现,环间距最小的样品D的光强却有所降低。

图6 0.1 mA电流注入下的样品A、B、C、D的芯片发光图。

Fig.6 Lighting images of sample A, B, C, and D at an injection current of 0.1 mA.

图7 350 mA电流注入下样品A、B、C、D的相对发光强度分布。

Fig.7 Relative intensity distribution of sample A, B, C, and D at an injection current of 350 mA.

样品A、B、C、D的I-P特性曲线如图8所示。从图中可以看出,在注入电流为350 mA时,样品A、B、C、D的光输出功率分别为368.4,359.8,346.0,302.6 W。随着环间距的减小,样品的光输出功率逐渐降低,样品D的光输出功率比样品C低12.5%,比样品A低17.8%。出现这些现象的原因是:随着环间距的减小,电极对VS-LEDs的遮光面积增加。对于样品A、B、C,电流分布均匀性依次增强,而电极遮光面积依次增大。电流分布均匀性增强使VS-LEDs光效增加,而增大了电极遮光面积又会使VS-LEDs光效减小,因此需要综合考虑两者对样品光输出功率的影响。样品D的电流分布最均匀,然而由于环间距降幅较大,电极面积的大幅增加严重降低了芯片的输出功率,其光输出功率远小于电流分布不及其均匀的样品A、B、C。这表明虽然减小环间距有利于电流的均匀扩展,但还需要考虑电极面积对VS-LEDs芯片的出光功率的影响。

图8 样品A、B、C、D的I-P特性曲线。

Fig.8 Light output power-injection current characteristics of sample A, B, C, and D, respectively.

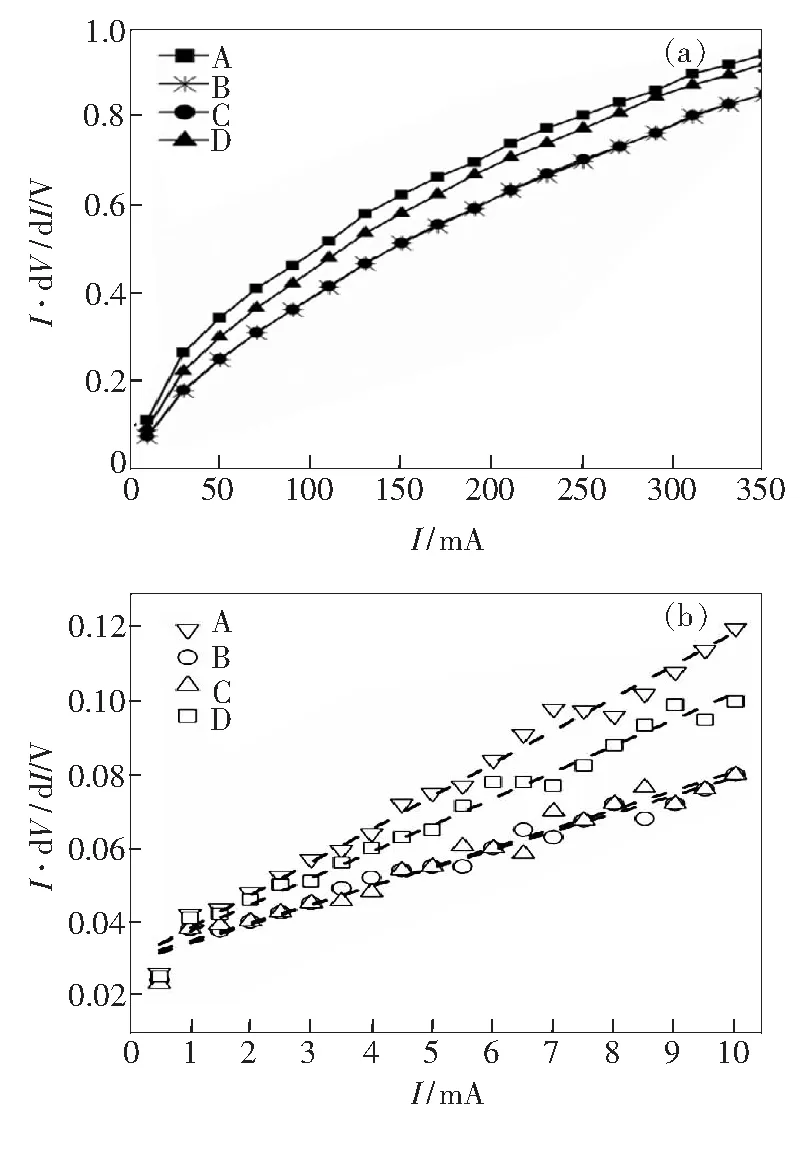

图9所示为样品A、B、C、D的I-V特性曲线。在注入电流为350 mA时,它们的工作电压分别为4.76,3.83,3.84,4.38 V。样品的电压总体偏高的原因,一是我们采用了高反射率的n型电极Cr/Al/Ti/Au(2/400/100/500 nm),与N极性n-GaN接触的金属Cr层厚度极薄;二是PSS衬底去除后,n型电极需要与具有表面微结构的n-GaN进行接触,目前所采用的n型接触条件还有待进一步的研究与优化。通过对比发现,样品A的工作电压最高,样品B和C的工作电压相近且最低,样品C的电压比样品A的电压低0.92 V,比样品D的电压低0.54 V。这些电学特性与其串联电阻有关,串联电阻与电流、电压间的关系[19]可表示为

(9)

其中,Rs是串联电阻,n是理想因子。故把I-V特性曲线转化为(I·dV/dI)-I的关系曲线,如图10(a)所示,图10(b)为其中0~10 mA的部分曲线,曲线的斜率即表示器件的串联电阻。通过对图10(b)中的曲线进行线性拟合,可得样品A、B、C、D的串联电阻分别为8.97,4.96,5.22,7.23 Ω。可以看出,随着电极环间距的减小,串联电阻先减小后增大。样品A的串联电阻较大的原因是电极的环间距较大,使得电流分布不均匀。而随着环间距的减小,串联电阻先减小的原因主要是随着环间距的减小,电流密度分布更加均匀,从而降低了串联电阻;串联电阻后增大的主要原因则是随着环间距变小,电极总长度增加(表2中样品D的电极总长度分别是样品A、B、C电极总长度的2.4、2.0、1.5倍),而电极的横截面积较小(电极的宽度为15 μm,电极的厚度约为1 μm),因此电极的电阻随着电极总长度的增加不可忽略。若把电极按金属铝的电阻率2.83×10-6Ω·cm计算电极电阻,则样品A、B、C、D的电极的横向电阻分别为6.28,7.56,10.1,15.2 Ω,因此,串联电阻后增大的原因是随着电极的环间距的减小,螺旋状环形电极本身电阻增大。电极横向电阻的增大也会使得LED芯片的电流密度分布更不均匀。这也是电极环间距变小后,LED芯片功率快速下降的另一原因。

图9 样品A、B、C、D的I-V特性曲线。

Fig.9 Injection current-forward voltage characteristics of sample A, B, C, and D, respectively.

图10 样品A、B、C、D的(I·dV/dI)-I特性曲线。

Fig.10 (I·dV/dI)-Icharacteristics of sample A, B, C, and D, respectively. The imaginary lines in (b) are the linear fitting curves whose slope gives the series resistance.

LED芯片的功能转换效率(Wall plug efficiency,WPE)由下式决定:

(10)

图11所示为样品A、B、C、D的WPE随注入电流的变化曲线。在注入电流为350 mA时,样品A、B、C、D的功能转化效率分别为25.2%、26.8%、25.7%、21.4%。样品A、B、C的WPE分别是样品D的1.18、1.25和1.20倍。上述结果表明,n型电极结构是影响VS-LEDs各项性能重要的参数,通过优化电极结构可以实现高性能的大功率LED芯片。

图11 样品A、B、C、D的功能转换效率。

Fig.11 Wall-plug efficiency of samples A, B, C, and D, respectively.

5 结 论

首先模拟了4种环间距分别为200,146.25,92.5,49.5μm的螺旋状环形电极结构VS-LEDs芯片的有源层电流密度分布,发现随着环间距的减小,芯片的电流密度分布均匀性变好。进一步地,利用高反射率p型欧姆接触电极制备、电镀金属铜基板、激光剥离及n型高反射率电极制备等技术制作了具有不同环间距的螺旋状环形电极结构的VS-LEDs芯片。实验结果显示,随着环间距的减小,由于电极的遮光面积变大,使得芯片输出功率逐渐降低,环间距最小的样品的输出功率比环间距最大的样品低17.8%@350 mA。而随着环间距的减小,芯片的电压先减小后增大。通过分析它们的串联电阻的变化发现n型电极总长度对器件的电压的影响较大。最后,通过计算LED样品的功能转换效率发现,环间距为146.25 μm的样品的功能转换效率最高为26.8%,是环间距为49.5 μm的样品的1.25倍。这些结果表明,LED芯片的电极结构设计非常重要,需要综合考虑芯片的电流分布均匀性、器件出光功率及芯片的串联电阻等,以实现芯片功能转换效率的最大化。

[1] LI C K, WU Y R. Study on the current spreading effect and light extraction enhancement of vertical GaN/InGaN LEDs [J].IEEETrans.ElectronDevices, 2012, 59(2):400-407.

[2] CHANG L M, CHANG S J, JIAO Z Y,etal.. Enhanced current spreading for GaN-based side-view LEDs by adding an metallic stripe across the long side of the chip [J].IEEEPhoton.Technol.Lett., 2012, 24(16):1412-1414.

[3] HORNG R H, CHUANG S H, TIEN C H,etal.. High performance GaN-based flip-chip LEDs with different electrode patterns [J].Opt.Express, 2014, 22(S3):A941-A946.

[4] 潘华璞,黄利伟,李睿,等. GaN基LED电流扩展的有限元模型及电极结构优化 [J]. 发光学报, 2007, 28(1):114-120. PAN H P, HUANG L W, LI R,etal.. Finite element model of GaN-based LED and the optimization of the mesa structure [J].Chin.J.Lumin., 2007, 28(1):114-120. (in Chinese)

[5] LIU H H, CHEN P R, LEE G Y,etal.. Efficiency enhancement of InGaN LEDs with an n-type AlGaN/GaN/InGaN current spreading layer [J].IEEEElectr.DeviceLett., 2011, 32(10):1409-1411.

[6] LIU W J, HU X L, ZHANG J Y,etal.. Low-temperature bonding technique for fabrication of high-power GaN-based blue vertical light-emitting diodes [J].Opt.Mater., 2012, 34(8):1327-1329.

[7] TSAI Y J, LIN R C, HU H L,etal.. Novel electrode design for integrated thin-film GaN LED package with efficiency improvement [J].IEEEPhoton.Technol.Lett., 2013, 25(6):609-611.

[8] TIAN T, WANG L C, GUO E Q,etal.. Optimized subsequent-annealing-free Ni/Ag based metallization contact to p-type GaN for vertical light emitting diodes with high yield and extremely low operating voltage (2.75 V@350 mA,>95%) [J].J.Phys. D, 2014, 47(11):115102.

[9] LI C K, WU Y R. Current spreading effect in vertical GaN/InGaN LEDs [J].SPIE, 2011, 7939:79392K.

[10] WANG S J, CHEN S L, UANG K M,etal.. The use of transparent conducting indium-zinc oxide film as a current spreading layer for vertical-structured high-power GaN-based light-emitting diodes [J].IEEEPhoton.Technol.Lett., 2006, 18(10):1146-1148.

[11] CHEN T M, WANG S J, UANG K M,etal.. Current spreading and blocking designs for improving light output power from the vertical-structured GaN-based light-emitting diodes [J].IEEEPhoton.Technol.Lett., 2008, 20(9):703-705.

[12] TU S H, CHEN J C, HWU F S,etal.. Characteristics of current distribution by designed electrode patterns for high power Thin GaN LED [J].Solid-StateElectron., 2010, 54(11):1438-1443.

[13] KIM H, KIM K K, CHOI K K,etal.. Design of high-efficiency GaN-based light emitting diodes with vertical injection geometry [J].Appl.Phys.Lett., 2007, 91(2):023510-1-3.

[14] CHU J T, KAO C C, HUANG H W,etal.. Effects of different n-electrode patterns on optical characteristics of large-area p-side-down InGaN light-emitting diodes fabricated by laser lift-off [J].Jpn.J.Appl.Phys., 2005, 44(11):7910-7912.

[15] KIM D W, LEE H Y, YEOM G Y,etal.. A study of transparent contact to vertical GaN-based light-emitting diodes [J].J.Appl.Phys., 2005, 98(5):053102-1-4.

[16] 钟广明,杜晓晴,唐杰灵,等. 影响倒装焊LED芯片电流分布均匀性的因素分析 [J]. 物理学报, 2012, 61(12):127803-1-9. ZHONG G M, DU X Q, TANG J L,etal.. Analysis of influencing factors on current spreading of flip-chip light-emitting diodes (LEDs) [J].ActaPhys.Sinica, 2012, 61(12):127803-1-9. (in Chinese)

[17] HU X L, LIU L, WANG H,etal.. Effects of pre-annealed ITO film on the electrical characteristics of high-reflectance Ni/Ag/Ni/Au contacts to p-type GaN [J].Appl.Surf.Sci., 2015, 357:1703-1707.

[18] KUMAR S, SINGH S, LUNIA A K,etal.. Optimization of n-electrode pattern for p-side down vertical InGaN/GaN blue light emitting diodes [J].Phys.Stat.Sol., 2014, 211(9):2134-2141.

[19] LUO Z S, CHO Y, LORYUENYONG V,etal.. Enhancement of (In, Ga) N light-emitting diode performance by laser liftoff and transfer from sapphire to silicon [J].IEEEPhoton.Technol.Lett., 2002, 14(10):1400-1402.

n-type Electrode Patterns Design and Device Fabrication of GaN-based Vertical Structure LEDs

LIU Li, HU Xiao-long, WANG Hong*

(EngineeringResearchCenterforOptoelectronicsofGuangdongProvince,SchoolofPhysicsandOptoelectronics,SouthChinaUniversityofTechnology,Guangzhou510640,China)

*CorrespondingAuthor,E-mail:phhwang@scut.edu.cn

The influences of size and spacing of n-type electrode on the current distribution of vertical-structure light-emitting diodes (VS-LEDs) were firstly analyzed by two-dimension circuit modeling, and annulospiral n-type electrodes were proposed for the fabrication of VS-LEDs. Then, finite element analysis model in Comsol Multiphysics was built to study the current density distribution in the active layer of VS-LEDs with the annulospiral electrodes. It is found that the current density distribution became more uniform when the electrode spacing reduced. Finally, VS-LEDs with various annulospiral electrodes were fabricated using high-reflectivity p-type Ohmic electrode, copper substrate electroplating and laser lift-off techniques. The wall plug efficiency of VS-LEDs with the electrode spacing of 146.25 μm is 26.8% at 350 mA, which is higher than that of VS-LEDs with other electrode spacings.

GaN; vertical-structure light-emitting diodes(VS-LEDs); current distribution; annulospiral electrode

刘丽(1990-),女,广东兴宁人,硕士研究生,2013年于华南理工大学获得学士学位,主要从事氮化镓基光电子器件方面的研究。

E-mail: 1916321996@qq.com

王洪(1964-),男,江苏无锡人,博士,教授,2004年于华南理工大学获得博士学位,主要从事微纳光电子材料与器件、光通信网络等领域的研究。

E-mail: phhwang@scut.edu.cn

1000-7032(2016)03-0338-08

2015-11-16;

2015-12-15

国家高技术研究发展计划(863 计划) (2014AA032609); 国家自然科学基金(61404050); 广东省战略性新兴产业专项资金(2012A080302003); 中央高校基本科研业务费(2014ZM0036)资助项目

TN383+.1

A

10.3788/fgxb20163703.0338