FPGA配置SRAM设计技术

张艳飞,耿 杨

(无锡中微亿芯有限公司,江苏无锡214072)

FPGA配置SRAM设计技术

张艳飞,耿杨

(无锡中微亿芯有限公司,江苏无锡214072)

摘要:首先分析了配置SRAM在SRAM型FPGA中的作用,介绍了配置SRAM的单元结构及在设计中的要点。设计实现了一种基于65 nm工艺的SRAM结构,并针对读写能力、功耗、噪声给出相应的仿真结果。此电路结构具有低功耗、抗噪声能力强的优点,已被应用于FPGA设计中并流片成功。

关键词:现场可编程门阵列;配置SRAM;静态噪声容限;读稳定性

1 引言

现场可编程门阵列(FPGA,Field Programmable Gate Array)是一种半定制集成电路,在其内部集成了大量的门和触发器等基本逻辑电路,用户通过编程来改变其内部的逻辑关系或连线,就可以得到需要的设计电路。FPGA按照编程方式可分为SRAM型、ANTI-FLASH型、FLASH型等,SRAM型是迄今为止应用范围最广的架构,具有密度高、速度快且具有可重复编程能力。配置SRAM作用是用户编程后存储配置的代码,同时对于采用SRAM工艺的可编程逻辑器件而言,要求每次上电对可编程逻辑器件进行重配置[1],因此SRAM的设计是FPGA芯片能否正常实现配置及功能的关键。

2配置SRAM工作原理

结构上,FPGA包含了各种可编程资源,包括可编程逻辑块(CLB)、布线资源以及可编程输入输出模块(IOB)等[2]。配置SRAM在FPGA内部有广泛的分布,它们以列的形式穿插在逻辑模块及布线资源的中间,被写入“0”或“1”后,可以实现对附近逻辑模块的控制。以布线开关阵列和CLB为例,配置SRAM的分布如图1所示。在FPGA内部配置SRAM的数量是巨大的,例如Xilinx公司Virtex4系列的XC4VLX100芯片内部配置SRAM数量可达到25 Mbit。

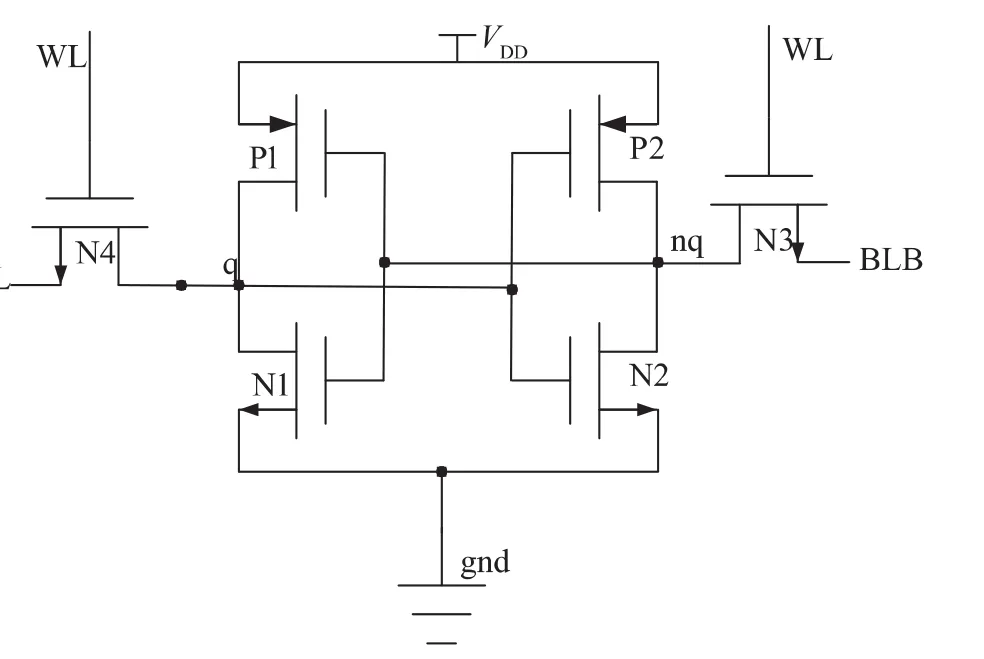

FPGA内部配置SRAM采用的是6管单元的结构,如图2所示。其中q和nq端引出,作为其他逻辑的控制端,BL、BLB为位线控制端,WL为字线控制端,这3个输入端口用于FPGA初始配置时配置信息的写入[3]。P1、P2、N1、N2是存储单元,而N3、N4用于门控访问。可以看出N1、P1和N2、P2是一个对称的结构,这是两个反相门的循环链接,由两个反相门循环相连的存储单元存在两种稳定状态,0或1。使用WL来控制存储单元的门控访问,BL来进行存储单元的读写。FPGA正常工作时SRAM读:WL为低,从q、nq中读出位即可;写:拉高WL,拉高或者拉低BL,由于BL的驱动能力比存储单元强,会强制覆盖原来的状态。

图1 配置SRAM在FPGA中的分布

图2 配置SRAM单元结构

3配置SRAM的设计与仿真

针对于FPGA配置SRAM的设计,主要关注静态功耗、写能力、读写稳定性和静态噪声容限SNM参数。

配置SRAM静态功耗测量,是在SRAM存储“0”或“1”后的静态功耗。

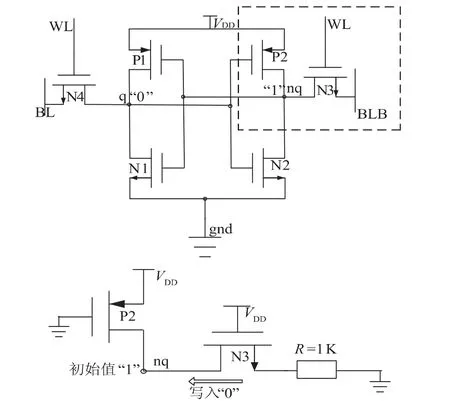

配置SRAM写能力与上拉管传输管的尺寸之比有关系,如图3虚线框中标注部分,上拉管P2与传输管N3的宽长比的比值将决定SRAM的写能力大小。

图3模拟的是节点nq由1写入0的过程(R代表金属位线的电阻),主要测量节点nq的电压值,一般写入完成后nq电压会小于N1管的阈值电压,如果写入完成后nq的电压值大于N1管的阈值电压则表明尺寸设计不合理,写入没有成功。写入完成后,节点nq的电压值越低,表明写入能力越好。

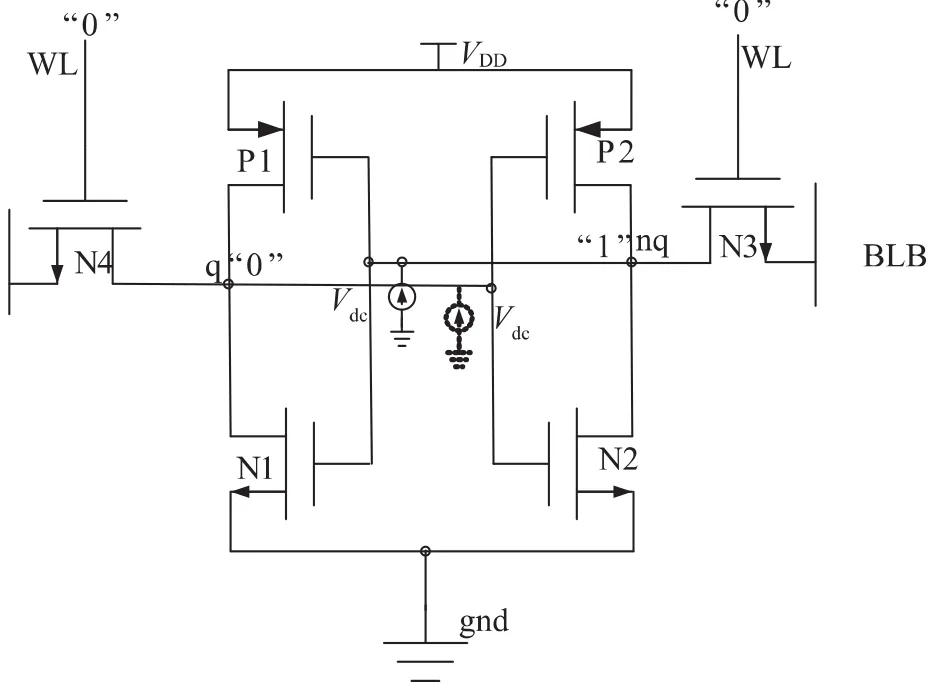

读写稳定性的测量方法如图4所示,其中WL为低电平,传输管关断,在节点q处加电流源从0~50 μA直流扫描,看电流加到何处时存储数据翻转。模拟读的过程,需要测量当电流源加到何处时节点q与nq翻转到相同的电压,并记录此时相对应的下拉管的电流Iread,Idc/Iread>1是能正常进行读操作的,Idc/Iread越大证明读稳定性越好。

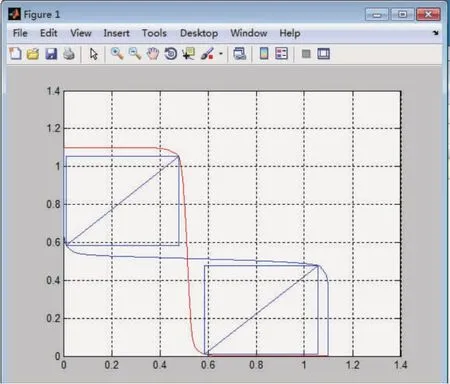

SNM是衡量存储单元抗干扰能力的一个重要参数。本文用电压传输曲线(VTC)也叫做蝴蝶曲线的测量方法测量SNM。测量方法如图5所示,分别对节点q和nq处电压参数进行直流扫描,对反相器输入端电压参数进行数据处理得到如图6所示的曲线,SRAM保持VTC曲线能够容纳的2个正方形中较小正方形的边长为SNM的值,SNM越大,表示保持性能越好。

图3 SRAM写能力测量方法

基于SMIC 65 nm CMOS工艺设计实现了FPGA配置SRAM结构,详细介绍了SRAM单元参数的模拟仿真方法,并给出了仿真结果。该设计符合FPGA配置SRAM的设计需求,被成功应用于FPGA的设计,经测试SRAM单元在0.7 V以上电压可进行读写操作;常温连续加电168 h,不间断进行读写,未出现数据错误现象。

图4 读写稳定性测量方法

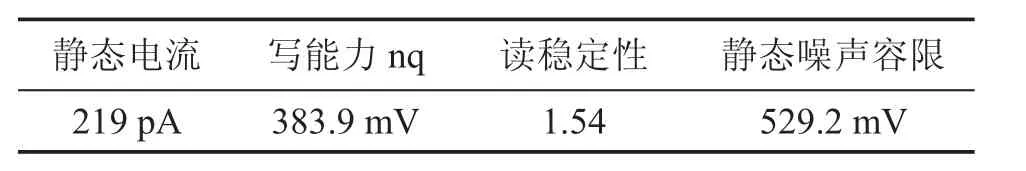

通过以上测试方法,设计一款65 nm工艺的SRAM单元,其在功耗、写能力、读稳定性、静态噪声容限方面的仿真结果如表1所示。

图5 SNM测试方法

图6 SNM测量结果

表1 65 nm工艺配置SRAM性能仿真结果

4 结论

参考文献:

[1]冯汝鹏,徐伟,朴永杰.基于SRAM型FPGA的容错性设计[J].电子测量技术,2014,10:76-80.

[2] Li Xingzheng,Yang Haigang,ZhongHua. Use of VPR in design of FPGA architecture[C]. 8th International Conference on Solid-state and Integrated Circuit Technology, 2006: 1880-1882.

[3]张惠国,唐玉兰,等. FPGA高性能查找表的设计与实现[J].固体电子学研究与进展,2009,4:584-588.

张艳飞(1981—),女,黑龙江佳木斯人,现就职于中国电子科技集团公司第58研究所,研究方向为FPGA芯片设计;

耿杨(1987—),女,河北石家庄人,现就职于无锡中微亿芯有限公司,研究方向为FPGA及SRAM单元设计。

FPGA Configuration SRAM Design Technology

ZHANG Yanfei, GEN Yang

(East Technologies, Inc,Wuxi 214072, China)

Abstract:The paper first analyzes the role of SRAM in the FPGA SRAM, introduces the structure of SRAM and the key points in the design, it designs a SRAM structure based on 65 nm process, and the corresponding simulation results are given for the reading and writing ability, power consumption and noise.This circuit structure which has been used in FPGA designand taped out successfullyhas the advantages oflow power consumption and strong anti-noise ability.

Keywords:FPGA; configuration SRAM; static noise margin; read stability

作者简介:

收稿日期:2015-11-20

中图分类号:TN402

文献标识码:A

文章编号:1681-1070(2016)03-0020-03