一种多通道缓冲串口的设计与实现

杨晓刚,强小燕,刘太广

(中国电子科技集团公司第58研究所,江苏无锡214035)

一种多通道缓冲串口的设计与实现

杨晓刚,强小燕,刘太广

(中国电子科技集团公司第58研究所,江苏无锡214035)

摘要:设计了一种多通道缓冲串口。在标准串口的功能基础上,增加了多通道控制逻辑来实现串口分时复用。并且加入数据压缩扩展逻辑,能够按照a律或者u律格式对数据进行压缩和扩展。逻辑综合结果表明,该通信串口具有良好的性能,可广泛应用于数字信号处理系统中。

关键词:多通道;串口;A律;u律

1 引言

随着DSP芯片得到越来越广泛的应用,对DSP通信接口的功能要求也越来越高。串行通信接口能有效减少器件引脚数[1],并且占用硬件资源少,得到广泛的关注和研究[2]。本文设计的多通道缓冲串口在标准串口基础功能上,增加了多通道传输功能和传输数据的压缩扩展功能。多通道数据传输功能,主要应用在一对多传输主串口根据寄存器的通道配置,将各个从串口所需的数据发送到相应通道上[3]。McBSP同时支持a律算法和u律算法的压缩扩展[4],能够按照a律或者u律格式对数据进行压缩和扩展。

2 McBSP发送和接收逻辑设计

2.1发送器

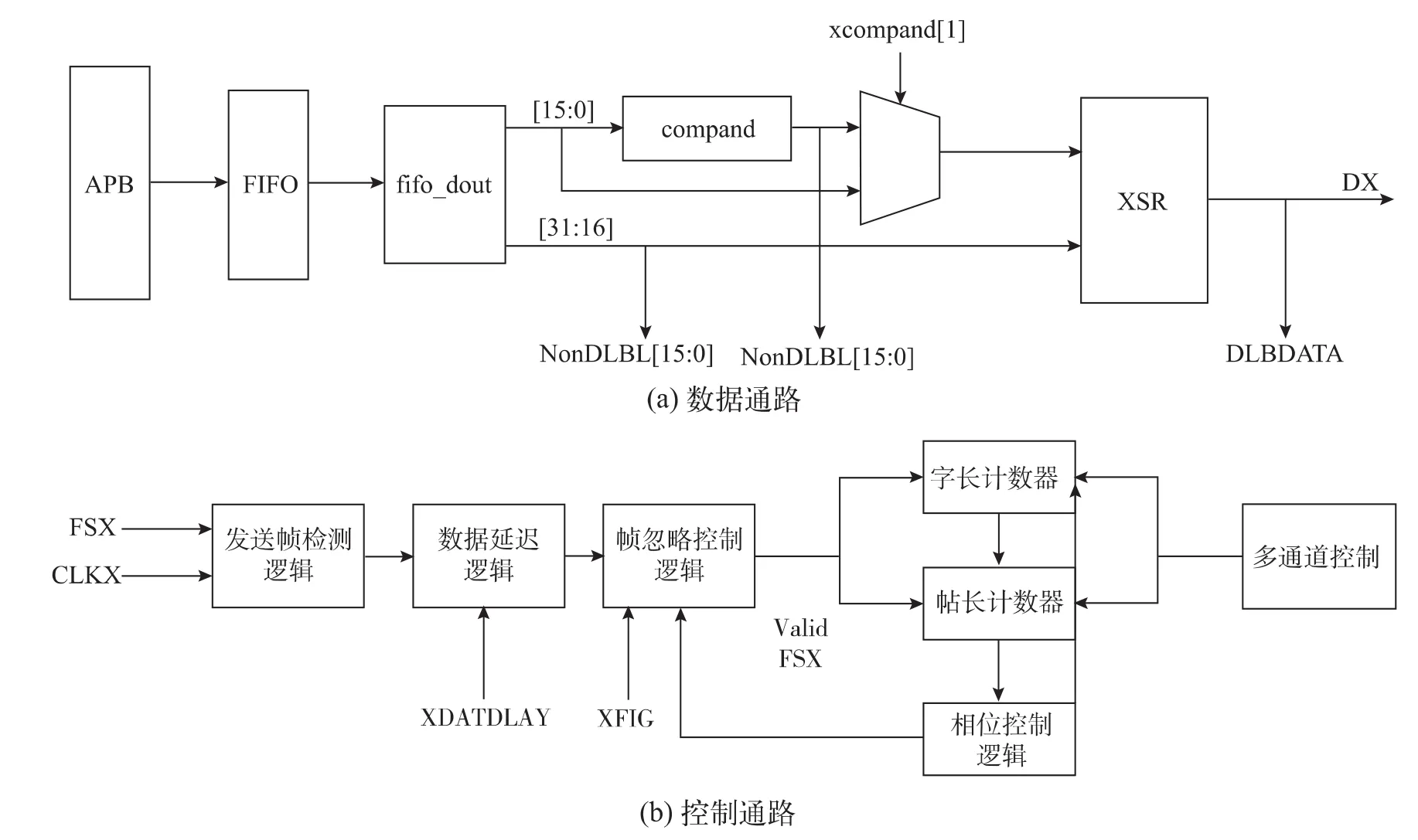

发送器模块完成数据从FIFO到DX引脚的串行发送,中间要经过压缩部件、发送移位寄存器等以及一些控制逻辑,如图1所示。FSX作为发送端的帧同步信号,作为一个数据字传输开始的标志。FSX经过帧检测逻辑、数据延时控制和帧忽略控制3个逻辑之后,产生一个有效的帧同步信号Valid FSX,并维持一个CLKX节拍。该信号可以启动字长度计数器和帧长度计数器,并将相位标志清零,开始一帧数据的发送。字长度计数器和帧长度计数器在Valid FSX有效时开始计数,当字长度计数器的值与配置的字长相等时,帧长度计数器加1。当帧长度计数器的值与配置的帧长相等时,数据发送完毕。

图1 发送器数据和控制通路

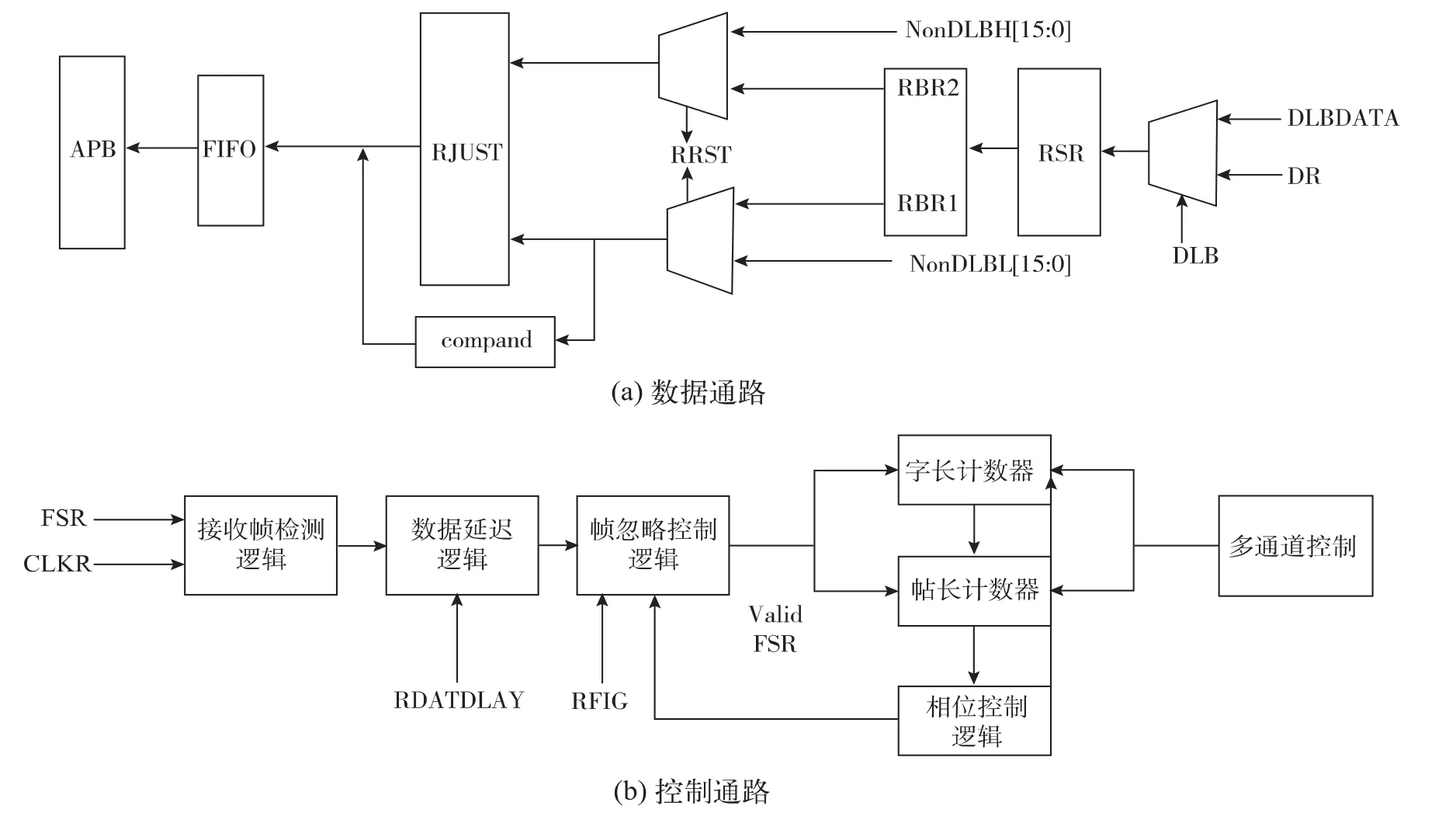

2.2接收器

接收器模块完成数据从DR引脚到DRR寄存器的串行接收,中间要经过接收移位寄存器RSR、接收控制逻辑、接收缓冲寄存器RBR、扩展部件、数据调整RJUST等逻辑最终到达数据接收寄存器FIFO。FSR作为接收端的帧同步信号,经过FSR检测逻辑、数据延时控制和FSR忽略控制3个逻辑之后,产生一个有效的帧同步信号Valid FSR,并维持一个CLKR节拍。该信号可以启动字长度计数器和帧长度计数器,并将相位标志清零,开始一帧数据的发送。字长度计数器和帧长度计数器在Valid FSX有效时,开始计数,当字长度计数器的值与配置的字长相等时,帧长度计数器加1。当帧长度计数器的值与配置的帧长相等时,数据接收完毕。

图2 接收器数据和控制通路

3 多通道控制逻辑设计

多通道操作是通过配置多通道控制寄存器MCR2中的XMCM字段来进行的,XMCM是一个2位的字段,当配置XMCM为一个非零值的时候,在串口的发送端启动之后就进行发送端的多通道操作。多通道操作共有3种模式:

模式一:XMCM=01,在这种模式下,发送端将禁止所有的通道,默认情况下通道全部屏蔽[5]。需要使用的通道通过使能XP(A/B)BLK和XCERA/B来选择。这些被选中的通道没有被屏蔽,因此DX引脚总是被驱动的。

模式二:XMCM=10,在这种模式下,发送端的所有通道均被启用,但被屏蔽[6]。由XP(A/B)BLK和XCERA/B来选择的通道未被屏蔽。

模式三:XMCM=11,该种模式用于对称的发送和接收操作中。在这种模式下禁止所有通道,因而默认为屏蔽。需要使用的通道可以通过使能XP(A/B)BLK 和XCERA/B来选择。选中的通道可以由RP(A/B)BLK和XCERA/B撤销屏蔽。

多通道的发送操作同多通道的接收操作类似,由两个16位的移位器XDTD_SHIFTER(以下用S2表示)、X_DCDTD_SHIFTER(以下用S3来表示)来控制,移位器中的数据代表一个数据块中16个连续的通道,其输入信号为XCERA~XCERH,输出信号为S2、S3经过右移操作而输出的S2<0>、S3<0>信号,如图3所示。图3为S2、S3的状态变化流程框图。当串口的发送端处于复位状态时,S2=0FFFFH,S3=0FFFFH。当串口发送端脱离复位状态后,首先判断发送多通道模式是否使能,若XMCM1,XMCM0=00b,多通道模式禁止,发送端为正常情况下发送操作,此时,S2<0>=0,S3<0>=0;若XMCM1,XMCM0!=00b,表示发送多通道模式使能。此时MCR2寄存器中的XCBLK字段的值等于0,同接收端的RCBLK字段相同。XCBLK是一个3位的字段(范围为0~7),表示当前发送的数据在哪个块中。当当前块中16个通道中的所有数据移完以后,XCBLK加1,直至加到7为止,然后清零,依次循环下去。

当串口执行多通道发送操作时,首先进行块0数据的发送(即A区的0~15通道)。若XPABLK!=00b,说明块0数据被屏蔽,发送到DX引脚的数据处于高阻状态,等待块1数据的发送。若XPABLK=00b,说明块0数据可以被发送。接下来判断是否为对称发送操作模式(模式三),如果是对称发送操作,S2=XCERA,S3=RCERA;如果不是对称操作,S2=XCERA,S3=XCERA,当发送移位寄存器XSR发送完一个通道的数据字时,S2、S3相应地右移一位,直至16个通道的数据全部发送完毕。如果移出的数据S2<0>、S3<0>都为1,说明该通道的数据发送到DX引脚有效;如果移出的数据S2<0>、S3<0>不全为1,说明该通道的数据被屏蔽,发送到DX引脚的数据无效,处于高阻状态。XSR移完块0数据后,将进行块1数据的发送操作。此时,接收当前块RCBLK=1,表明接收当前块为B区的块1(即16~31通道)。块1的发送操作同块0的发送操作相同,首先判断块1是否被屏蔽,若屏蔽,等待块2的发送;若没有被屏蔽,则判断是否为对称发送操作,若为对称发送操作,S2=XCERB,S3=RCERB;若不是对称发送操作,S2=XCERB,S3=XCERB。直至块7数据发送完毕为止,S2、S3再从块0开始操作。

4 压缩扩展算法逻辑设计

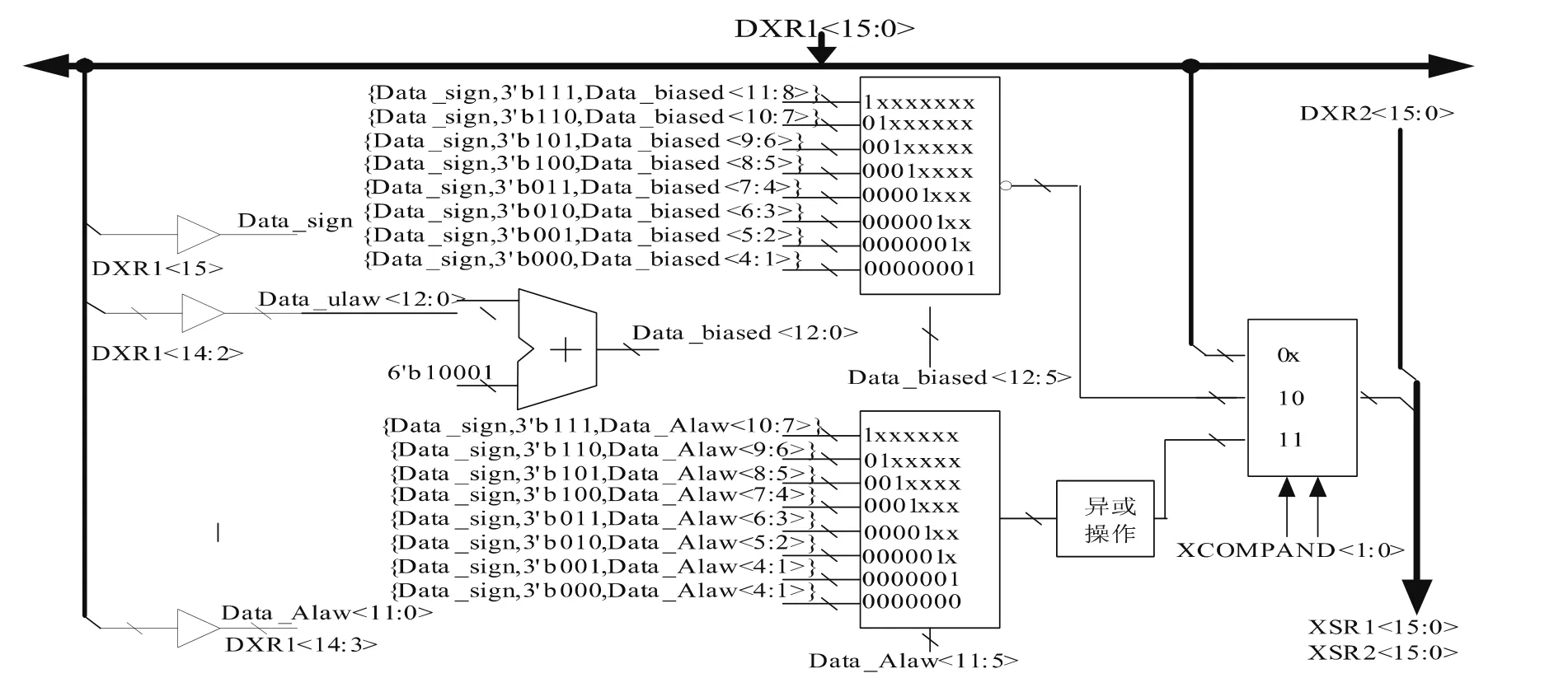

4.1压缩算法逻辑设计

μ律的压缩算法的实现如图4所示。DXR1<15>用作算法中的符号位,DXR1<14:2>用于μ律压缩算法的数据来源。DXR1<14:2>与100001b进行加法运算得到偏置值数据Data_biased<12:0>,根据Data_biased的高8位Data_biased<12:5>的值就可以得到不同的三位段码值(范围0~7)和四位量化值。将符号位、三位段码值和四位量化值进行拼接以后进行取反操作,就得到了μ律压缩后的数据值。因此对于μ律算法的实现只需要一个加法器、一个多路复用器和一次取反操作就可以得到压缩后的数据。

在μ律的压缩算法中,实际进行μ律压缩算法的数据有14位,为DXR<15:2>,而参加A律算法的数据有13位,为DXR<15:3>。如图4所示为A律压缩算法的实现。同μ律压缩算法的实现类似,DXR1<15>用作算法中的符号位,DXR1<14:3>用于A律压缩算法的数据来源Data_Alaw<11:0>,其中,Data_Alaw<11: 5>用于多路复用器的数据控制端,根据Data_Alaw<11:5>就可以得到不同的三位段码值(范围0~7)和四位量化值。将符号位、三位段码值和四位量化值进行拼接以后,为了提高系统的性能,再进行异或操作,就得到了A律压缩后的数据值。同样,对于A律算法的实现只需要一个加法器、一个多路复用器和一次异或操作就可以得到压缩后的数据。

图3 多通道设计流程图

图4 压缩算法实现逻辑

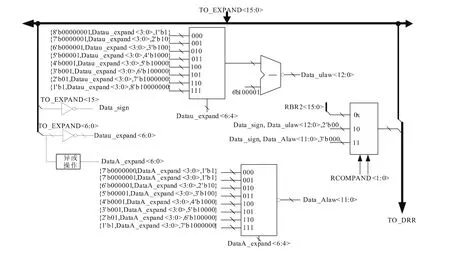

4.2扩展算法逻辑设计

μ律扩展算法的实现如图5所示,在TO_EXPAND<15:0>中,TO_EXPAND<15>取反得到符号位Data_sign,TO_EXPAND<6:0>取反后得到实际进行扩展的数据Datau_expand<6:0>,而TO_EXPAND<14:7>不用于扩展,被忽略掉。Datau_expand<6:0>作为多路复用器的数据控制端,这个多路复用器的输出与100001b进行减法运算便得到了μ律扩展后的结果Data_ulaw<11:0>。

图5的下半部分为A律的扩展逻辑。同μ律扩展的来源相同,A律的扩展来源为TO_EXPAND<15>和TO_EXPAND<6:0>。TO_EXPAND<15>取反得到A律的符号位Data_sign,TO_EXPAND<6:0>经异或操作后得到数据DataA_expand<6:0>。DataA_expand<6: 0>作为多路复用器的数据控制端,这个多路复用器的输出端取反便得到了μ律扩展后的结果Data_Alaw<11:0>。

图5 扩展算法实现逻辑

5 仿真与综合

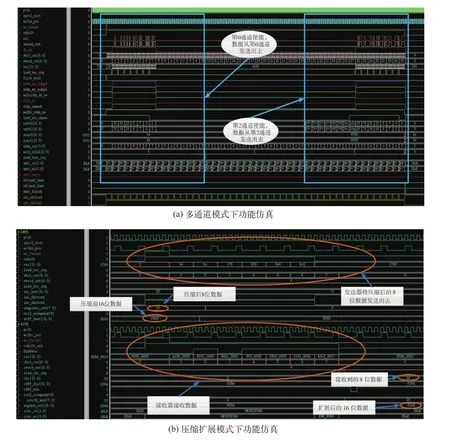

McBSP功能仿真如图6所示。在多通道工作模式下,通过寄存器配置,只将第0通道和第2通道使能,McBSP发送的数据只能通过第0通道和第2通道进行发送。其他通道的从设备都不能接收到数据。在压缩扩展工作模式下,McBSP发送器将需要发送的16位数据,用a律或u律算法压缩成8位再将数据发送出去。McBSP接收器则将接收到8位数据,用a律或u律算法扩展成8位再将数据存放到FIFO中去。

设计采用Synopsys公司的Design Compiler为综合工具,以TSMC 55 nm工艺库在最坏情况下对McBSP进行逻辑综合。当时钟频率为200 MHz时,最长路径延时为7.084 ns,动态功耗为260.9412 μW,漏流功耗为775.3772 nW。

综合和仿真结果表明:整个多通道缓冲串口的设计满足DSP处理器对功耗及路径延时的要求。

6 小结

本文设计了一种多通道缓冲串口,并在标准串口的功能基础上加入了多通道分时复用功能,并且支持a律和u律数据压缩扩展协议,目前该设计已成功应用于某32位高端DSP中。

参考文献:

[1] Simon Srot, SPI master core specification[DB/OL]. http: //www.opencores.org, Rev.0.6, 2007.

[2] Leens F. An introduction to I2C and SPI protocols[J]. IEEEInstrumentation & Measurement Magazine, 2009, 12(1): 8-13.

[3] National Semiconductor Corp. USART IPBrochure[EB/OL]. http://www.ip-extreme.com, 2010.

[4]高腾飞.异步串口通信模块硬IP核的设计与验证[D].成都:电子科技大学,2006.

[5] Patterson D A, Hennessy J L.计算机组成与设计——硬件与软件接口[M].北京:机械工业出版社,2008.

[6] Hennessy J L, Patterson D A.计算机系统结构——量化研究方法[M].北京:电子工业出版社,2004.

图6 功能仿真

杨晓刚(1983—),男,江苏江阴人,硕士,主要研究领域为专用集成电路与系统设计。

The Design and Implementation of a Multichannel Buffered Serial Port

YANG Xiaogang, QIANG Xiaoyan, LIU Taiguang

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214035,China)

Abstract:The paper designed a multichannel buffered serial port(McBSP). In order to accomplish the achievement of time division of multiplexing(TDM), the design added multichannel controlling logic basis of standard serial port. Additionally, compressing and expanding hardware allows compressing and expansion of data in either u-law or a-law format. The serial port has good performance according to the synthesis result and can be widely used in the digital signal processing(DSP)systems.

Keywords:multichannel; serial port; a-law; u-law

作者简介:

收稿日期:2015-11-7

中图分类号:TP302

文献标识码:A

文章编号:1681-1070(2016)03-0031-06