基于DICE结构的SRAM抗辐照加固设计

沈 婧,薛海卫

(中国电子科技集团公司第58研究所,江苏无锡214035)

基于DICE结构的SRAM抗辐照加固设计

沈婧,薛海卫

(中国电子科技集团公司第58研究所,江苏无锡214035)

摘要:存储单元的加固是SRAM加固设计中的一个重要环节。经典DICE单元可以在静态情况下有效地抗单粒子翻转,但是动态情况下抗单粒子翻转能力较差。提出了分离位线的DICE结构,使存储单元在读写状态下具有一定的抗单粒子效应能力。同时,对外围电路中的锁存器采用双模冗余的方法,解决锁存器发生SEU的问题。该设计对SRAM进行了多方位的加固,具有很强的抗单粒子翻转能力。

关键词:SRAM加固;DICE;分离位线;单粒子翻转

1 引言

在外层空间以及核爆等辐射环境中,单粒子效应将引起集成电路本身损坏或存储信息变化,从而导致整个系统崩溃,造成灾难性的后果。随着工艺缩减,单粒子效应对集成电路的损伤在持续增加。近年来,我国航天事业取得了迅速发展,对抗单粒子效应加固的大规模集成电路提出了极大的需求[1]。

存储器作为超大规模集成电路的主要产品,近年来发展非常迅速。目前SRAM不仅是用作计算机高速缓存的最大量挥发性存储器,在航空、通讯、消费类电子产品中也有着十分广泛的应用。因此,在航天航空事业飞速发展的今天,SRAM的抗辐照性能设计显得至关重要。

为了解决单粒子翻转效应,传统的方法是从特殊的辐射工艺线上进行加固。但是,由于这种特殊的工艺线生产流程较复杂,而且辐照产品的需求量极低,使采用工艺加固进行抗辐照设计的研究进展较为迟缓。为了降低工艺的复杂度,同时满足抗辐照性能的要求,电路级抗辐照加固设计的方法得到了快速发展。目前,常用的电路级抗单粒子翻转技术有双互锁存储单元(dual interlocked storagecell,DICE)技术[2~3]、三模冗余技术[4](triple modular redundancy,TMR)等。

本文基于经典DICE结构,提出了一种将位线分离的DICE结构。该结构用于存储单元不仅能在数据保持阶段有效地抗单粒子翻转,也能解决传统DICE结构在数据读写过程中不能抗单粒翻转的问题。外围电路中,综合考虑存储面积的大小以及与分离位线DICE单元使用的兼容性,本文采用锁存器双模冗余的结构来进行加固。

2基于DICE结构的SRAM加固设计

2.1分离位线的DICE结构

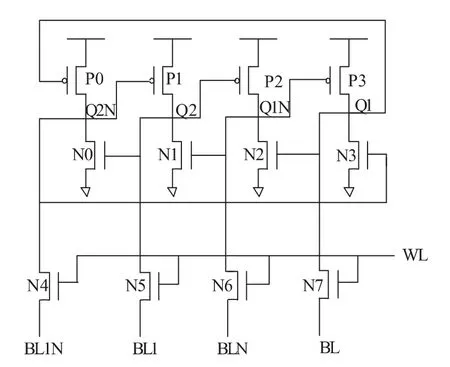

图1所示为经典的基于反馈机制的12管DICE存储单元[5],通过将4个反相器首尾相接,其中存储节点分别与前一级NMOS和后一级PMOS相连接,使得正负存储器数据都被冗余保存,一旦某个存储节点发生单粒子翻转,其连接的节点电压只会影响前一级或者后一级的存储节点,未被影响的那一级会对跳变的存储节点的信息进行恢复。

在数据保持状态中,字线WL关断,4个读写管关断,根据DICE工作原理,若有1个节点发生SEU,可以通过其他3个节点来恢复。在读写过程中,字线打开,4个传输管同时导通,存储单元中的节点Q1、Q2 和Q1N、Q2N将通过位线两两连接在一起。只要其中有1个节点发生翻转,其他3个节点都会通过传输管而发生翻转。综上所述,该结构在读写过程中发生翻转的关键原因在于WL打开使得读写管与位线相连。因此,本文提出了一种分离位线的DICE结构,如图2所示。

图2 位线分离的DICE存储单元结构

分离位线的DICE单元将4根位线各自独立,原来通过位线相连接的N5、N7和N4、N6不再两两连接在一起,形成4条独立的位线BL、BLN、BL1、BL1N,这样,即使读写管同时打开,内部节点也是相互隔离的,因此在读写过程中也能防止发生SEU翻转。

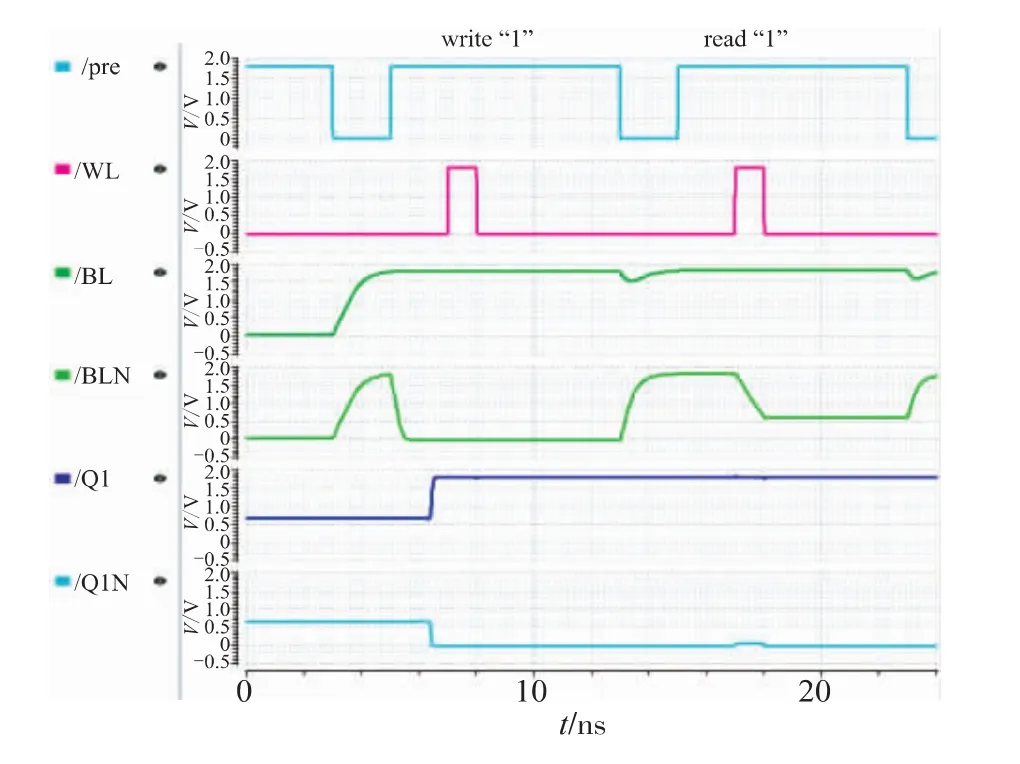

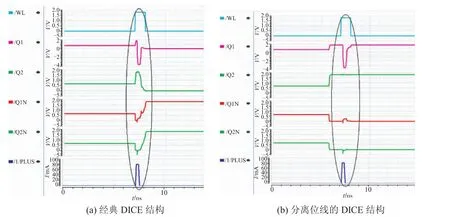

本文采用Cadence Spectre仿真工具,对位线分离的DICE存储单元进行功能仿真,仿真结果如图3所示。

图3 分离位线的DICE单元读写仿真结果

从图中可以看出,该仿真实现了写“1”、读“1”的读写功能,字线“WL”第一个高电平来时,位线“BL”把“1”写到了存储点Q上,而在下一个字线脉冲来时,存储的“1”数据使得位线BLN进行放电。一旦灵敏放大器检测到两条位线上的电压差便输出相应的逻辑值,完成了读“1”操作。同样的原理,写“0”和读“0”也是如此。节点Q1、Q2和Q1N、Q2N两两虽没有相互连接,但由于DICE结构的对称性,它们存储的节点电压是一致的,也就是说BL0、BL0N与BL、BLN的结果是一致的。

2.2双模冗余加固设计

外围电路抗单粒子翻转的加固在SRAM加固设计中也是必不可少的,对锁存器加固一般采用双模冗余或三模冗余的方法,相比而言,双模冗余占用的资源比较少且速度快,但缺点就是如果出错将会输出高阻态,如果不及时进行刷新将导致输出错误。而SRAM中的写入、地址和输出电路中锁存器内容在每一个周期都会进行刷新,因此,选择使用双模冗余进行加固是一个比较好的选择。

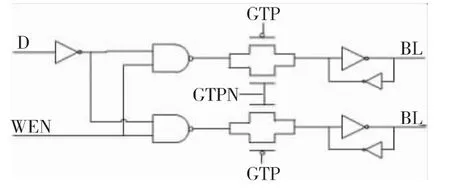

本文以数据写入电路双模冗余设计为例,图4为SRAM传统数据写入电路结构图。D为数据输入端,WEN为写使能信号,D为数据输入信号,当WEN=1时,进行写操作,数据进行锁存后发送到位线BL和BL_。由GTP作为控制信号的传输门和交叉耦合的反相器组成的锁存器,一旦发生SEU,将会导致BL和BL_位线同时放电或者不放电,这样写入的数据将会是一个不定值。

图4 SRAM数据写入电路

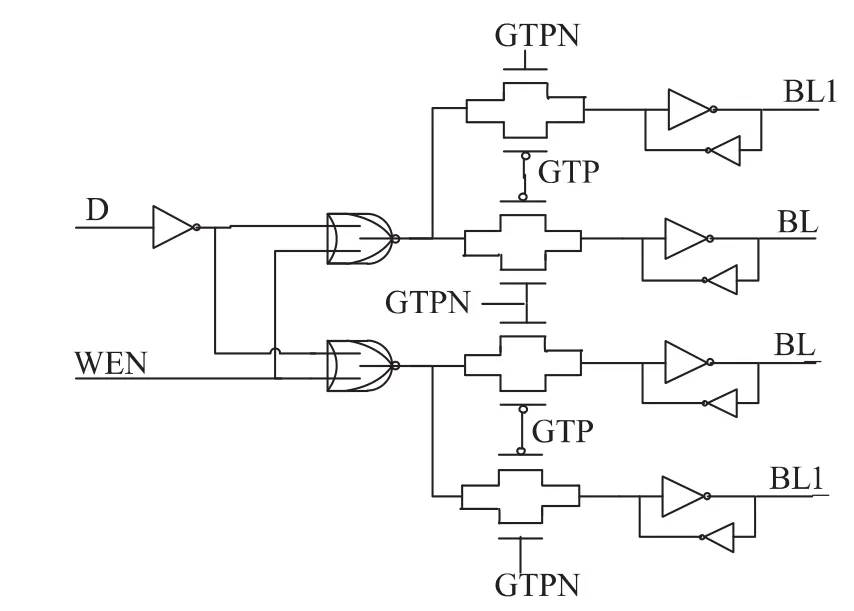

双模冗余加固后的写入电路如图5所示。电路增加了一对存储反相信号的锁存器,这样就产生了BL、BL_、BL1、BL1_共4根位线信号,当其中某一个锁存器发生错误时,其他3个锁存器还能提供正确的信号,结合考虑DICE结构的工作机理,只要有3路信号正确就可以保证写入的数据是正确的。

图5 双模冗余加固的SRAM写入电路

3 单粒子效应模拟仿真

本文采用Cadence的Spectre仿真软件对分离位线的DICE单元以及双模冗余加固的外围电路进行了抗单粒子模拟仿真。在半导体集成电路中,受到单粒子轰击会产生大量的电荷,在电场的作用下形成脉冲电流,通常在仿真中采用向敏感节点注入一定宽度脉冲电流的方法来模拟单粒子轰击[6~7]。

3.1写操作时的单粒子效应模拟

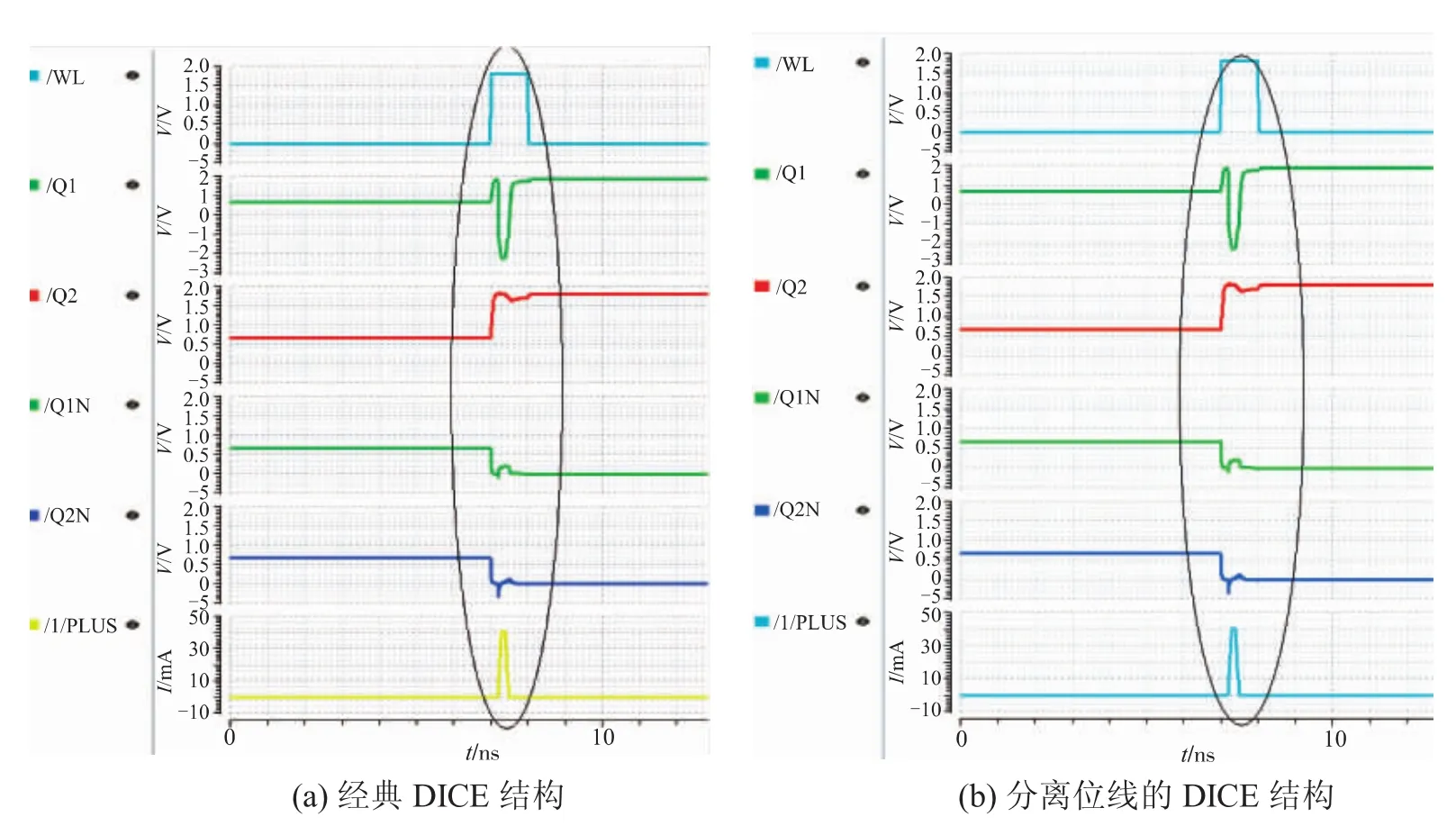

在节点Q1和地之间加一个轰击时间持续100 ps的电流脉冲来进行SEU模拟,假设写操作时对Q1点写入“1”,一旦受到电流轰击,Q1节点将不能进行正常的写操作,节点Q1存储的电荷将迅速放电,最终导致该节点的存储值发生翻转,下面分析了两种DICE结构在不同强度轰击电流下的翻转情况对比。

图6为轰击电流为40 mA时,各个节点的电压变化波形图。由图6(a)和图6(b)可以看出,虽然写“1”过程中Q1节点在电流轰击时发生了翻转,但由于轰击电流较弱,两种DICE单元均在电流轰击结束之后迅速恢复到写“1”状态。

图7为轰击电流增大至80 mA时,各个节点的电压变化波形图。由图7(a)可以看出,Q1节点在进行写“1”操作时受到了单粒子轰击,Q1节点的值立即翻转到“0”,并且在单粒子轰击结束之后也未能恢复,写“1”操作出现错误。图7(b)是分离位线的DICE单元,Q1节点在电流轰击之后迅速恢复到写“1”状态。实验证明了SRAM在读写操作时,分离位线的DICE单元能够有效地抗单粒子翻转。

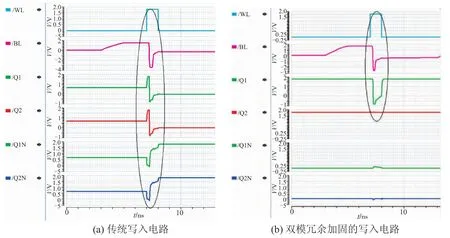

3.2写入电路单粒子效应模拟

图8是分别对传统的数据写入电路和双模冗余加固的数据写入电路在工作过程中发生单粒子效应的模拟波形。写电路在进行写1操作时锁存器受到单粒子轰击,位线BL翻转为0,BL_也为0,传统DICE结构Q1、Q2连接同一根位线,因此节点Q1、Q2的写入状态同时出现错误,两个节点同时翻转,DICE单元将无法恢复,结果如图8(a)所示。而在双模冗余加固电路中,尽管BL翻转导致节点Q1发生错误,但BL1、BL1_和BL_三路位线仍能保证Q2、Q2N、Q1N三个节点的状态正确,在字线关断之后,Q1的状态也能通过DICE的恢复机制恢复到预期值,仿真结果如图8 (b)所示。

图6 I=40 mA、t=100 ps时的波形图

图7 I=80 mA、t=100 ps时的波形图

图8 数据写入电路受轰击时的信号波形

4 结束语

通过对比分析仿真波形,基于分离位线的DICE结构的SRAM存储单元可以实现传统SRAM具备的读写性能。位线分离使得SRAM存储单元在数据保持状态以及数据读写状态时具备有效的抗单粒子翻转特性,外围电路的双模冗余加固结构也为SRAM的抗辐照能力提供了更有力的保障。

参考文献:

[1] K NU DSEN J E, CLARK L T. An area and power efficient radiation hardened by design flip-flop [J]. IEEE Trans Nucl Sci, 2006, 53(6): 3392-3399.

[2] CALIM T, NICOLAIDIS M, VELAZCO R. Upset hardened memory design for submicron CMOS technology [J]. IEEE Transaction on Nuclear Science, 1996, 43(6): 2874-2878.

[3] TIAN H, YANG H Q, MA X, et al. Design of radiation hardened master-slave type flip-flop based on DICE [J]. Microelectronics, 2013, 43(1): 65-69.

[4] HENTSCHKE R, MARQUES F, LINA F, et al. Analyzing area and performance penalty of protecting different digital modules with hamming code d triple modular redundancy [C]. Proceedings of the 15th Conference on Integrated Circuits and Systems Design. Porto Alegre, Brazil, 2002: 95-100.

[5] NOWLIN R N, BEGAY C S, PARKER R R, et al. Radiation hardness of hardened-by-design SRAMs in commercial foundrytechnologies[C].Proceedingsof2006 IEEERadiation EffectsDataWorkshop,PonteVedra,FL,USA,2006.136-143.

[6] Maru A, Shindou S, Ebihara T, et al. DICE based flip-flop with SET pulse discriminator on a 90 nm bulk CMOS process[C]. Nuclear and Space Radiation Effects Conference, 2010. USA: Denver, 2010.

[7]张凌宇,贾宇明,李磊,等.基于DICE结构的抗辐照SRAM设计[J].微电子学,2011,4(1).

沈婧(1988—),女,江苏泰州人,硕士,研究方向为抗辐照SRAM设计。

Design of Radiation Hardened SRAM Based on DICE

SHEN Jing, XUE Haiwei

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214035, China)

Abstract:Cell hardened is an important part in the design of SRAM radiation hardened. The classic DICE unit possesses high efficiency of anti-SEU in the static state of SRAM,but it is incapable of resisting SET in the dynamic state. A separated-bit-line structure is proposed in the paper and this new memory cell has got the ability to immunize Single Event Transient in any working period besides anti-SEU. Furthermore a double module redundancy method is presented to resolve the upset in the peripheral circuits. SRAM with this new structure will get a strong ability of anti-Single Event Effects and high security of data for the multiple aspects of hardening design.

Keywords:SRAM hardening; DICE; separated-bit-line; single event upset

作者简介:

收稿日期:2015-12-9

中图分类号:TN402

文献标识码:A

文章编号:1681-1070(2016)03-0026-05