A律语音压缩编解码器的FPGA实现*

贾瑞莲, 肖沙里, 郭 成, 刘 锋

(重庆大学 光电技术及系统教育部重点实验室,重庆 400030)

A律语音压缩编解码器的FPGA实现*

贾瑞莲, 肖沙里, 郭成, 刘锋

(重庆大学 光电技术及系统教育部重点实验室,重庆 400030)

摘要:阐述了A律13折线非线性量化编/解码算法原理,利用Verilog HDL语言在QuartusII软件平台上给出顶层原理图、仿真结果和编/解码部分的关键代码,编/解码器通过现场可编程门阵列(FPGA)下载验证,实现了语音信号的实时传输;实现的过程中利用逐次比较型算法的特点进行了更好的优化和简化,使应用具有更好的可靠性和实时性。

关键词:A律;FPGA;编码;解码

在信号处理的过程中,一般采取将模拟信号转换为数字信号来进行处理或传输,脉冲编码调制(PCM)是实现模拟信号数字化最基本、最常用的一种方法。脉冲编码调制主要经过3个过程:抽样、量化和编码。抽样是将连续时间的模拟信号转换为离散时间、连续幅度的抽样信号;量化是将抽样信号变为离散时间、离散幅度的数字信号;编码是将量化后的信号编码成为一个二进制码组输出。根据量化间隔选取的不同分为均匀量化和非均匀量化,非均匀量化可以有效地改善信号的量化信噪比。语音信号的量化常采用国际电话电报咨询委员会CCITT建议的对数压扩特性的A律(中国和欧洲)和μ律(北美和日本)压缩的非均匀量化,为便于采用数字电路实现量化,通常采用13折线和15折线近似代替A律和μ律[1]。

所谓A压缩律也就是压缩率具有如下特性的压缩律:

其中,X为归一化压缩器的输入电压;Y为归一化压缩器的输出电压;A为压扩参数,表示压缩成度[2]。

1系统概述

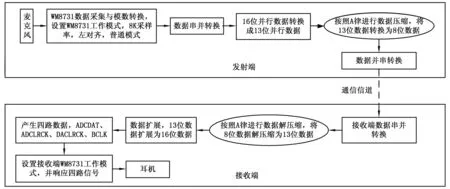

设计的语音通信系统由发射端、通信信道和接收端组成,系统流程图如图1所示。

发射端主要实现语音信号的采集,FPGA开发板内部语音芯片WM8731的配置(8K采样率,左对齐、普通模式),语音数据的串并转换,16-13位语音数据转换,A律语音编码的实现,以及语音数据的并串转换。接收端主要实现语音数据的串并转换,语音数据的解压缩,13-16位数据的转换和WM8731工作所要求的四路信号(ADCDAT、ADCLRCK、DACLRCK、BCLK)的产生以及语音信号的输出。

通信系统使用Altera公司的DE2(EP2C35F672C6)开发板来实现,而DE2开发板的音频输入/输出是由Wolfson公司的低功耗立体声音24位音频编解码芯片WM8731完成。WM8731的音频速率为8~96 kHz可调,提供2线与3线两种与主控制器的接口方式,支持4种音频数据格式,即I2S模式、左对齐模式、右对齐模式和DSP模式[3,4]。采用8 kHz采样率,左对齐、普通模式。

图1 A律语音通信系统流程Fig.1 A-law speech communication system flow

2A律13折线编码原理及FPGA实现

2.1A律13折线编码原理

逐次比较反馈型编码方法对输入样值脉冲进行8位二进制编码。除第一位为极性码外,其他7位二进制码均是通过逐次比较确定的[5]。实现的8位编码码组合如表1,C1为极性码,C2C3C4为段落码,C5C6C7C8为段内码。

表1 A律13折线8位非线性编码码组合

段落码C2C3C4的值是从000-111共8段,其对应的起始电平和段落长度如表2所示:

表2 段落起始电平和长度

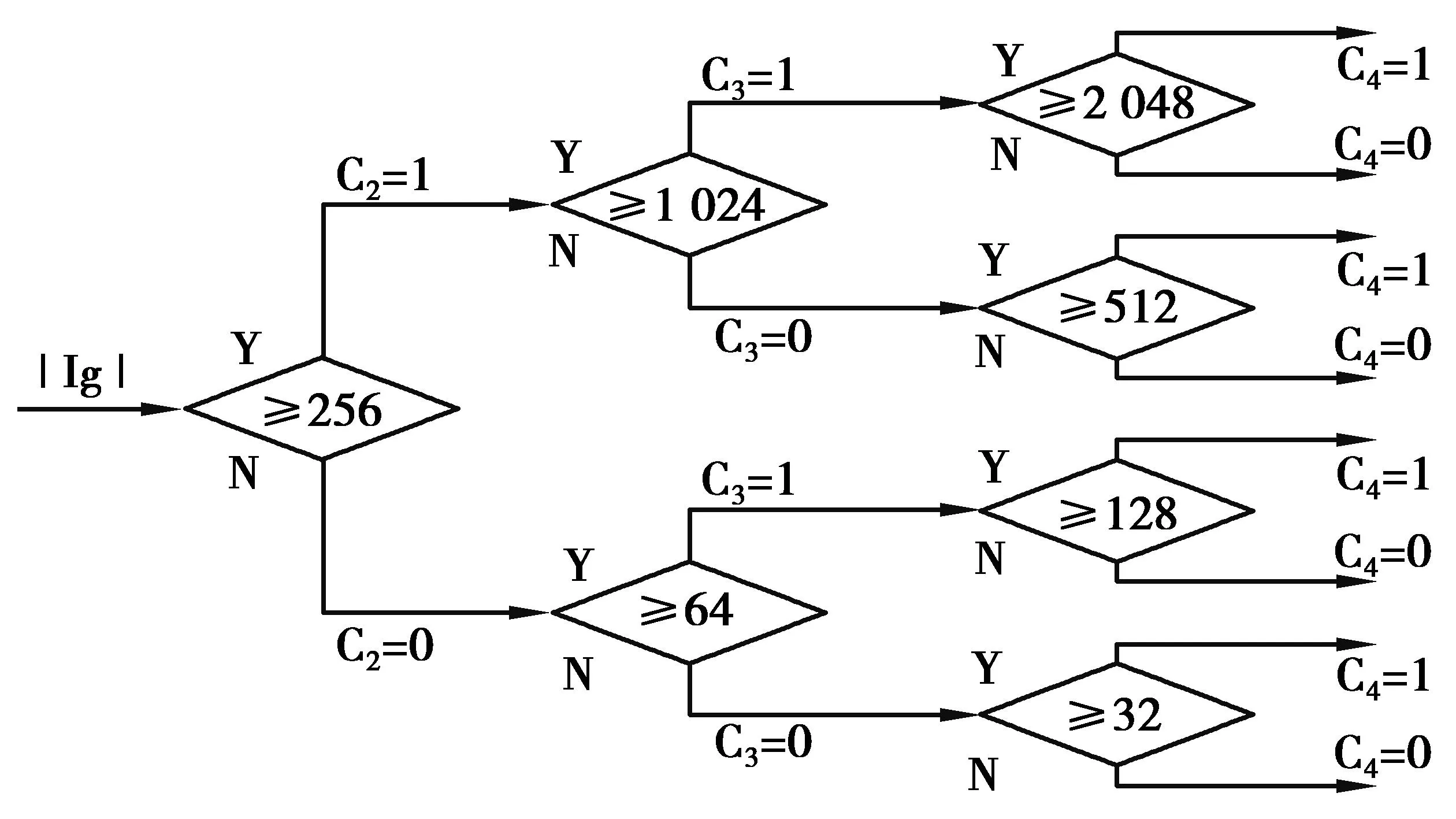

A律13折线量化编码是采用逐次反馈比较型编码器进行编码的,令|Ig|代表信号的幅度,A律13折线逐次反馈型编码方案流程具体如下[6]:

(1) 判断极性码C1的值。若信号为正极性时C1为“0”,反之C1为“1”,如图2所示;

(2) 判断段落码C2C3C4的值。如图3所示,通过比较判断可以得到段落码C2C3C4的值;

图2 信号极性判断Fig.2 Signal pole judgement

图3 段落码编码流程图Fig.3 Paragraph encoding flow chart

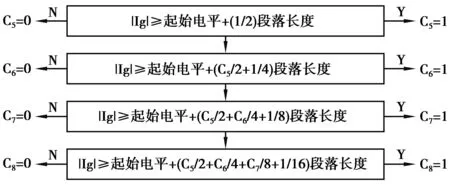

(3) 判断段内码C5C6C7C8的值。对于段内码C5C6C7C8的码值可以通过图4并结合表2来确定。

图4 段内码编码流程图Fig.4 Inside paragraph encoding flow chart

2.2A律13折线编码的FPGA实现

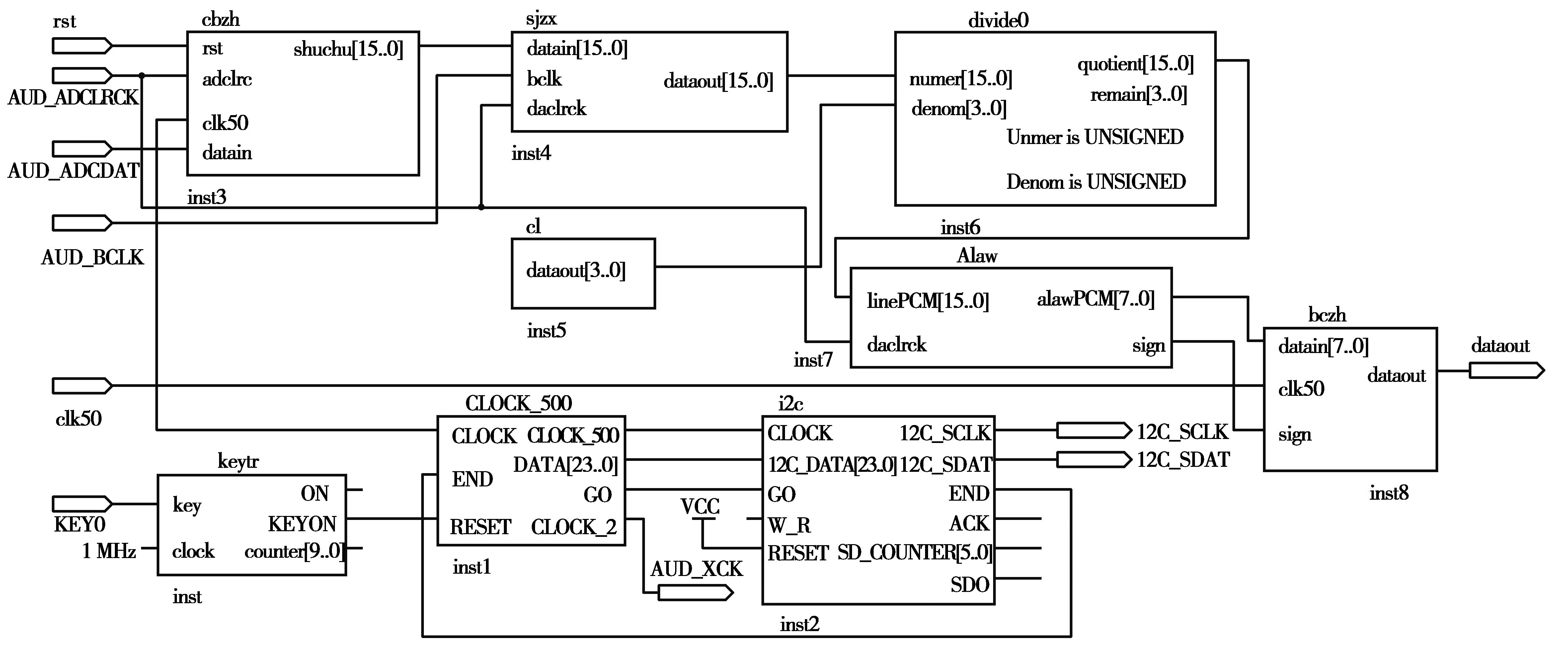

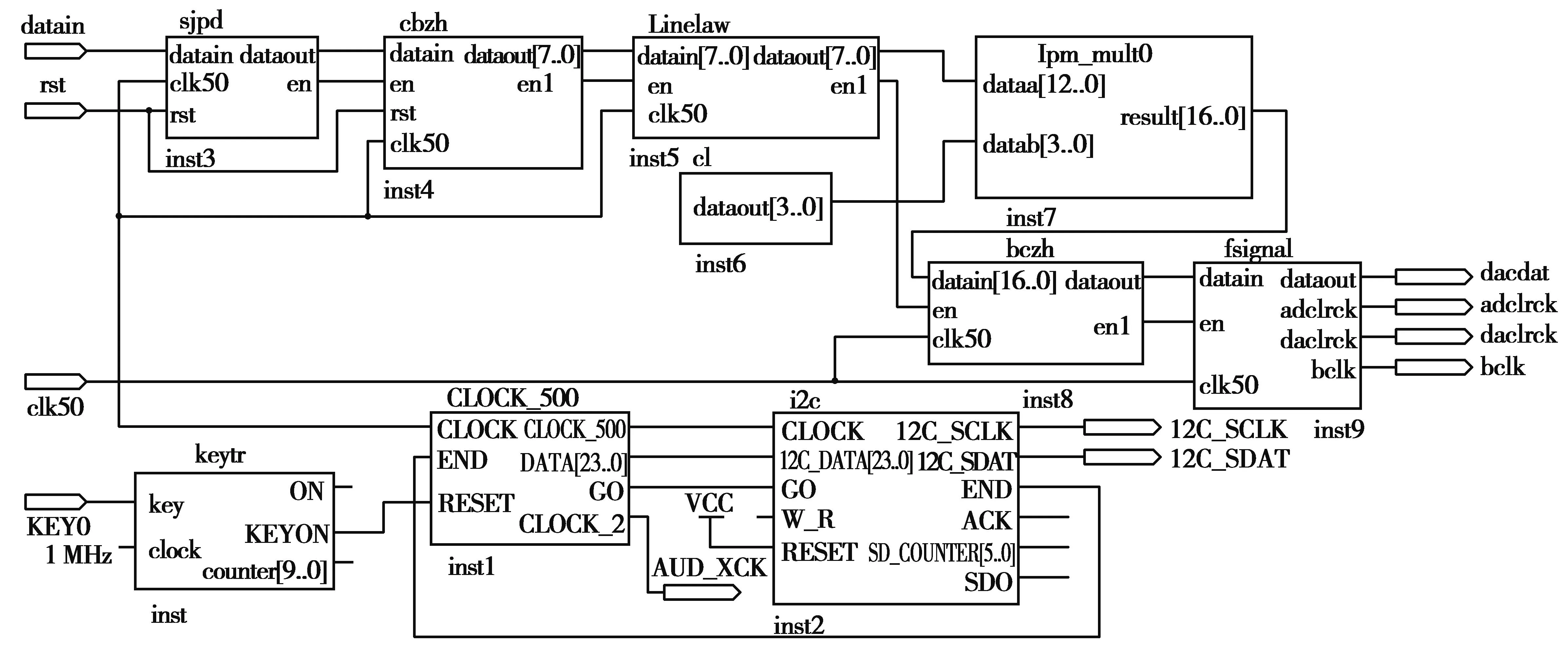

用Verilog HDL语言实现编码器的内部结构如图5所示,编码器的内部结构又可以分为两个部分,一部分为语音芯片WM8731的配置模块,另一部分是A律语音压缩编码模块。语音芯片的配置模块由keytr、CLOCK_500和i2c 3个小模块构成,其中模块keytr是工作时序接口模块,CLOCK_500模块实现时钟分频以产生控制模块i2c的时钟输入,i2c模块为控制字配置模块,控制数据的发送。串并转换模块cbzh,数据整形模块sjzx,常量模块cl,除法器模块divid0,A律编码模块Alaw,并串转换模块bczh一起实现了A律语音数据压缩编码和数据转换。

编码器在各个模块的控制下按照一定时序有规律地完成语音信号的编码。其算法的流程如下:(1) 在WM8731语音芯片音频数字格式的配置下,将到来的语音信号数据首先进行串并转换;(2) 将串并转换后的数据进行16-13位转换;(3) 将13位数据进行A律压缩编码得到8位数据;(4) 将得到的8位数据进行并串转换输出;(5) 跳到(1)循环执行;

图5 A律编码器内部结构图Fig.5 Inner structure chart of A-law encoder

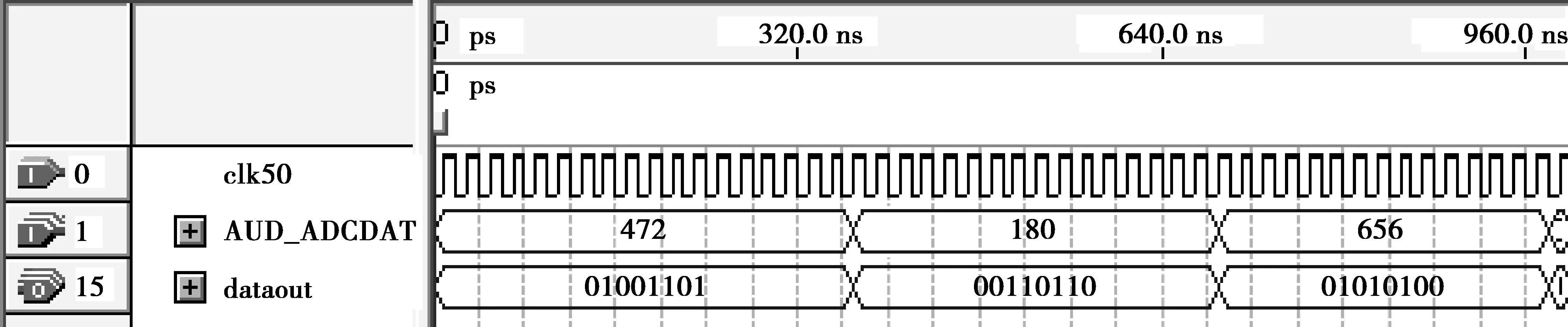

图6 编码器的部分仿真波形Fig.6 Part simulation wave form of the encoder

编码器的部分仿真波形如图6所示:

采用Verilog HDL语言编写程序实现编码和解码过程。在编码过程中,根据语音芯片WM8731的配置要求设置采样率为8 KHz,FPGA工作时钟为50 MHz,数字音频位时钟BCLK为3.125 MHz,FPGA编码输入为语音芯片的16位数据输出AUD_ADCDAT。图6为编码模块的部分仿真图,从图6中看到输入的第一个采样值为正值472,按照上述的编码方法,在第一个时钟上升沿来临后,计算出的八位值为01001101,与仿真结果完全一致。相比文献[6]的仅仅做出A律编解码的理论分析,给出顶层架构设计和仿真分析。

2.3代码

使用Verilog HDL语言实现A律语音编码的部分关键代码(编码部分)如下:

(还有数据要处理)

∥确定符号位

always @(AUD_ADCDAT)

begin

if(AUD_ADCDAT[12]==1′b1)∥输入的是0表示正数,1表示负数

SignBit<=1;

else

SignBit<=0;

end

∥确定段落码

always @(AUD_ADCDAT)

begin

if(AUD_ADCDAT[11:0]>=2048/*>11′h7ff*/)

Seg=3′b111;

else if(AUD_ADCDAT[11:0]>=1024/*>10′h3ff*/)

Seg=3′b110;

else if(AUD_ADCDAT[11:0]>=512/*>9′h1ff*/)

Seg=3′b101;

else if(AUD_ADCDAT[11:0]>=256/*>8′hff*/)

Seg=3′b100;

else if(AUD_ADCDAT[11:0]>=128/*>7′h7f*/)

Seg=3′b011;

else if(AUD_ADCDAT[11:0]>=64/*>6′h3f*/)

Seg=3′b010;

else if(AUD_ADCDAT[11:0]>=32/*>5′h1f*/)

Seg=3′b001;

else

Seg=3′b000;

end

∥确定段内码

always @(AUD_ADCDAT or Seg)

begin

case (Seg)

3′b000:InnerCode=AUD_ADCDAT[4:1];

3′b001:InnerCode=AUD_ADCDAT[4:1];

∥因为要求第一段和第二段的斜率都是16

3′b010:InnerCode=AUD_ADCDAT[5:2];

3′b011:InnerCode=AUD_ADCDAT[6:3];

3′b100:InnerCode=AUD_ADCDAT[7:4];

3′b101:InnerCode=AUD_ADCDAT[8:5];

3′b110:InnerCode=AUD_ADCDAT[9:6];

3′b111:InnerCode=AUD_ADCDAT[10:7];

default:InnerCode=4′b0000;

endcase

end∥输出

always @(clk50)

begin

dataout={SignBit,Seg[2:0],InnerCode[3:0]};

end

3A律13折线解码器原理及其FPGA实现

3.1A律13折线解码器原理

解码是编码的逆过程,也即是在接收端将接收到的信号经解码后音频输出。A律13折线解码器解码流程如下:

(1) 首先根据C1判断信号的极性,若C1为0则信号为正极性,反之为负极性;

(2) 根据段落码C2C3C4的码值,再结合表2确定段落的起始电平;

3.2A律13折线解码器的FPGA实现

用Verilog HDL语言实现的解码器内部结构如图6所示,与编码器一样解码器的内部结构也可以分为两个部分,一部分为语音芯片WM8731的配置模块,另一部分是A律语音解码模块。语音芯片的配置模块由keytr、CLOCK_500和i2c 3个小模块构成,其中模块keytr是工作时序接口模块,CLOCK_500模块实现时钟分频以产生控制模块i2c的时钟输入,i2c模块为控制字配置模块,控制数据的接收。数据判断模块sjpd,串并转换模块cbzh,A律解码模块Linelaw,常量模块cl,乘法器模块Ipm_mult0,并串转换bczh模块,产生WM8731工作的四路信号模块fsignal一起实现语音信号的解码以及数据转换。

解码器是在各模块的控制下按照一定的时序有规律地完成语音信号的解码。解码算法的流程如下:

(1) 在WM8731语音信号音频数字格式的配置下,首先进行数据的判断,当有数据到来时进行串并转换;(2) 将得到的并行信号进行A律解码,也即是将8-13位数据解码;(3) 将解码后的数据进行13-16位扩展;(4) 将得到的16位数据输入到语音芯片,实现语音型号的还原;(5) 跳到(1)循环执行;

图7 解器内部结构图Fig.7 Inside structure chart of the decoder

图8 解码器的部分仿真波形Fig.8 Part simulation wave form of the decoder

解码器的部分仿真波形如图7所示:按照图1的编码原理和Quartusll编写的解码程序得到解码的部分仿真波形。从仿真图7中看到在第一个时钟上升沿到来时的解码值为01001101,也即是图6的第一个编码值,按照上述的解码方法计算得到的值是472,这与仿真结果完全一致。相比于文献[2]和[5]仅仅阐述编码的设计与实现,做出了解码器的原理分析和仿真实现。

3.3代码

使用Verilog HDL语言实现A律语音解码的部分关键代码(解码部分)如下:

(还有数据要处理)

∥确定段落码

always @(clk50)

begin

Seg<=datain[6:4];

dacdat<=out;

end

always @ (clk50)

begin

case(Seg)

3′b000:out[12:0]<={datain[7],7′b0,datain[3:0],1′b1};

3′b001:out[12:0]<={datain[7],6′b0,1′b1,datain[3:0],1′b1};

3′b010:out[12:0]<={datain[7],5′b0,1′b1,datain[3:0],1′b1,1′b0};

3′b011:out[12:0]<={datain[7],4′b0,1′b1,datain[3:0],1′b1,2′b0};

3′b100:out[12:0]<={datain[7],3′b0,1′b1,datain[3:0],1′b1,3′b0};

3′b101:out[12:0]<={datain[7],2′b0,1′b1,datain[3:0],1′b1,4′b0};

3′b110:out[12:0]<={datain[7],1′b0,1′b1,datain[3:0],1′b1,5′b0};

3′b111:out[12:0]<={datain[7],1′b1,datain[3:0],1′b1,6′b0};

default:dacdat[12:0]<=12′b0;

endcase

end

4结论

采用Verilog HDL语言利用逐次反馈比较型算法在QuartusII软件平台上实现了A律语音数据的编解码算法,并通过FPGA的下载验证。给出了算法的顶层架构设计和仿真是分析,以及编/解码部分的关键代码,这相对参考文献[2][5]和[6]都有了很大的提高和补充,这为进一步研究语音通信编解码算法及实现提供了指导。

参考文献(References):

[1]吴家安.现代语音编码技术[M].北京:科学出版社,2008

WU J A.Modern Speech Coding Technology[M].Science Press,2008

[2] 李春泉,李敬群.基于FPGA快速A律压缩编码的设计与实现[J].现场总线技术应用200例,2008,24(6):214-216

LI C Q,LI J Q.The Design and Implementation of Speed A Law Compressed Encoding Based on FPGA[J].200 Cases of Field bus Technology.2008,24(6):214-216

[3] 张志刚.FPGA与SOPC设计教程—DE2实践[M].西安:西安电子科技大学,2007

ZHANG Z G.FPGA and SOPC Technology DE2 Practice[M].XiDian University,2007

[4] 易星,肖沙里.基于紫外激光器的无线光通信系统[J].重庆工商大学学报(自然科学版),2014(7):46

YI X,XIAO S L.Wireless Communication System Based on UV Laser[J].Journal of Chongqing Technology and Business University:Natural Science Edition,2014(7):46

[5] 刘全金.一种A律PCM编码的简化方法[J].安庆师范学院学报,2007(11):34

LIU Q J.A Simplify Method of A- law PCM Encoding[J].Journal of Anqing Teachers College (Natural Science Edition ),2007(11):34

[6] 张海琼.浅论A律13折线非线性编译码[J].科技文汇,2008(11):283

ZHANG H Q.On the Encode and Decode of A Law 13 Segments[J].The Science Education Article Collects,2008(11):283

责任编辑:田静

FPGA Implementation of A-law Speech Compression Encoder and Decoder

JIA Rui-lian, XIAO Sha-li, GUO Cheng, LIU Feng

(Key Laboratory of Optoelectronic Technology and System of Education Ministry of China,Chongqing University,Chongqing 400030,China)

Abstract:This paper expounds the principle of the A-law 13-segment nonlinear quantization encoding/decoding algorithm.The top floor principle diagram,simulation result and the key code of encoding/decoding part are given by using Verilog HDL language on QuartusII software platform,and the encoder/decoder can be downloaded and tested via field programmable gate array(FPGA)so that real-time speech signal transmission is implemented.The implementing process is better optimized and simplified based on the characteristics of successive approximation type algorithm so that its application has better reliability and timeliness.

Key words:A-law; FPGA; encode; decode

中图分类号:TP321

文献标志码:A

文章编号:1672-058X(2016)01-0059-06

作者简介:贾瑞莲(1989-),女,河南商丘人,硕士研究生,从事语音通信研究.

*基金项目:国家自然科学基金项目(11075226);中央高校基金(CDJZR10120009)资助课题.

收稿日期:2015-06-13;修回日期:2015-09-08.

doi:10.16055/j.issn.1672-058X.2016.0001.013