高速时钟驱动电路的优化设计

曲 明,高 欣,王鑫华

(1.中国电子科技集团公司第五十四研究所,河北 石家庄050081;

2.中国人民解放军63916部队,北京 100089)

高速时钟驱动电路的优化设计

曲明1,高欣2,王鑫华1

(1.中国电子科技集团公司第五十四研究所,河北 石家庄050081;

2.中国人民解放军63916部队,北京 100089)

摘要:随着系统电路工作频率的不断提高,在应用中对系统互连和电路间的时钟传输提出了更高的要求。提出了一款基于LVDS(低压差分信号)接口的时钟分路驱动电路,该电路可输出四路时钟信号,工作频率在2 GHz以下,电路采用了0.13μm CMOS工艺,电源电压为3.3 V,内部集成了LDO电路。主要阐述了如何通过内部预加重电路,共模电压稳定电路,占空比调整电路等模块来优化电路的性能,并配合仿真进行了相关的分析。

关键词:LVDS;预加重电路;占空比调整;共模电压稳定

0引言

目前,CMOS工艺技术已经使芯片内的时钟频率和微处理器的速度达到了上GHz,然而由于受到电路以及传输线的限制,普通I/O接口电路仅能工作在几百MHz级,因此,I/O 接口电路限制了当前高速低功耗时钟驱动电路间的连接应用和发展[1,2]。LVDS(Low Voltage Differential Signaling)传输技术这种高速低功耗接口标准为解决这一瓶颈问题提供了可能[3]。但是,由于传输过程中,会受到传输距离、外界环境以及制造工艺偏差的影响,高速的数据信号易出现干扰和失真,因此,需要对传统的LVDS 驱动电路进行优化[4]。

1高速时钟驱动电路结构

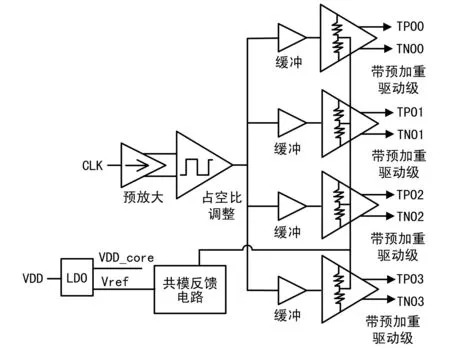

本文将从预加重电路、占空比调整电路和共模稳压电路3个方面对高速时钟驱动电路中LVDS模块性能进行优化。其中,预加重电路能够增大输出信号的电平反转能力,增大了高频信号的输出能力[5]。占空比调整电路不仅能保证输出信号占空比1∶1的平衡,还能保证信号的完整性。共模稳压电路能够保证输出信号的共模电平动态稳定在接口所需的电压值上,便于后级电路的接收[6,7]。高速时钟驱动电路整体架构如图1所示。

图1 高速时钟驱动电路架构

2预加重电路的分析和仿真

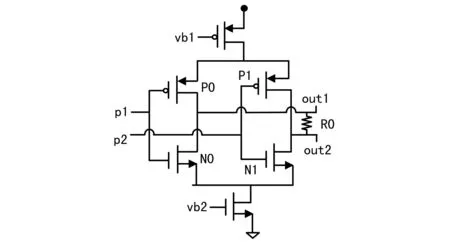

预加重电路能够实现传输信号高频部分的放大,加快信号高低电平的建立时间,降低码间干扰,提高了LVDS驱动电路的传输速率[8],因此预加重电路成为了LVDS设计的一个重点。普通驱动级和带预加重电路的驱动级如图2和图3所示。

图2 普通驱动级

图3 带预加重的驱动级

普通驱动级电路是通过差分信号p1和p2控制4个MOS管的导通,来改变电流流过R0的方向,从而在输出端out1、out2产生高低电平。当信号的传输速率很高时,图2 的输出信号很容易受到干扰,而且需要较大的功耗做补偿。

带预加重的驱动级电路如图3所示,控制信号线pl、p2比plb、p2b延迟一定时间,当p1、p2信号还未到达稳定电平1或0时,p1b、p2b已提前一定时间建立到1或0电平,使得通过R0的电流I(t)由图3中左侧驱动级电路产生的电流I1和右侧预加重级产生的电流I2组成,但方向相反,此时I(t)=I1-I2;当p1、p2信号达到稳定电平1或0时,p1b、p2b仍处在1或0电平,此时流过R0的电流方向相同,I(t)=I1+I2。由此可见,信号在反转时刻,驱动电流得到了加强,实现了预加重的功能。普通驱动级和带预加重的驱动级输出波形如图4和图5所示。

图4 普通驱动级输出波形 图5 带预加重的驱动级输出波形

由此可见,预加重电路在信号发生变化时,能更快地上升到最大电压,而且高出的瞬间高电压能很好地抑止噪音,并且能够克服信号在变化时的突变。预加重电压越大,信号传输的距离将会越长。因此,带预加重的驱动级与普通驱动级电路相比具有较好的抗干扰能力[9]。

3占空比调整电路分析和仿真

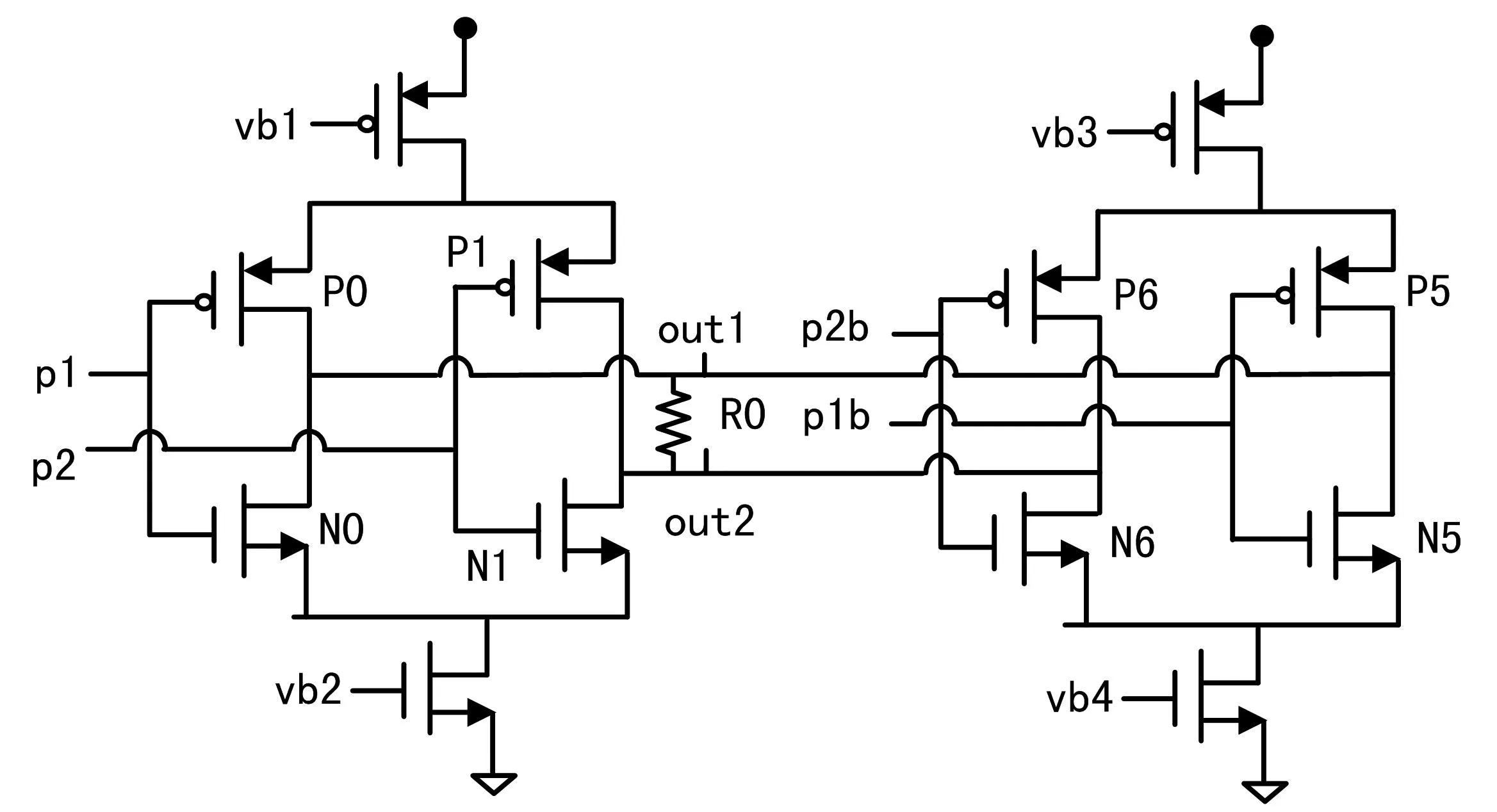

在高频信号输入的过程中,即使在输入端口匹配较好的情况下,芯片加工时的工艺偏差,会导致输入时钟信号到达驱动级控制端时发生占空比的偏移,从而导致,一个周期内,高电平或低电平信号不能充分地建立,降低了信号的质量,甚至无法被后级电路识别[10]。而占空比调整电路,能够自动将占空比调整为1∶1,工作原理如图6所示。

图6 占空比调整电路工作原理

普通的接收级,仅是由图6中虚线框中部分的运放作为比较器,将差分信号接收进来,产生时钟信号,而改进的电路增加了检测和反馈环路,首先从INV1后的A点将信号采出,经过低通滤波器,得到A点信号的直流信号,然后送到检测电路OP中,与参考电压Vref进行比较,若反馈电压高于Vref,则降低VO1和VO2的电压,增大VBO的电压;若反馈电压低于Vref,则增大VO1和VO2的电压,减小VBO的电压。最终通过短暂的调整过程,反馈电压与Vref电压相等,输出时钟的占空比近似为1∶1。

在对A点信号进行滤波采样时,最低工作频率的信号,经过滤波采样后应该衰减60 dB左右。该时钟驱动电路应用在50 MHz~2 GHz的频率范围,因此对低通滤波采样电路进行AC特性仿真,衰减3 dB时,带宽在1 MHz左右,可以满足使用要求。

由于该检测调整系统是负反馈系统,需要对该系统的相位裕度和环路增益进行仿真,相位裕度的仿真是用来保证系统的稳定性,一般要求相位裕度在60°以上[11];环路增益的仿真是保证系统的精度,根据设计指标要求,可以偏差20 mV以内,由此计算环路增益应在50 dB以上。根据使用要求,将系统的稳定时间设定在2 μs以内,根据通过式(1)计算可以得到:

稳定时间=3.5/GBW,

(1)

式中,GBW为反馈系统的单位增益带宽积,设计单位增益带宽积>1.75 MHz。

在典型情况和4个极端工艺角下,进行波特仿真,相位裕度均在73.8°以上,环路增益在50 dB以上,GBW在2.9 MHz以上,能够满足设计要求。

此外,对该电路进行瞬态仿真,仿真波形如图7所示。

图7 输出时钟信号的变化

由图7可看到,刚输出的时钟信号占空比较差,高电平和低电平大概在1∶2,由于占空比调整电路的作用,占空比最终近似为1∶1,由于是负反馈调整电路,无论是工艺偏差的影响,还是外界环境的变化,占空比调整电路都能将输出占空比稳定在1∶1。

4共模反馈电路分析和仿真

根据不同LVDS的应用,为和后级接收电路匹配,需要将输出的共模电平固定在稳定电压上。本电路设计将固定电平稳定在612 mV左右。

由于芯片外界的噪声以及工作中外界环境的变化,很容易导致在信号传输过程中共模电平的偏移和波动,而且器件的失配也会造成共模电平的偏移[12]。而接收器对共模电平的变化是相当敏感的,这将直接导致接收器性能上的波动,最重要的是共模电平是不可能通过差动反馈来达到稳定[13]。因此,就要求加入共模反馈电路来稳定输出共模电平。共模反馈电路的工作大致可以分为3个步骤:① 共模电平的检测;② 共模电平与参考电平进行比较;③ 将比较的误差送回驱动器的偏置运放中。

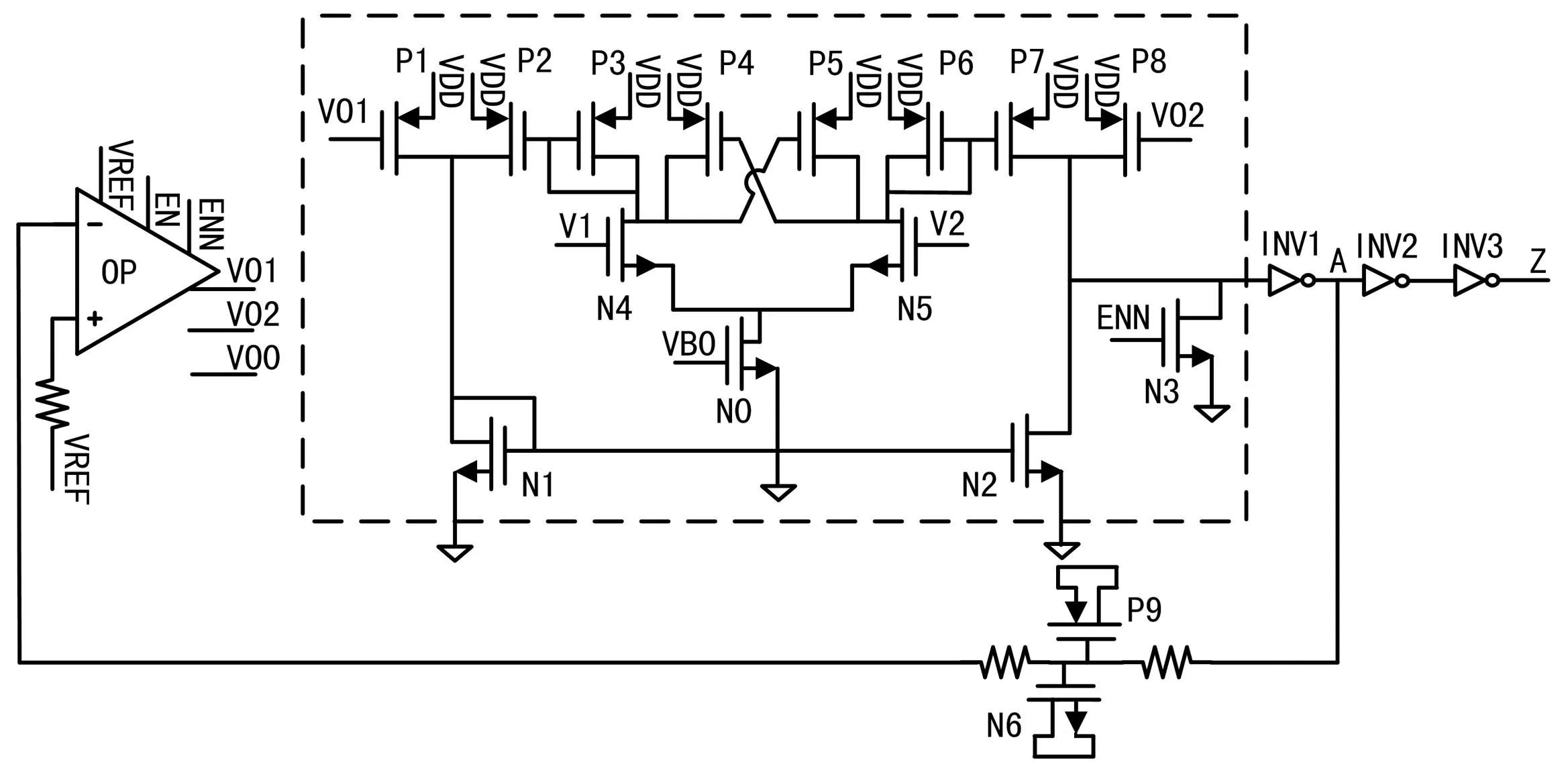

比较通用的共模反馈电路如图8所示,在输出端间接2个阻值相同的电阻R0和R1,通过电阻分压来实现共模电平的检测。将检测电压送入五管运放的负端,共模参考电压vref送入运放的正端,二者进行比较,将结果通过偏置电路送给驱动器的P5管和N6管,从而调整输出的共模电压。但是这种方法在实际应用中存在很大的弊端。电阻R0、Rl是端接在发送器两输出线上的,而发送器发送的是差分信号,如此则要求这2个电阻有非常大的阻值才能避免开环增益的降低。2个大的电阻将不可避免地占去非常大的面积,增加了系统成本,而且电阻越大越多,增加了匹配的难度,会使失配的概率增大,最终会导致输出共模电压偏移出设计范围。

图8 通用共模反馈电路

为了避免图8结构带来的设计弊端,采用了一种无电阻结构的反馈电路,如图9所示。该结构中尾电流管N2、N3镜像N13管的电流,限制住共模反馈主体电路。主体电路由N4、N5、N6、N7 4个MOS管构成。N4、N7的栅极接发送器的差分输出,N5、N6的栅极接基准电压输出。当共模电平偏高的时候,N7、N4管的栅电压高于正常值,通过这两管的电流增加。但是由于尾电流管N2、N3的作用,共模反馈主体电路的电流恒定,所以通过N5、N6管的电流减小。该效果通过电流镜传递给电流模主体电路的首尾电流管P0、N0,其减小了主体电路的工作电流,从而降低输出共模电平。同理,当共模电平偏高的时候,通过N5、N6管的电流增大,通过镜像,从而增大了主体电路的工作电流,进而提高共模电平,最终实现了共模反馈。由图4和图5可以看出,最终输出的共模电平能够稳定在600 mV附近。

图9 无电阻结构

5芯片整体输出仿真

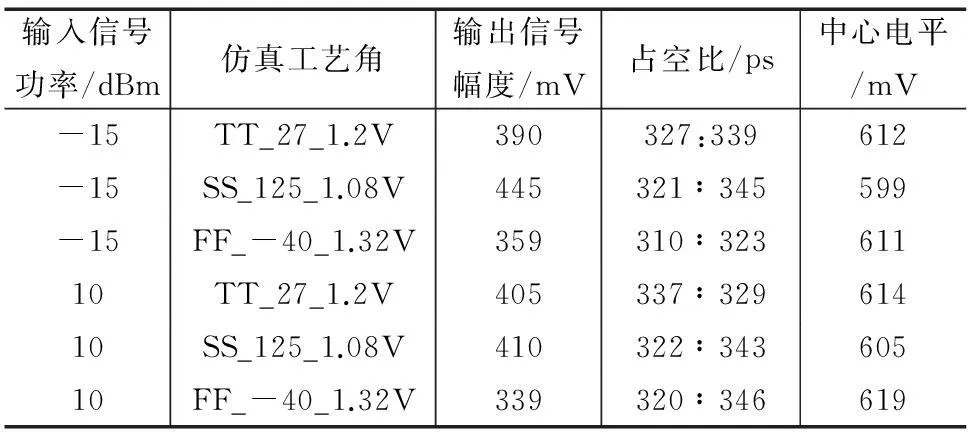

在完成预加重电路,占空比调整电路以及共模反馈电路的优化后,并对版图进行充分匹配优化设计,然后,对版图进行寄生参数的提取,在极端工艺角下,负载13 pF电容,对整体电路进行后仿真,进行充分的验证,仿真结果如表1所示,仿真波形如图10所示。

表1 2 GHz输入信号的后仿真结果

图10 仿真波形

从各个工艺角下的仿真结果和测试结果可以看出,输出平均幅值在350 mV左右,说明预加重电路能够在高频时,保证了输出的建立幅度;占空比近似1∶1,说明占空比调整电路对占空比进行了动态调整;中心电平近似在600 mV左右,说明共模反馈电路将够将共模稳定电路稳定在设计值上。

6结束语

在对时钟驱动电路的设计中,对预加重电路、占空比调整电路和共模反馈电路进行了优化,仿真结果表明,电路能够保证占空比稳定在1∶1左右,输出共模电平稳定在0.6 V左右,适应高频传输要求,具有较好的抗干扰能力。

参考文献

[1]李宏儒,刘亮.并行转串行LVDS长线接口设计[J].实验室研究与探索,2010,29(6):62-65.

[2]刘祥远,陈书明.LVDS高速I/O接口单元的设计研究[J].计算机工程与科学,2001,23(4):52-56.

[3]Allen P E,Holberg D R.CMOS模拟集成电路设计[M].北京:电子工业出版社,2005.

[4]YANG Cui-hong,WEN Feng,YAO Zong.Design of Long-distance High-speed Serial Data Transmission System Based on LVDS[J].Communications Technology,2010,43(09):59-64.

[5]Byun J,Lee H Y.Analysis and Improvement of Electromagnetic Susceptibility on High Speed LVDS I/O System[C]//Microwave Conference Proceeding(APMC),2010 Asia-Pacific,2010:175-178.

[6]LVDS Application and Data Handbook[R].Texas Instruments.SLLD009,2002.

[7]Sansen W M C.模拟集成电路设计精粹[M].陈莹梅,译.北京:清华大学出版社,2008.

[8]Rafal K.The Design of Low Power 11.6mW High Speed 1.8Gb/s Stand-alone LVDS Drive in 0.18-μm CMOS,Mixed Design of Integrated Circuit and Systems(MIXDES)[C]//2010 Proceedings of the 17th International Conference,2010:337-342.

[9]拉扎维.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2008.

[10]邹振杰,陈明辉,曲明.一种4 bit相位量化ADC电路分析[J].无线电通信技术,2011,37(6):40-42,49.

[11]李斌,田素雷,孙雪晶.大点数FFT设计中提高资源利用率的方法[J].无线电工程,2011,41(1):54-57.

[12]魏瑞刚,孙学士.高速LDPC码译码器的实现技术分析[J].无线电工程,2011,41(9):28-30.

[13]许仕龙,李斌,李哲,等.高灵敏度GPS导航算法分析[J].无线电工程,2011,41(10):37-39.

Design Optimization of High-speed Clock Drive Circuit

QU Ming1,GAO Xin2,WANG Xin-hua1

(1.The 54th Research Institute of CETC,Shijiazhuang Hebei 050081,China;2.Unit 63916,PLA,Beijing 100089,China)

Abstract:Owing to the increasing high frequency of circuit systems,it is required to improve the performance of clock signal transmission,applying to system interconnection and circuit.The paper presents a multi-channel clock drive module,based on Low-Voltage Differential Signaling(LVDS)interface.Having four clock signal outputs,the LVDS interface is designed in 0.13 μm CMOS process and is supplied in 3.3V supply source.It works in highest frequency of 2GHz and consists an inter LDO module.Also,this paper presents how to optimize circuit features,using internal pre-emphasis module,common mode stabilizer and duty cycle corrector.Finally,analysis is put forward in virtue of simulation.

Key words:LVDS;Pre-emphasis Module;Common Mode Stabilizer;Duty Cycle Corrector

中图分类号:TN108.7

文献标识码:A

文章编号:1003-3114(2016)02-80-4

作者简介:曲明(1982—),男,工程师,主要研究方向:模拟集成电路设计。高欣(1987—),女,助理工程师,主要研究方向:射频通信集成电路设计。

收稿日期:2015-11-11

doi:10.3969/j.issn.1003-3114.2016.02.21

引用格式:曲明,高欣,王鑫华.高速时钟驱动电路的优化设计[J].无线电通信技术,2016,42(2):80-83.